Desainer memiliki banyak cara untuk membedakan solusi RISC-V. Satu jalur diluncurkan ke berbagai penyesuaian dan ekstensi inti RISC-V sesuai spesifikasi. Fokus lainnya adalah memilih dan merakit blok IP dalam desain system-on-chip (SoC) lengkap di sekitar satu atau lebih inti RISC-V. Yang ketiga sedang muncul: menghubungkan inti RISC-V dan blok IP lainnya dengan network-on-chip (NoC) alih-alih struktur bus sederhana. Dan ini bukan hanya pada level tinggi – memasangkan inti RISC-V dengan NoC menjawab banyak tantangan desain SoC di mana data harus mengalir secara efisien dalam beban kerja apa pun menggunakan protokol on-chip apa pun.

Tingkat kinerja berubah dengan skema interkoneksi tingkat lanjut

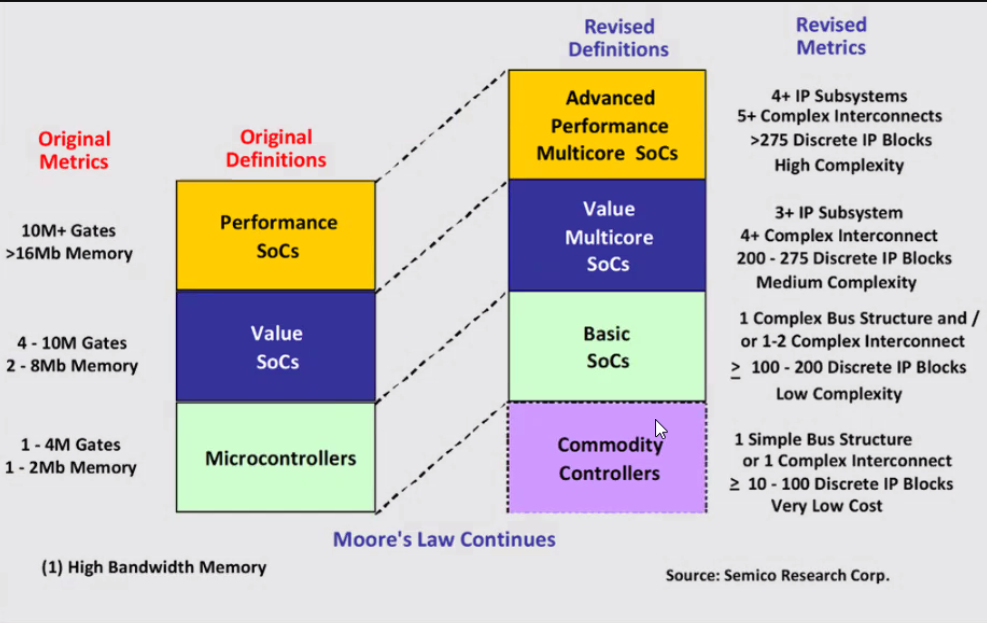

Menghitung gerbang, inti, dan blok periferal saja tidak lagi menggambarkan potensi kinerja desain SoC. Skema interkoneksi kini menentukan batas antara tingkat kinerja SoC, menurut Semico Research, dan tingkat baru telah terbuka di mana interkoneksi berubah dari struktur bus sederhana menjadi skema yang lebih canggih.

Definisi Semico yang diperbarui mengakui tiga kekuatan yang bekerja: desain multicore yang mudah meresap, standar yang lebih tinggi untuk apa yang dianggap sebagai desain yang kompleks, dan garis kabur antara “mikrokontroler” dan “SoC.” Dalam pandangan terbaru Semico, gagasan jumlah gerbang sebagai metrik menghilang karena satu inti prosesor modern dapat menyeret banyak gerbang bersamanya. Kompleksitas menjadi fungsi interkoneksi, bervariasi menurut subsistem dan blok IP yang beragam.

Tingkat kinerja SoC, gambar milik Semico Research Corp.

Jika bus sederhana dapat digunakan, kemungkinan merupakan bagian dengan inti prosesor tunggal dan periferal siklus tugas rendah yang tidak terus-menerus bersaing untuk mendapatkan bus, Semico melihat tingkat pengontrol komoditas. Apa pun di atas itu akan menjadi SoC, mungkin dengan setidaknya beberapa periferal yang berjuang untuk mendapatkan bandwidth on-chip dan perhatian dari inti prosesor. Tingkat SoC yang lebih tinggi memiliki banyak inti dan beberapa subsistem IP, masing-masing dengan teknologi interkoneksi yang disesuaikan.

NoC mengambil lebih banyak protokol dan subsistem

RISC-V dengan cepat meningkatkan tingkat kinerja ini seiring dengan munculnya core yang lebih kuat, dengan penerapan yang sama pada skala Semico kelas bawah. Namun, perancang RISC-V mungkin memiliki lebih sedikit pengalaman dalam skema interkoneksi kompleks yang terlihat pada tingkat yang lebih tinggi. “TileLink mungkin merupakan pemikiran pertama untuk interkoneksi RISC-V, namun mungkin sulit digunakan dalam skenario yang lebih kompleks,” kata Frank Schirrmeister, VP Solusi dan Pengembangan Bisnis untuk Arteris.

Kekuatan super NoC adalah kemampuannya untuk menghubungkan subsistem menggunakan protokol yang berbeda, dan perancang SoC kemungkinan besar akan menjalankan beberapa protokol dengan kompleksitas sedang. AXI menyamakan kedudukan untuk koneksi blok IP sederhana. Solusi multicore dengan blok pemrosesan bersama memerlukan koherensi cache, sehingga memunculkan protokol CHI. Berbagi memori I/O membantu membentuk interkoneksi CXL yang lebih cepat. “Ketika tiba waktunya untuk mengoptimalkan komputasi dan transportasi dengan berbagai subsistem dan protokol, NoC adalah solusi yang lebih baik,” lanjut Schirrmeister.

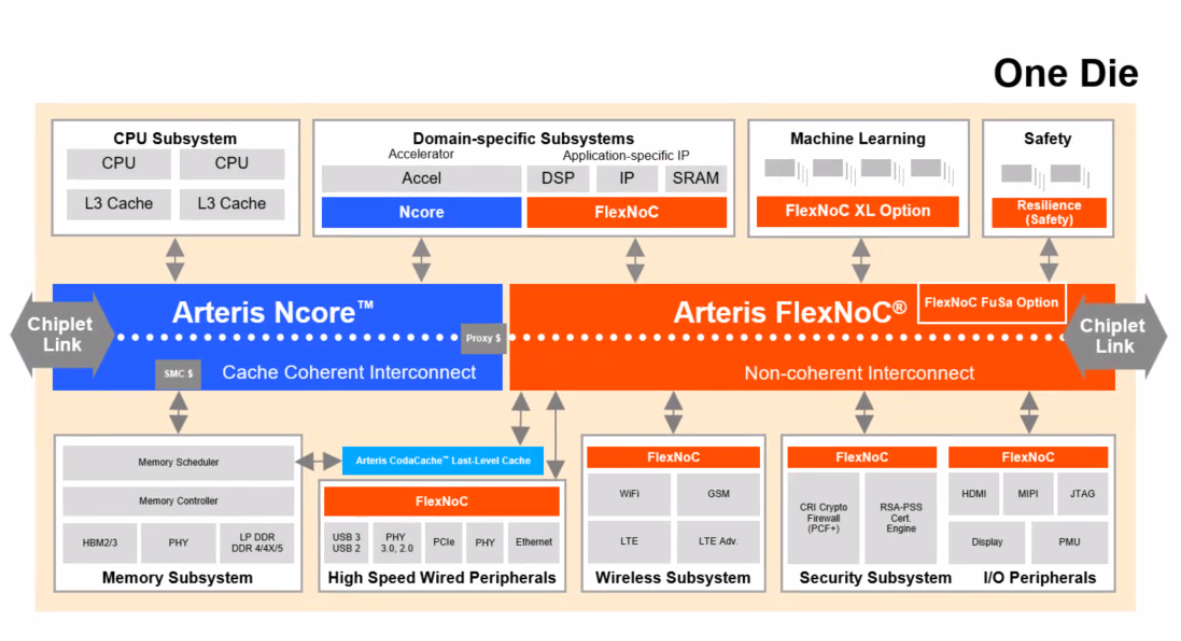

Seperti apa cara memasangkan inti RISC-V dengan NoC? Pelanggan Arteris, Tenstorrent, memberikan gambaran sekilas tentang kemungkinannya. Fokus terbaru mereka adalah menciptakan chiplet yang dapat digunakan kembali yang menggabungkan inti RISC-V, IP akselerasi pembelajaran mesin, dan periferal standar yang ditemukan di banyak aplikasi edge AI. Pada skala besar, implementasi single-die dapat terlihat seperti diagram berikut, menggunakan interkoneksi koheren cache Arteris Ncore dan beberapa segmen interkoneksi non-koheren Arteris FlexNoC.

gambar milik Arteris

Smart Memory Controller (SMC) menyediakan koneksi memori tingkat server berkinerja tinggi dalam aplikasi intensif memori. “Link chiplet” yang tidak disebutkan namanya mungkin adalah UCIe, spesifikasi yang relatif baru yang dioptimalkan untuk integrasi chiplet yang lebih erat. Ketika interkoneksi subsistem baru muncul, mengadaptasi bagian dari NoC lebih mudah dikelola daripada menghancurkan seluruh struktur chip.

Memasangkan inti RISC-V dengan NoC akan menurunkan risiko dan waktu pemasaran

Jika diagram tersebut terlihat rumit, dan memang benar, mungkin sebagian besar aplikasi RISC-V saat ini tidak terlalu rumit, pertimbangkan ini: chiplet sudah mendorong integrasi jauh lebih tinggi. Bagian multicore RISC-V yang canggih saat ini akan menjadi SoC bernilai tahun depan seiring dengan semakin pesatnya inovasi.

Alat pengembangan Arteris Ncore dan Arteris FlexNoC menghasilkan RTL untuk implementasi, memberikan beberapa keuntungan. Estimasi NoC fisik sangat mudah dilakukan dalam alur kerja EDA. Penyesuaian parameter NoC, seperti jumlah tahapan pipeline, juga hanya berjarak beberapa klik saja di alat EDA. Modifikasi yang disebutkan di atas untuk menambahkan protokol subsistem juga dapat dilakukan dengan mudah. “Di kelas atas, pengguna mendapatkan akses langsung ke keahlian NoC kami,” kata Schirrmeister. “Di tingkat bawah, alat kami mudah digunakan untuk mencapai kesuksesan tahap pertama dan memberikan jalur pertumbuhan untuk proyek-proyek masa depan yang lebih ambisius dengan interkoneksi yang kompleks.”

Memasangkan inti RISC-V dengan NoC menurunkan risiko satu blok IP lagi memasuki desain dan memicu gelombang desain ulang interkoneksi di seluruh chip. Hal ini juga mengurangi waktu pemasaran untuk desain SoC yang kompleks dibandingkan dengan struktur interkoneksi yang dilakukan sendiri. Kami belum membahas manfaat lain dari NoC di sini, seperti bandwidth dan manajemen daya, namun alasan untuk NoC dalam desain RISC-V cukup kuat hanya dengan mempertimbangkan campuran protokol yang beragam.

Kunjungi situs web Arteris untuk informasi lebih lanjut tentang NoC dan produk lainnya.

Bagikan postingan ini melalui:

- Konten Bertenaga SEO & Distribusi PR. Dapatkan Amplifikasi Hari Ini.

- PlatoData.Jaringan Vertikal Generatif Ai. Berdayakan Diri Anda. Akses Di Sini.

- PlatoAiStream. Intelijen Web3. Pengetahuan Diperkuat. Akses Di Sini.

- PlatoESG. Karbon, teknologi bersih, energi, Lingkungan Hidup, Tenaga surya, Penanganan limbah. Akses Di Sini.

- PlatoHealth. Kecerdasan Uji Coba Biotek dan Klinis. Akses Di Sini.

- Sumber: https://semiwiki.com/ip/arteris/336086-pairing-risc-v-cores-with-nocs-ties-soc-protocols-together/

- :memiliki

- :adalah

- :bukan

- :Di mana

- $NAIK

- a

- kemampuan

- atas

- percepatan

- mengakses

- dicapai

- Menurut

- di seluruh

- menambahkan

- penyesuaian

- maju

- keuntungan

- AI

- sudah

- juga

- ambisius

- an

- dan

- Lain

- jawaban

- Apa pun

- apa saja

- muncul

- aplikasi

- ADALAH

- sekitar

- AS

- At

- perhatian

- jauh

- Bandwidth

- bar

- BE

- menjadi

- Manfaat

- Lebih baik

- antara

- Memblokir

- Blok

- bis

- bisnis

- pengembangan bisnis

- tapi

- CAN

- kasus

- tantangan

- perubahan

- mengubah

- keping

- menggabungkan

- komoditi

- dibandingkan

- lengkap

- kompleks

- kompleksitas

- menghitung

- Terhubung

- koneksi

- Koneksi

- Mempertimbangkan

- dianggap

- mengingat

- terus

- terus menerus

- pengawas

- Core

- Corp

- bisa

- perhitungan

- membuat

- pelanggan

- data

- menetapkan

- definisi

- Permintaan

- Mendesain

- desainer

- desain

- Pengembangan

- alat pengembangan

- berbeda

- sulit

- dibahas

- beberapa

- do

- penggerak

- setiap

- Mudah

- Tepi

- efisien

- muncul

- muncul

- akhir

- memasuki

- Seluruh

- Bahkan

- pengalaman

- keahlian

- ekstensi

- lebih cepat

- beberapa

- bidang

- perkelahian

- Pertama

- aliran

- Fokus

- berfokus

- berikut

- Untuk

- pasukan

- ditemukan

- jujur

- dari

- fungsi

- masa depan

- Mendapatkan

- Gates

- Pemberian

- Melihat sekilas

- diberikan

- Pertumbuhan

- Memiliki

- membantu

- di sini

- High

- kinerja tinggi

- lebih tinggi

- Namun

- HTTPS

- gambar

- Segera

- implementasi

- in

- informasi

- Innovation

- sebagai gantinya

- integrasi

- interkoneksi

- interkoneksi

- ke

- IP

- IT

- NYA

- hanya

- Terbaru

- meluncurkan

- paling sedikit

- kurang

- 'like'

- Mungkin

- baris

- baris

- lagi

- melihat

- terlihat seperti

- TERLIHAT

- Rendah

- menurunkan

- pengelolaan

- banyak

- max-width

- Mungkin..

- mungkin

- Memori

- tersebut

- metrik

- mencampur

- moderat

- modern

- Modifikasi

- lebih

- paling

- terharu

- banyak

- beberapa

- harus

- New

- berikutnya

- tidak

- Gagasan

- sekarang

- jumlah

- of

- on

- ONE

- dibuka

- dioptimalkan

- or

- Lainnya

- kami

- keluaran

- Perdamaian

- pasangan

- parameter

- bagian

- path

- untuk

- prestasi

- sekeliling

- peripheral

- fisik

- memilih

- Pilihan

- pipa saluran

- plato

- Kecerdasan Data Plato

- Data Plato

- Bermain

- bermain

- kemungkinan

- Pos

- potensi

- kekuasaan

- kuat

- Prosesor

- Produk

- memprojeksikan

- protokol

- protokol

- memberikan

- menyediakan

- menyediakan

- segera

- segera

- baru

- mengakui

- mendesain ulang

- mengurangi

- relatif

- penelitian

- dapat digunakan kembali

- benar

- Ripple

- Naik

- Risiko

- Run

- s

- mengatakan

- Skala

- skenario

- skema

- Bagian

- terlihat

- melihat

- segmen

- memilih

- beberapa

- Bentuknya

- berbagi

- Sederhana

- sejak

- tunggal

- pintar

- larutan

- Solusi

- beberapa

- mutakhir

- spesifikasi

- magang

- standar

- mudah

- kuat

- struktur

- struktur

- selanjutnya

- sukses

- seperti itu

- kekuatan terbesar

- Teknologi

- dari

- bahwa

- Grafik

- mereka

- Ini

- Ketiga

- ini

- pikir

- tiga

- tingkat

- Dasi

- lebih ketat

- waktu

- untuk

- hari ini

- bersama

- alat

- mengangkut

- memicu

- TANPA NAMA

- diperbarui

- menggunakan

- Pengguna

- menggunakan

- nilai

- berbagai

- bervariasi

- melalui

- View

- vp

- we

- Situs Web

- Apa

- Apa itu

- ketika

- akan

- dengan

- Kerja

- alur kerja

- zephyrnet.dll