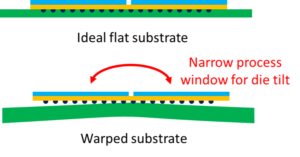

Tren perampingan perangkat menimbulkan tuntutan terus-menerus untuk meningkatkan input/output (I/O) dan kepadatan sirkuit, dan kebutuhan ini mendorong pengembangan paket High-Density Fan-Out (HDFO) dengan lapisan redistribusi tembaga halus (Cu). (RDL). Untuk aplikasi seluler dan jaringan dengan kinerja tinggi, HDFO adalah solusi yang muncul karena aturan desain yang agresif dapat diterapkan pada HDFO dibandingkan dengan jenis paket lainnya seperti Wafer Level Fan-Out (WLFO). HDFO memungkinkan perakitan lebih dari satu chip dalam satu paket dan sebagian besar RDL Cu halus digunakan untuk menghubungkan chip. Selain itu, HDFO dapat dibuat dalam tingkat wafer dan substrat tergantung pada aplikasinya, yang memiliki skalabilitas lebih baik dalam hal ukuran paket.

Cu RDL di HDFO tertanam dengan lapisan dielektrik seperti polimida (PI) dan mentransfer sinyal antar chip atau dari substrat ke chip. Saat arus mengalir melalui RDL Cu, panas terakumulasi dalam konduktor karena timbulnya pemanasan Joule. Akumulasi panas ini dapat menyebabkan penurunan kinerja. Karena kepadatan arus yang diperlukan dan suhu pemanasan Joule meningkat dalam struktur RDL Cu halus, hal ini dianggap sebagai faktor penting pada kinerja pengemasan HDFO.

Karena RDL Cu yang halus harus memiliki kinerja keandalan yang tinggi, berbagai struktur RDL diperkenalkan baru-baru ini, seperti jejak RDL tertanam (ETR) dan jejak Cu yang dilapisi dengan dielektrik anorganik untuk interkoneksi kepadatan tinggi dan kinerja keandalan [1, 2]. Banyak penelitian mengenai evaluasi kinerja keandalan RDL Cu yang baik telah dilakukan juga.

Electromigration (EM) adalah salah satu item untuk mengevaluasi keandalan dan kinerja karakteristik listrik Cu RDL. EM adalah mekanisme yang dikendalikan difusi dengan pergerakan bertahap atom logam dalam konduktor sebagai akibat dari aliran elektron. Pengangkutan massa atom logam ini menyebabkan terbentuknya rongga di sisi katoda dan bukit kecil di sisi anoda konduktor. Proses-proses ini mengakibatkan hilangnya kontinuitas listrik. Perilaku elektromigrasi dipengaruhi oleh ukuran fitur, kondisi tegangan, arah aliran elektron, dan struktur pengujian seperti metalurgi sambungan. Dalam pengujian Cu RDL EM, tidak hanya terdapat gaya aliran elektron tetapi juga gradien termal pada konduktor, sehingga degradasi EM disebabkan oleh potensial listrik dan energi panas [3].

Dengan menggunakan hasil uji EM, dimungkinkan untuk memprediksi kepadatan arus atau masa pakai maksimum yang diijinkan dalam kondisi lapangan tertentu. Pengujian EM dilakukan dalam kondisi yang dipercepat dan ekstrapolasi berdasarkan data eksperimen EM dapat digunakan untuk memperkirakan nilai kasus penggunaan saat ini atau seumur hidup. Untuk perhitungan, model Black yang diterbitkan oleh James Black pada tahun 1969 banyak digunakan. Beberapa faktor dalam model ini ditentukan dengan menyesuaikan model distribusi kegagalan seperti distribusi Weibull dan lognormal. Dalam makalah ini dijelaskan karakterisasi EM dan hasil analisis kegagalan RDL Cu dengan ≤ 10 µm dalam paket HDFO pada berbagai kondisi arus dan suhu. Selain itu, peningkatan rasio perkiraan arus maksimum yang diijinkan dalam beberapa kondisi penggunaan suhu pengoperasian dan masa pakai juga disediakan.

Struktur Cu RDL dalam paket HDFO

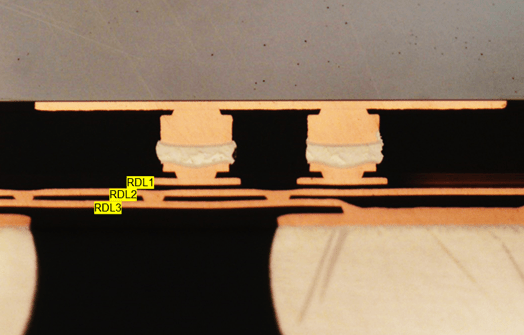

Paket HDFO dibuat untuk pengujian Cu RDL EM. Ukuran badan paket dan cetakan masing-masing adalah 8.5 mm x 8.5 mm dan 5.6 mm x 5.6 mm. TV HDFO memiliki struktur RDL multi-lapis yang memiliki tiga lapisan dengan ketebalan 3-µm dan lapisan benih Ti/Cu untuk setiap RDL. Juga, polimida diaplikasikan sebagai bahan dielektrik yang mengelilingi RDL Cu halus. Di atas struktur RDL terdapat pilar Cu bump, die dan mold. Jenis cetakannya adalah cetakan yang menutupi sisi atas cetakan. Struktur Cu RDL secara keseluruhan ditunjukkan pada Gambar 1.

Gambar 1: Tampilan penampang kendaraan uji HDFO dengan tiga RDL-nya.

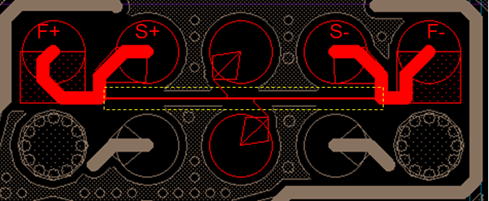

RDL Cu lurus dengan panjang 1000 µm, lebar 2 dan 10 µm dirancang dan diuji. RDL Cu adalah lapisan paling bawah (RDL3) di HDFO. Empat bola ball grid array (BGA) dihubungkan ke Cu RDL yang diuji untuk pemaksaan arus dan penginderaan tegangan. Gambar 2 menunjukkan ilustrasi skema desain RDL yang diuji.

Gambar 2: Desain Cu RDL untuk uji elektromigrasi. 'F' dan 'S' masing-masing berarti pemaksaan arus dan penginderaan tegangan.

Pengujian elektromigrasi

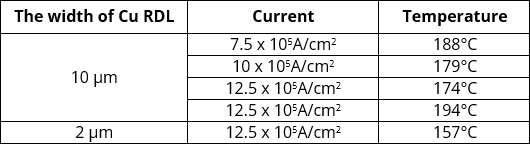

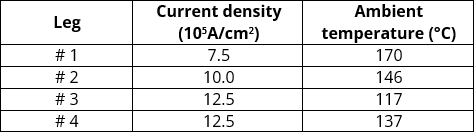

Kendaraan uji HDFO dipasang di permukaan ke papan uji untuk sambungan listrik dengan sistem uji EM dan pengisian bawah kedua tidak diterapkan setelah pemasangan di permukaan. RDL Cu selebar 10 µm diberi tekanan pada arus searah 7.5, 10 dan 12.5 x 105A/cm2 dan suhu 174, 179, 188 dan 194°C. Uji Cu RDL EM lebar 2 µm juga diuji pada arus searah 12.5 x 105A/cm2 dan suhu 157°C. Kondisi pengujian ditunjukkan pada tabel 1. Suhu pengujian dianggap sebagai suhu pada RDL Cu. Oleh karena itu, suhu oven diatur dengan mengkompensasi jumlah pemanasan Joule. Kalibrasi pemanasan joule dilakukan pada setiap tegangan arus karena bergantung pada besarnya rapat arus.

Untuk kalibrasi pemanasan Joule, resistansi diukur pada berbagai suhu dalam kondisi arus rendah dan tegangan. Arus rendah dianggap sebagai kondisi yang menghasilkan pemanasan non-Joule. Nilai resistansi meningkat seiring dengan peningkatan suhu lingkungan dan perilaku perubahan resistansi pada kondisi arus rendah digunakan untuk memperoleh nilai koefisien resistansi termal (TCR). Setelah dilakukan pengukuran resistansi pada beberapa kondisi temperatur, besarnya pemanasan Joule dihitung menggunakan TCR dan selisih resistansi antara kondisi rendah dan kondisi arus uji. Suhu pemanasan Joule yang dihitung dari setiap kondisi pengujian saat ini dan suhu pada RDL Cu dengan lebar 10 µm ditunjukkan pada tabel 2.

Tabel 1: Kondisi pengujian garis halus Cu RDL EM.

Tabel 2 Suhu pemanasan joule dan suhu pada rdl. Empat kondisi pengujian dilakukan untuk pengujian Cu RDL EM halus.

Pengujian EM dilanjutkan hingga resistansi meningkat 100% dan kriteria penentuan waktu kegagalan (TTF) untuk menghitung arus maksimum yang diijinkan ditetapkan sebesar peningkatan resistansi 20%. Kriteria persentase kenaikan resistensi diketahui paling efektif jika semua struktur menunjukkan resistensi awal yang sangat mirip. Resistansi awal pada kondisi tegangan adalah 0.7 hingga 0.8 ohm untuk RDL Cu dengan lebar 10 µm, sehingga nilainya terlihat cukup mirip satu sama lain. Pada pengujian EM, resistansi RDL Cu diukur menggunakan teknik pengukuran 4 titik. Jumlah sampel uji ditentukan menjadi 18 hingga 20 untuk analisis statistik yang bermakna.

Selain mikroskop optik, berkas ion terfokus (FIB)/scanning emisi lapangan mikroskop elektron (FESEM) digunakan untuk analisis kegagalan guna memahami degradasi selama uji migrasi listrik. Selain analisis gambar tampilan atas, area tertentu dipotong melintang dengan penggilingan ion galium (Ga) untuk mengamati reduksi area RDL Cu oleh oksidasi dan rongga Cu.

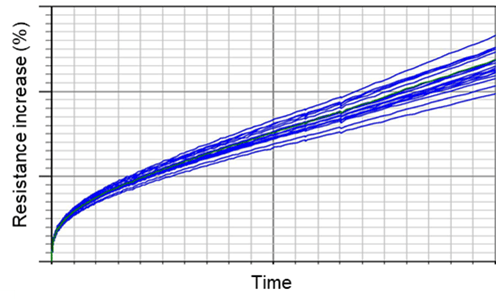

Perlawanan mengubah perilaku

Perilaku peningkatan resistansi RDL Cu lebar 10 µm selama pengujian EM ditunjukkan pada gambar 3. Tren peningkatan resistansi dapat dibagi menjadi dua mode berbeda. Pada tahap awal, resistensi terus meningkat, tetapi setelah mencapai % peningkatan resistensi tertentu, perubahan resistensi terjadi dengan cepat. Alasan peningkatan resistensi pada dua tahap tersebut adalah karena mode kegagalan yang terjadi secara dominan berbeda pada setiap tahap.

Perbedaan masa pakai berdasarkan kondisi suhu dan distribusi time to fail (TTF) pada kondisi pengujian yang sama juga ditunjukkan pada Gambar 3. Diperkirakan alasan distribusi TTF pada kondisi yang sama adalah karena perbedaan ukuran butir setiap RDL Cu. di antara kendaraan uji. Jalur difusi atom logam Cu adalah batas butir, antarmuka material dan logam curah, serta energi aktivasi setiap jalur difusi berbeda-beda. Karena energi aktivasi batas butir atau antarmuka material lebih rendah dibandingkan logam curah, difusi melalui batas butir atau antarmuka material lebih dominan selama EM. Oleh karena itu, ukuran butir merupakan faktor penting yang menentukan TTF selama pengujian EM [4].

Dalam kasus kepadatan arus yang lebih rendah yaitu 7.5A/cm2, sebagian besar sampel menunjukkan peningkatan resistansi yang lebih rendah dan kurva yang lebih halus dibandingkan dengan arus tinggi 12.5A/cm2 seperti yang ditunjukkan pada gambar 3 (c). Berdasarkan hasil yang diperoleh, diharapkan kondisi arus rendah ini mempunyai mode kegagalan yang tidak terlalu parah dibandingkan kondisi arus tinggi, namun mode kegagalan tidak terlihat berbeda secara signifikan antara kondisi arus tinggi dan rendah. Pada penelitian selanjutnya direncanakan akan dilakukan analisis kegagalan terhadap langkah-langkah resistensi perubahan perilaku.

Pengujian EM tambahan dilakukan dengan RDL Cu lebar 2 µm dalam kondisi kerapatan arus yang sama (12.5×105A/cm2) dengan RDL Cu lebar 10 µm dan kondisi suhu yang lebih rendah. Plot peningkatan resistensi selama pengujian EM disajikan pada gambar 4. Dalam hal ini, perilaku perubahan resistensi hanya menunjukkan peningkatan resistensi yang terus-menerus bahkan dalam waktu pengujian yang lama hingga 10 Khrs, yang berbeda dari kasus RDL Cu dengan lebar 10 µm. Berdasarkan perbedaan perilaku perubahan resistansi antara kondisi temperatur rendah dan tinggi, diduga mode kegagalan pada temperatur tinggi dan rendah tidak sama. Selain itu, diharapkan bahwa mode kegagalan RDL Cu selebar 2 µm terutama terjadi karena tahap resistensi yang terus meningkat.

Untuk RDL Cu dengan lebar 10 µm, jumlah unit yang memenuhi kriteria kegagalan peningkatan resistansi 20% dan 100% ditunjukkan pada tabel 3. Semua unit yang diuji memenuhi kriteria kegagalan 20% dalam waktu 8,000 jam dan beberapa unit menunjukkan di bawah 100 jam. % resistensi meningkat ketika waktu pengujian 10,000 jam. Karena jumlah unit kegagalan cukup untuk melakukan analisis statistik, uji EM dihentikan pada 10,000 jam. Selain itu, data EM yang resistansinya meningkat sebesar 100% diamankan sehingga memungkinkan untuk menghitung kapasitas arus maksimum tergantung pada berbagai kriteria kegagalan.

Gambar 3: Perilaku peningkatan resistensi selama uji EM 10-µm lebar RDL, 12.5A/cm2 arus dan (a) pada 174°C dan (b) suhu 194°C dan (c) 7.5A/cm2 dan 188°C.

Gambar 4: Perilaku peningkatan resistansi selama uji EM pada RDL lebar 2 µm. Kondisi pengujian adalah rapat arus 12.5A/cm2 dan suhu 157°C.

Tabel 3: Jumlah unit yang gagal 10-µm lebar Cu RDL untuk setiap kondisi.

Analisis mode kegagalan

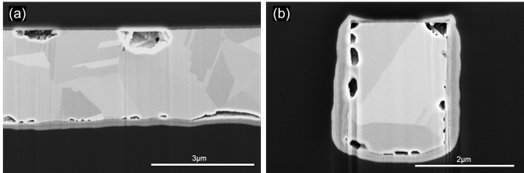

Untuk memahami mekanisme kegagalan uji halus Cu RDL EM, mikroskop optik dan FIB/FESEM digunakan untuk mengamati tampilan atas dan penampang. Gambar 5 menunjukkan lebar Cu RDL 2-µm dan 10-µm setelah pemasangan permukaan pada papan uji. Ketebalan dan lebarnya telah sesuai dengan nilai desain dan tidak terdapat kelainan seperti permukaan tidak rata, rongga dan delaminasi antara Cu dan PI pada Cu RDL. Seperti terlihat pada gambar 5, dipastikan ukuran butir pada RDL bervariasi. Karena cacat dapat mempengaruhi kinerja elektromigrasi, kualitas Cu RDL harus diperiksa sebelum uji EM.

Gambar 5: Gambar FIB/FESEM dari Cu RDL setelah pemasangan di permukaan: (a) lebar 10-µm dan (b) lebar 2-µm.

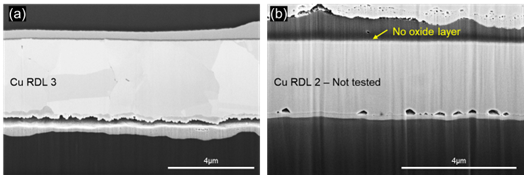

Dalam kasus RDL Cu dengan lebar 10 µm, berbagai mode kegagalan diamati seperti yang ditunjukkan pada gambar 6. Pertama, delaminasi dan oksida Cu diamati antara RDL Cu dan pasivasi, yang menyebabkan pengurangan area RDL Cu dan terutama disebabkan oleh resistensi meningkat. Berkurangnya area RDL Cu juga mengakibatkan kepadatan saat ini dan suhu yang lebih tinggi pada RDL dan degradasi EM juga semakin cepat. Selama pengujian EM, rongga dihasilkan karena migrasi atom Cu dan delaminasi tampaknya disebabkan oleh pertumbuhan rongga di sepanjang antarmuka antara pasivasi dan RDL Cu. Nilai eksponen kepadatan arus mencerminkan fenomena mana yang lebih dominan antara kekosongan nukleasi dan pertumbuhan. [5] Mengenai lapisan oksida Cu dan difusi ke PI, difusi Cu tampaknya dipercepat karena aliran elektron atau/dan gradien termal karena pada RDL2 (tidak diuji EM), tidak ada lapisan oksida pada lapisan benih Ti/Cu untuk bertindak sebagai lapisan penghalang seperti yang ditunjukkan pada gambar 6 (b).

Antara Cu RDL2 dan PI, hanya rongga dan lapisan oksida Cu yang diamati, yang disebabkan oleh tekanan termal. Dengan kata lain, mode kegagalan yang diamati pada Cu RDL2 dapat dianggap sebagai penyimpanan suhu tinggi (HTS) untuk waktu yang lama.

Gambar 6: Mikroskop optik dan gambar FIB/FESEM dengan lebar 10 µm Cu RDL setelah pengujian pada 12.5×105A/cm2, 174°C: (a) Cu oksida dan delaminasi pada RDL3 yang diuji dan (b) tidak ada oksidasi Cu pada lapisan benih Ti/Cu pada RDL2 (tidak diuji EM).

Berbeda dengan RDL Cu dengan lebar 10 µm, RDL Cu dengan lebar 2 µm tidak menunjukkan delaminasi antara RDL Cu dan PI, seperti yang ditunjukkan pada gambar 7. Dari Cu RDL lebar 2 µm yang tidak terlalu rusak, diduga tumbuhnya rongga sepanjang antarmuka antara Cu RDL dan PI mengakibatkan delaminasi seperti yang ditunjukkan pada RDL Cu lebar 10 µm. Selain itu, delaminasi ini dianggap sebagai faktor utama yang menyebabkan tahap kedua menunjukkan peningkatan resistensi secara tiba-tiba. Direncanakan untuk melakukan studi elektromigrasi RDL 2-µm Cu pada kondisi arus yang lebih tinggi untuk perbandingan mode kegagalan dan nilai parameter pada persamaan Black dengan hasil elektromigrasi RDL 10-µm Cu. Selain itu, diharapkan dapat menentukan mode kegagalan dari setiap langkah peningkatan resistensi melalui studi lebih lanjut ini.

Gambar 7: Mikroskop optik dan gambar FIB/FESEM dengan lebar 2 µm Cu RDL setelah pengujian pada 12.5×105A/cm2, 157°C: (a) Cu oksida kosong pada RDL3 dan (b) sumbu penggilingan FIB berbeda pada Cu RDL3.

Simulasi pemanasan joule

Untuk memprediksi jumlah pemanasan Joule dan lokasi kegagalan, simulasi listrik-termal dilakukan untuk RDL Cu lebar 10 µm. Ketika jumlah akumulasi panas berbeda dalam jejak Cu, tingkat kegagalan dapat berbeda berdasarkan lokasi karena kerusakan EM tidak hanya disebabkan oleh gaya aliran elektron tetapi juga gradien termal. Seperti disajikan pada gambar 8, desain pengujian aktual dan struktur TV HDFO serta papan pengujian tercermin dalam model simulasi, dan konduktivitas termal efektif setiap struktur juga diterapkan. Tabel 4 menunjukkan desain percobaan (DOE) berdasarkan suhu oven dan arus sumber. Suhu oven dapat dianggap sebagai suhu sekitar dan jumlah pemanasan Joule diperkirakan bervariasi sesuai arus sumber. Hasil simulasi pemanasan Joule ditunjukkan pada Gambar 9. Selisih besaran pemanasan Joule antara nilai simulasi dan eksperimen adalah 1.3 hingga 4.2°C, dan nilai keduanya hampir sama. Selain itu, lokasi yang menunjukkan suhu lokal tertinggi adalah di tengah RDL Cu tempat bantalan logam dihubungkan, yang sangat cocok dengan lokasi kegagalan sebenarnya setelah pengujian EM. Ringkasnya, hasil simulasi pemanasan Joule sangat cocok dengan hasil uji EM aktual dalam hal jumlah pemanasan Joule dan lokasi kegagalan, yang berguna untuk memahami degradasi EM Cu RDL dan memprediksi lokasi kegagalan.

Gambar 8: Model simulasi pemanasan joule untuk RDL Cu lebar 10 µm.

Tabel 4: DOE untuk simulasi pemanasan Joule.

Gambar 9 Hasil simulasi pemanasan joule : (a) kontur suhu dan titik menunjukkan suhu tertinggi dibawah 12.5 x 105A/cm2 dan 137°C. (b) perbandingan besaran pemanasan Joule antara eksperimen dan simulasi.

Perhitungan daya dukung saat ini

Untuk menghitung arus maksimum dalam kondisi lapangan, persamaan Black, yang berhubungan dengan waktu hingga kegagalan dalam uji migrasi listrik, banyak digunakan.

MTTF = AJ-n exp (Ea/Kt) (1)

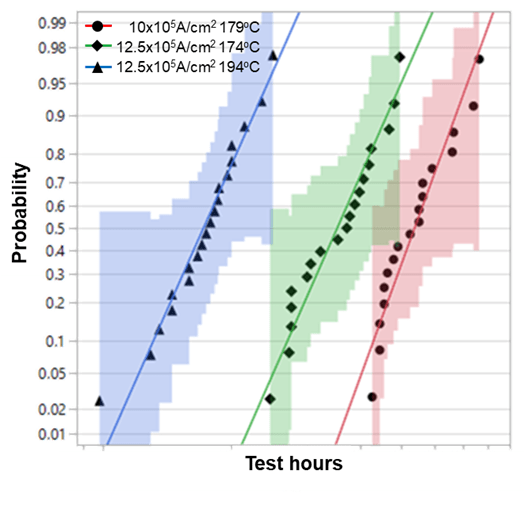

Dimana MTTF adalah waktu rata-rata terjadinya kegagalan, A adalah konstanta empiris, J adalah rapat arus, n adalah eksponen rapat arus, Ea adalah energi aktivasi (eV), K adalah konstanta Boltzmann (8.62×10-5 eV/K) dan T adalah suhu (K). Untuk menentukan parameter persamaan Black seperti A, n dan Ea, analisis statistik harus dilakukan terlebih dahulu. Hal ini sangat penting karena ekstrapolasi ke persentase kegagalan yang lebih rendah berdasarkan hasil analisis statistik digunakan untuk memperkirakan daya dukung saat ini. Dua metode umum untuk menggambarkan distribusi kegagalan EM adalah plot Weibull dan lognormal. Distribusi lognormal lebih disukai ketika menganalisis kegagalan garis logam dan vias, sedangkan model Weibull biasanya digunakan ketika struktur pengujian memiliki banyak elemen independen yang dapat menyebabkan kegagalan seperti migrasi listrik benjolan dan bola BGA. [6] Karena pilihan model pemasangan bisa menjadi penting ketika memperkirakan arus maksimum dalam kasus penggunaan, studi mengenai model distribusi dalam migrasi listrik juga telah dilakukan [7]. Dalam penelitian ini, distribusi lognormal dipilih sebagai model pemasangan dan grafik distribusi lognormal RDL Cu lebar 10 µm ditunjukkan pada gambar 10.

Daya dukung arus maksimum dihitung berdasarkan asumsi bahwa mode kegagalan antara pengujian ini dan kasus penggunaan sama, dan persamaan Black berlaku untuk pengujian yang dipercepat dan kondisi lapangan. Kapasitas arus maksimum dalam use case diperkirakan menggunakan Persamaan 2. Dalam hal ini, tingkat kegagalan diasumsikan 0.1% dan nilai 3.09 berasal dari skor Z distribusi lognormal standar.

J = [A exp (Ea/KT – 3.09σ)/TTF]-n (2)

Dimana T adalah suhu kondisi penggunaan dan TTF adalah perkiraan masa pakai dalam kasus penggunaan. Untuk Cu RDL lebar 10 µm, Ea dan n ditentukan masing-masing sebesar 0.74 dan 1.88. Secara umum, nilai energi aktivasi dan eksponen rapat arus masing-masing dikenal sebagai 1 dan 2. Selain itu, nilai eksponen kerapatan arus 2 dan 1 umumnya dianggap masing-masing sebagai kendali nukleasi kosong dan kendali pertumbuhan. Dalam uji EM ini, mekanisme kegagalan tampaknya merupakan campuran dari kekosongan nukleasi dan pertumbuhan, dan lebih khusus lagi, kekosongan nukleasi tampak lebih dominan. Jika mekanisme kegagalan tidak sama dengan penelitian ini karena beberapa alasan seperti kondisi pengujian yang parah atau struktur pengujian yang berbeda, maka nilai estimasinya mungkin berbeda. Biasanya nilai eksponen rapat arus (n) meningkat ketika kondisi tegangan berlebih mempercepat degradasi EM dengan pemanasan Joule.

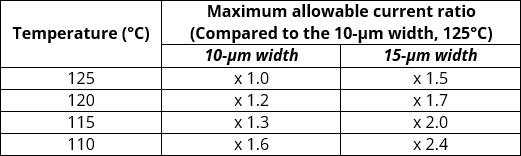

Tabel 5 menunjukkan peningkatan rasio perkiraan arus maksimum yang diijinkan dibandingkan dengan nilai pada kondisi lapangan yaitu masa pakai 100,000 jam, siklus kerja 100% dan tingkat kegagalan 0.1%. Nilai referensi untuk perbandingan adalah lebar 10-µm pada 125°C, yang ditetapkan sebagai 1. Ketika suhu pengoperasian diturunkan dari 125°C menjadi 110°C, perkiraan kapasitas arus meningkat sebesar 1.6 dan 2.4 untuk 10- dan 15. lebarnya masing-masing 2 µm. Kriteria kegagalan mempengaruhi nilai arus maksimum yang diijinkan, sehingga penting untuk memilih kapasitas arus maksimum untuk suatu desain. Seperti yang ditunjukkan oleh Persamaan (XNUMX), arus maksimum meningkat secara eksponensial – tidak sebanding dengan suhu pengoperasian. Ketika nilai perkiraan arus ini digunakan untuk desain jejak, maka arus sekering RDL juga harus diperhitungkan karena terdapat titik persilangan antara arus maksimum yang diijinkan yang dihitung dan arus sekering aktual.

Gambar 10: Distribusi lognormal untuk plot probabilitas kegagalan RDL Cu lebar 10 µm.

Tabel 5: Rasio arus maksimum yang diperbolehkan (mA) pada beberapa kondisi lapangan. Nilai lebar 10-µm pada 125°C ditetapkan sebagai 1.

Kesimpulan

Perilaku migrasi listrik dan mode kegagalan RDL Cu garis halus untuk paket fan-out kepadatan tinggi dilaporkan dalam penelitian ini. Lebar Cu RDL yang diuji adalah 2- dan 10-µm, dan peningkatan resistansi akibat degradasi oleh migrasi listrik berbeda untuk setiap kondisi pengujian. Dalam kasus RDL Cu dengan lebar 10 µm, terdapat dua tahap yang menunjukkan perilaku perubahan resistensi yang berbeda. Pada tahap pertama, resistensi terus meningkat dan kekosongan nukleasi serta pertumbuhan diperkirakan sebagai fenomena yang paling banyak terjadi pada tahap pertama. Langkah kedua adalah bagian dimana resistensi meningkat dengan cepat. Tahap ini hanya ditunjukkan pada kasus RDL Cu lebar 10 µm, yang menunjukkan delaminasi antara RDL Cu dan PI berbeda dengan RDL lebar 2 µm yang diuji dengan suhu rendah dan hanya menunjukkan oksida Cu dan rongga. Oleh karena itu, disimpulkan bahwa delaminasi akibat void growth merupakan faktor utama yang mempengaruhi peningkatan resistensi pada langkah kedua.

Mode kegagalan yang diamati setelah migrasi listrik adalah pengurangan area Cu karena oksidasi Cu dan pembentukan/pertumbuhan rongga. Karena migrasi Cu ke PI juga diamati, tampaknya dipercepat karena aliran elektron atau/dan gradien termal. Karena degradasi termal PI harus dipertimbangkan dalam pengujian Cu RDL EM, simulasi listrik-termal dilakukan untuk memprediksi posisi lemah yang mudah rusak dan hasilnya sesuai dengan hasil pengujian sebenarnya. Selain itu, jumlah pemanasan Joule yang diperoleh melalui simulasi hampir sama dengan nilai eksperimen sebenarnya.

Berdasarkan hasil Cu RDL EM lebar 10 µm, persamaan Black diselesaikan sehingga dapat dihitung daya dukung arus maksimum. Distribusi lognormal digunakan untuk analisis statistik dengan nilai perhitungan Ea dan eksponen rapat arus masing-masing adalah 0.74 dan 1.88. Perkiraan arus maksimum dalam kondisi lapangan dapat berguna untuk merancang RDL, namun ada beberapa pertimbangan seperti nilai arus sekering aktual dan ketergantungan Ea dan eksponen kerapatan arus pada mode kegagalan dan kondisi pengujian.

Pengakuan

Penelitian ini didukung oleh pusat R&D Global Amkor Technology. Penulis mengucapkan terima kasih kepada tim R&D Proses/Penelitian Material untuk persiapan TV fan-out dengan kepadatan tinggi. Juga terima kasih kepada rekan-rekan lab R&D yang bekerja sama dalam persiapan DUT dan analisis kegagalan.

Referensi

- S. Jin, W. Do, J. Jeong, H. Cha, Y. Jeong dan J. Khim, “Kemasan Substrat Silicon Wafer Integrated Fan-out Technology (S-SWIFT) dengan Fine Pitch Embedded Trace RDL,” 2022 IEEE 72nd Konferensi Komponen dan Teknologi Elektronik (ECTC), 2022, hlm. 1355-1361, doi: 10.1109/ECTC51906.2022.00218.

- H. Kudo dkk., “Demonstrasi ketahanan migrasi listrik yang tinggi pada lapisan redistribusi Cu skala sub-2 mikron yang ditingkatkan untuk pengemasan nada halus yang canggih,” 2017 IEEE CPMT Symposium Japan (ICSJ), 2017, hlm. 5-8, doi : 10.1109/ICSJ.2017.8240055.

- C.-L. Liang, Y.-S. Lin, C.-L. Kao, D. Tarng dkk., “Keandalan Elektromigrasi dari Kemasan Fan-out Berdensitas Tinggi Tingkat Lanjut dengan Jalur Redistribusi Cu 2μm/2μm L/S Cu,” Transaksi IEEE pada Teknologi Pengemasan dan Manufaktur Komponen, hal. 1438-1445 , 2020.

- M. Rovitto, “Masalah Keandalan Elektromigrasi dalam Interkoneksi untuk Teknologi Integrasi Tiga Dimensi,” tidak dipublikasikan.

- M. Hauschildt dkk., “Kegagalan awal elektromigrasi menghilangkan fenomena nukleasi dan pertumbuhan dalam interkoneksi Cu dan Cu(Mn),” Simposium Fisika Reliabilitas Internasional (IRPS) IEEE 2013, Monterey, CA, AS, 2013, hal. 2C.1.1, doi: 2/IRPS.1.6.

- JEP154, “Pedoman untuk Mengkarakterisasi Elektromigrasi Benjolan Solder di Bawah Tekanan Arus dan Suhu Konstan,” JEDEC, 2008.

- A. Basavalingappa, JM Passage, MY Shen dan JR Lloyd, “Electromigration: Lognormal versus Weibull distribution,” Lokakarya Keandalan Terintegrasi Internasional (IIRW) IEEE 2017, South Lake Tahoe, CA, AS, 2017, hlm. 1/IIRW.4.

- Konten Bertenaga SEO & Distribusi PR. Dapatkan Amplifikasi Hari Ini.

- PlatoData.Jaringan Vertikal Generatif Ai. Berdayakan Diri Anda. Akses Di Sini.

- PlatoAiStream. Intelijen Web3. Pengetahuan Diperkuat. Akses Di Sini.

- PlatoESG. Karbon, teknologi bersih, energi, Lingkungan Hidup, Tenaga surya, Penanganan limbah. Akses Di Sini.

- PlatoHealth. Kecerdasan Uji Coba Biotek dan Klinis. Akses Di Sini.

- Sumber: https://semiengineering.com/electromigration-performance-of-fine-line-cu-redistribution-layer-rdl-for-hdfo-packaging/

- :memiliki

- :adalah

- :bukan

- :Di mana

- $NAIK

- 000

- 09

- 1

- 1.3

- 10

- 100

- 12

- 173

- 179

- 20

- 2008

- 2013

- 2017

- 2020

- 2022

- 212

- 521

- 7

- 8

- 820

- 9

- a

- atas

- tiba-tiba

- dipercepat

- mempercepat

- Akumulasi

- akumulasi

- Bertindak

- Activation

- sebenarnya

- tambahan

- maju

- mempengaruhi

- terpengaruh

- Setelah

- agresif

- AL

- Semua

- memungkinkan

- hampir

- sepanjang

- juga

- Ambient

- antara

- jumlah

- an

- analisis

- menganalisis

- dan

- Muncul

- Aplikasi

- terapan

- ADALAH

- DAERAH

- daerah

- susunan

- AS

- Majelis

- diasumsikan

- asumsi

- At

- penulis

- Sumbu

- b

- bola

- pembatas

- berdasarkan

- BE

- Balok

- karena

- menjadi

- sebelum

- laku

- Lebih baik

- antara

- Black

- papan

- tubuh

- kedua

- Bawah

- batas-batas

- tapi

- by

- CA

- menghitung

- dihitung

- menghitung

- perhitungan

- datang

- CAN

- Kapasitas

- dilakukan

- membawa

- kasus

- Menyebabkan

- pusat

- tertentu

- perubahan

- ciri

- Grafik

- diperiksa

- keping

- Keripik

- pilihan

- rekan

- dibandingkan

- perbandingan

- Lengkap

- komponen

- Disimpulkan

- kondisi

- Kondisi

- Mengadakan

- dilakukan

- daya konduksi

- konduktor

- Konferensi

- DIKONFIRMASI

- terhubung

- koneksi

- pertimbangan

- dianggap

- konstan

- terus

- kontinuitas

- kontinu

- berkontribusi

- Tembaga

- bisa

- tercakup

- penutup

- kriteria

- kritis

- Cross

- terbaru

- melengkung

- siklus

- kerusakan

- data

- menurun

- tuntutan

- kepadatan

- Ketergantungan

- Tergantung

- tergantung

- menggambarkan

- dijelaskan

- Mendesain

- dirancang

- Menentukan

- ditentukan

- ditentukan

- menentukan

- Pengembangan

- Devices

- MELAKUKAN

- Mati

- perbedaan

- berbeda

- Difusi

- langsung

- arah

- distribusi

- Terbagi

- do

- DOE

- dominan

- perampingan

- dua

- selama

- E&T

- EA

- setiap

- Awal

- tahap awal

- mudah

- Efektif

- Elektronik

- elemen

- tertanam

- muncul

- emisi

- mendorong

- energi

- ditingkatkan

- memperkirakan

- diperkirakan

- EV

- mengevaluasi

- evaluasi

- Bahkan

- diharapkan

- eksperimen

- eksperimental

- eksperimen

- eksponensial

- faktor

- faktor

- Gagal

- Kegagalan

- Fitur

- beberapa

- bidang

- Angka

- akhir

- Pertama

- sesuai

- aliran

- Mengalir

- terfokus

- Untuk

- kekuatan

- paksaan

- pembentukan

- empat

- dari

- lebih lanjut

- sekering

- Umum

- umumnya

- dihasilkan

- menghasilkan

- generasi

- memberikan

- Aksi

- bertahap

- kisi

- Pertumbuhan

- Memiliki

- bermanfaat

- High

- lebih tinggi

- paling tinggi

- HTTPS

- identik

- IEEE

- if

- gambar

- analisis gambar

- penting

- in

- Di lain

- Meningkatkan

- Pada meningkat

- Meningkatkan

- meningkatkan

- independen

- menunjukkan

- mempengaruhi

- mulanya

- terpadu

- integrasi

- interkoneksi

- interkoneksi

- Antarmuka

- Internasional

- ke

- diperkenalkan

- isu

- IT

- item

- NYA

- james

- Jepang

- bersama

- dikenal

- laboratorium

- danau

- lapisan

- lapisan

- Memimpin

- Dipimpin

- Panjang

- kurang

- Tingkat

- seumur hidup

- 'like'

- lin

- baris

- lokal

- tempat

- lokasi

- Panjang

- lama

- melihat

- tampak

- lepas

- Rendah

- menurunkan

- terbuat

- terutama

- utama

- pabrik

- banyak

- Massa

- cocok

- bahan

- max-width

- maksimum

- berarti

- berarti

- diukur

- pengukuran

- mekanisme

- logam

- metode

- Mikroskop

- Mikroskopi

- Tengah

- migrasi

- mencampur

- mobil

- mode

- model

- mode

- lebih

- paling

- kebanyakan

- gerakan

- beberapa

- kebutuhan

- jaringan

- tidak

- jumlah

- mengamati

- diamati

- memperoleh

- diperoleh

- terjadi

- terjadi

- of

- OHM

- on

- ONE

- hanya

- operasi

- or

- Lainnya

- di luar

- lebih

- secara keseluruhan

- paket

- pengemasan

- kertas

- parameter

- bagian

- path

- jalan

- persentase

- prestasi

- dilakukan

- gejala

- Fisika

- Pilar

- Nada

- berencana

- plato

- Kecerdasan Data Plato

- Data Plato

- Titik

- posisi

- mungkin

- potensi

- meramalkan

- disukai

- persiapan

- disajikan

- probabilitas

- proses

- disediakan

- diterbitkan

- kualitas

- agak

- R

- R & D

- cepat

- Penilaian

- perbandingan

- mencapai

- alasan

- alasan

- baru-baru ini

- pengurangan

- referensi

- tercermin

- mencerminkan

- dianggap

- mengenai

- terkait

- keandalan

- Dilaporkan

- wajib

- penelitian

- Perlawanan

- menghormati

- masing-masing

- mengakibatkan

- mengakibatkan

- Hasil

- Naik

- aturan

- sama

- puas

- Skalabilitas

- pemindaian

- skor

- Kedua

- Bagian

- Dijamin

- benih

- tampak

- memilih

- terpilih

- set

- beberapa

- parah

- kerasnya

- harus

- Menunjukkan

- menunjukkan

- menunjukkan

- ditunjukkan

- Pertunjukkan

- sisi

- Sinyal

- signifikan

- Silikon

- mirip

- simulasi

- sejak

- Ukuran

- lebih halus

- So

- larutan

- beberapa

- Sourcing

- Selatan

- tertentu

- Secara khusus

- Tahap

- magang

- standar

- statistik

- terus-menerus

- Langkah

- Tangga

- penyimpanan

- lurus

- tekanan

- struktur

- struktur

- studi

- Belajar

- seperti itu

- cukup

- meringkaskan

- Didukung

- Permukaan

- Sekitarnya

- tersangka

- Simposium

- sistem

- T

- tabel

- tim

- teknik

- Teknologi

- Teknologi

- istilah

- uji

- diuji

- pengujian

- tes

- dari

- terima kasih

- Terima kasih

- bahwa

- Grafik

- Sana.

- karena itu

- panas

- Ini

- ini

- tiga

- tiga dimensi

- Melalui

- waktu

- untuk

- terlalu

- puncak

- jejak

- Transaksi

- transfer

- mengangkut

- kecenderungan

- tv

- dua

- mengetik

- jenis

- khas

- bawah

- memahami

- unit

- sampai

- Amerika Serikat

- menggunakan

- gunakan case

- bekas

- berguna

- menggunakan

- biasanya

- sah

- nilai

- Nilai - Nilai

- berbagai

- kendaraan

- Kendaraan

- Lawan

- sangat

- View

- Tegangan

- W

- adalah

- webp

- BAIK

- adalah

- ketika

- sedangkan

- yang

- SIAPA

- sangat

- dengan

- dalam

- kata

- bengkel

- akan

- X

- zephyrnet.dll