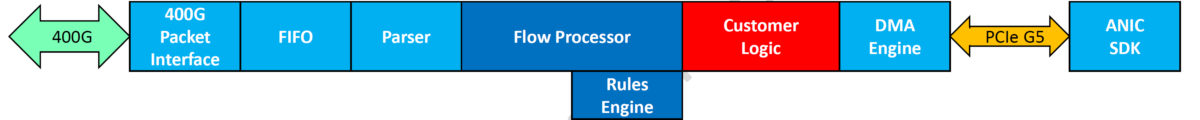

Mempertahankan transfer berkecepatan kabel 400 GbE hanyalah langkah pertama dalam mengelola lalu lintas perusahaan. Menambahkan pemfilteran berbasis aturan untuk menyaring paket secara real-time dapat menekan sebagian besar perangkat keras jaringan hingga mencapai titik puncaknya, sehingga memperlambat keseluruhan jaringan. Arsitek mencoba untuk menyebarkan beban ini, mendistribusikan manajemen lalu lintas cerdas dari firewall kelas atas dan peralatan lainnya menuju titik akhir di mana lalu lintas berasal – namun perangkat keras 400 GbE dengan mesin aturan terintegrasi tidak dapat diturunkan skalanya dengan mudah. Achronix memiliki solusi yang dibangun pada Speedster7t FPGA yang mengintegrasikan antarmuka paket 400 GbE, PCIe Gen 5, prosesor aliran dengan mesin aturan, dan ruang tersisa bagi logika pelanggan untuk membedakan desain SmartNIC 400 GbE.

Semua bagian yang dibutuhkan untuk SmartNIC 400 GbE dalam satu FPGA

Transceiver berkemampuan 400 GbE bermunculan di lebih dari satu FPGA kelas atas. Namun masalah pembuatan “pipa” yang sesuai pada FPGA sebesar 400 GbE sering kali dibiarkan sebagai latihan bagi pembaca. Dua proyek dalam Achronix, dengan bantuan dari akuisisi Accolade IP dan keahliannya pada bulan September 2022, telah memikirkan keseluruhan rantai IP dan bersatu untuk menghasilkan solusi lengkap di bawah bendera Achronix Network Infrastructure Code (ANIC).

“Kami rasa tidak ada orang yang memiliki 400 GbE dengan jenis pemrosesan aliran dan mesin aturan untuk titik akhir saat ini,” kata Scott Schweitzer, CISSP, Direktur Perencanaan Produk SmartNIC di Achronix. Hal ini dimulai dengan mengaktifkan teknologi – ANIC Shell, jalur pipa aliran paket Ethernet di RTL. Proyek ini dimulai dari teknologi 100 GbE dan PCIe Gen 3, yang berkonsentrasi pada FIFO, parsing, dan elemen DMA yang diperlukan untuk menjaga paket tetap bergerak dengan lancar. Di Speedster 7t, lebih dari separuh logika tetap tersedia untuk pelanggan.

![]()

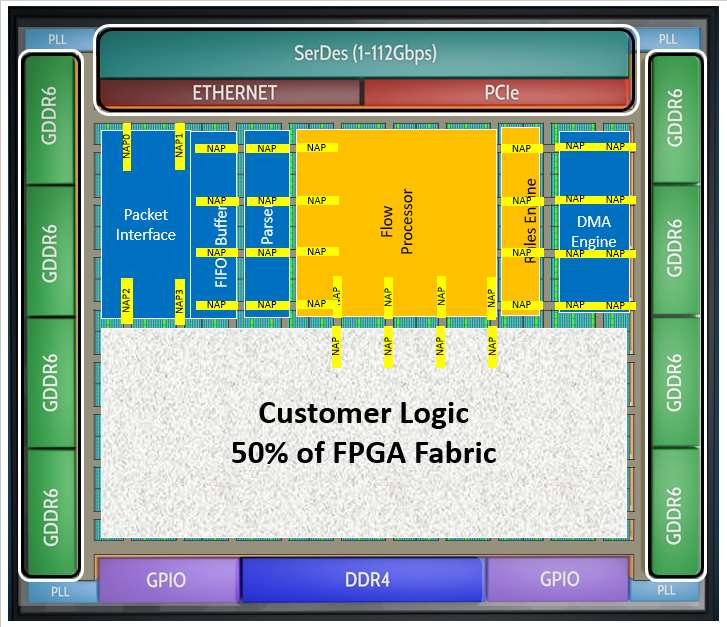

Berikutnya adalah peralihan dari shell ke ANIC lengkap untuk SmartNIC 400 GbE dengan prosesor aliran dan mesin aturan, masih dengan sekitar 50% logika Speedster7t yang tersisa.

Meningkatkan ANIC hingga 400 GbE mungkin terlihat mudah dari diagram ini, namun Schweitzer menunjukkan dua poin dalam rantai yang memerlukan perhatian khusus. “Untuk mendapatkan host pada 400 Gb, kami memerlukan setiap kinerja PCIe yang bisa kami dapatkan – 16 jalur PCIe 5 menjaga mesin DMA tetap terisi,” kata Schweitzer. “Kami juga membutuhkan memori yang lebih cepat untuk DMA dan FIFO, dan empat saluran GDDR6 di setiap sisi membawa kami ke sana.

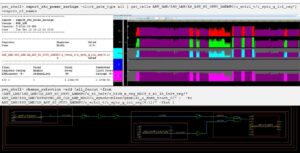

Divisualisasikan dalam jejak Speedster7t, ANIC terlihat seperti ini. Perhatikan bahwa ini semua adalah blok IP yang dioptimalkan dengan waktu tertutup yang terverifikasi dengan kecepatan.

Membuka kemungkinan baru untuk manajemen lalu lintas yang cerdas

ANIC membentuk landasan untuk pengembangan SmartNIC, memungkinkan pelanggan untuk menentukan kemampuan pembentukan paket dan manajemen lalu lintas dalam perangkat keras skala titik akhir yang berjalan pada kecepatan SmartNIC 400 GbE. Pelanggan mendapatkan waktu pemasaran yang lebih cepat dan kendali atas penyesuaian IP ANIC dan logika nilai tambah mereka. Menduplikasi atau menghilangkan duplikasi paket, menjalankan penyimpanan nilai kunci lokal, dan operasi lainnya dimungkinkan pada aliran paket menggunakan SmartNICs.

Keamanan jaringan meningkat dengan manajemen lalu lintas yang cerdas untuk penerimaan dan transmisi, namun SmartNIC secara tradisional menerapkan kebijakan hanya pada penerimaan. ANIC memungkinkan kebijakan diterapkan pada data yang diterima dan dikirimkan. “Katakanlah suatu malam, ada server aplikasi yang tiba-tiba menghasilkan volume lalu lintas yang tidak biasa pada jam 2 pagi ketika tidak ada orang yang bekerja,” Schweitzer memulai sebuah anekdot. “Dalam arsitektur jaringan perusahaan konvensional, peningkatan lalu lintas akan mencapai perangkat seperti firewall berkinerja tinggi, dan perangkat tersebut harus memiliki aturan yang tepat untuk menghentikan paket. Dengan memindahkan aturan yang sama ke SmartNIC 400 GbE dengan IP ANIC yang terpasang di server aplikasi, lalu lintas yang mencurigakan tidak akan pernah keluar, mencegah propagasi dan mengurangi beban pada jaringan.”

Kecerdasan buatan (AI) juga berperan besar dalam skala kemungkinan ANIC. Pemroses pembelajaran mesin (MLP) di Speedster7t dapat mempelajari dan menerapkan aturan ANIC dengan mengamati pola lalu lintas SmartNIC sebelum tim keamanan jaringan menyadari adanya kerentanan. Pembelajaran asli titik akhir juga dapat mendorong penyeimbang beban virtual, terdistribusi, dan cerdas, memindahkan lalu lintas ke platform lain jika pola lalu lintas terkonsentrasi muncul.

Achronix berupaya keras untuk memastikan FPGA Speedster7t berkinerja tinggi siap untuk aplikasi canggih di dunia nyata. SmartNIC 400 GbE hanyalah salah satu kemungkinan penggunaan Speedster7t – dan ini bagus karena hanya sedikit pendekatan lain yang dapat mencapai hasil yang sama. Kami berharap inovasi pelanggan akan mengambil alih dengan serangkaian solusi berbeda yang dibangun pada IP ANIC 400 GbE.

Pelajari lebih lanjut dalam siaran pers Achronix:

Achronix Mendorong Batasan Jaringan dengan 400 GbE dan PCIe Gen 5.0 untuk SmartNIC

Bagikan postingan ini melalui:

- Konten Bertenaga SEO & Distribusi PR. Dapatkan Amplifikasi Hari Ini.

- PlatoData.Jaringan Vertikal Generatif Ai. Berdayakan Diri Anda. Akses Di Sini.

- PlatoAiStream. Intelijen Web3. Pengetahuan Diperkuat. Akses Di Sini.

- PlatoESG. Otomotif / EV, Karbon, teknologi bersih, energi, Lingkungan Hidup, Tenaga surya, Penanganan limbah. Akses Di Sini.

- BlockOffset. Modernisasi Kepemilikan Offset Lingkungan. Akses Di Sini.

- Sumber: https://semiwiki.com/efpga/achronix/331586-400-gbe-smartnic-ip-sets-up-fpga-based-traffic-management/

- :memiliki

- :adalah

- :Di mana

- $NAIK

- 100

- 16

- 2022

- 32

- a

- Mencapai

- perolehan

- menambahkan

- maju

- AI

- Semua

- Membiarkan

- juga

- am

- an

- dan

- siapapun

- peralatan

- Aplikasi

- aplikasi

- terapan

- pendekatan

- arsitektur

- ADALAH

- sekitar

- AS

- At

- perhatian

- tersedia

- jauh

- kembali

- ayunan

- spanduk

- BE

- sebelum

- Bit

- Memblokir

- Blok

- kedua

- batas-batas

- Melanggar

- Bangunan

- dibangun di

- tapi

- by

- datang

- CAN

- kemampuan

- mampu

- kasus

- rantai

- saluran

- tertutup

- kode

- kedatangan

- lengkap

- Pekat

- kontrol

- konvensional

- bisa

- membuat

- pelanggan

- pelanggan

- kustomisasi

- data

- Tanggal

- menyebarkan

- desain

- Pengembangan

- membedakan

- dibedakan

- Kepala

- didistribusikan

- mendistribusikan

- DMA

- Dont

- turun

- mendorong

- setiap

- mudah

- Mudah

- usaha

- elemen

- muncul

- memungkinkan

- memungkinkan

- Titik akhir

- endpoint

- Mesin

- memastikan

- Enterprise

- Seluruh

- Setiap

- Latihan

- mengharapkan

- keahlian

- lebih cepat

- Fed

- beberapa

- penyaringan

- firewall

- firewall

- Pertama

- aliran

- Tapak

- Untuk

- bentuk

- Prinsip Dasar

- empat

- FPGA

- dari

- Mendapatkan

- Gen

- menghasilkan

- mendapatkan

- baik

- Setengah

- Perangkat keras

- Memiliki

- membantu

- High-End

- kinerja tinggi

- tuan rumah

- HTTPS

- if

- meningkatkan

- in

- Pada meningkat

- Infrastruktur

- Innovation

- terpadu

- Mengintegrasikan

- Intelijen

- Cerdas

- Antarmuka

- ke

- IP

- IT

- NYA

- jpg

- hanya

- hanya satu

- Menjaga

- besar

- BELAJAR

- pengetahuan

- meninggalkan

- 'like'

- memuat

- beban

- lokal

- logika

- melihat

- TERLIHAT

- mesin

- Mesin belajar

- pengelolaan

- pelaksana

- max-width

- Memori

- mungkin

- lebih

- paling

- bergerak

- dibutuhkan

- membutuhkan

- jaringan

- Keamanan jaringan

- jaringan

- tak pernah

- New

- malam

- Melihat..

- sekarang

- of

- sering

- on

- ONE

- hanya

- Operasi

- dioptimalkan

- or

- Lainnya

- di luar

- lebih

- paket

- pola

- prestasi

- potongan-potongan

- pipa saluran

- perencanaan

- Platform

- plato

- Kecerdasan Data Plato

- Data Plato

- Titik

- poin

- Kebijakan

- kemungkinan

- mungkin

- Pos

- pers

- Jumpa pers

- mencegah

- Masalah

- pengolahan

- Prosesor

- prosesor

- Produk

- proyek

- memprojeksikan

- perambatan

- tepat

- mendorong

- Puting

- jarak

- mencapai

- Pembaca

- siap

- nyata

- dunia nyata

- real-time

- menerima

- diterima

- mengurangi

- melepaskan

- sisa

- Hasil

- benar

- Kamar

- aturan

- berjalan

- sama

- mengatakan

- mengatakan

- Skala

- scott

- keamanan

- September

- set

- membentuk

- Kulit

- harus

- sisi

- Menyaring

- sejak

- Melambat

- lancar

- padat

- larutan

- Solusi

- tertentu

- kecepatan

- kecepatan

- penyebaran

- dimulai

- Langkah

- Masih

- berhenti

- toko

- stream

- tekanan

- cocok

- mencurigakan

- Mengambil

- tim

- Teknologi

- dari

- Grafik

- mereka

- Sana.

- Ini

- berpikir

- ini

- itu

- pikir

- Melalui

- waktu

- waktu

- untuk

- bersama

- terhadap

- secara tradisional

- lalu lintas

- transfer

- mengirimkan

- dua

- mengetik

- bawah

- luar biasa

- us

- menggunakan

- gunakan case

- menggunakan

- nilai tambah

- diverifikasi

- melalui

- maya

- volume

- kerentanan

- we

- ketika

- dengan

- dalam

- kerja

- akan

- zephyrnet.dll