Az integrált áramköri terminológiában a droop az áramkörben előforduló feszültségesés. Ez egy jól ismert jelenség, és a következő okok miatt fordulhat elő. A tápegység azon működési tartomány alá esik, amelyre a chipet tervezték, ami leesést eredményez. A vezető elemek több áramot vesznek fel, mint amennyire tervezték, ami leesést eredményez. Néha a tápegység jelinterferenciája vagy zaja feszültségingadozást is okozhat, ami leesést eredményezhet.

A leesések befolyásolhatják az áramkör működését. Az egyik ilyen hatás a chip csökkent teljesítménye, ami hosszabb feldolgozási időt eredményez. A következők azonban a súlyosabb és/vagy katasztrofálisabb hatások közül kerülnek ki. A chip több áramot vehet fel a teljesítmény szinten tartása érdekében, ami megnövekedett energiafogyasztáshoz és hőelvezetéshez vezet. Ez a chip élettartamának csökkenéséhez, súlyos esetekben pedig a chip teljes meghibásodásához vezethet a beállítási és tartási eltérések miatt. A leesések adatsérülést vagy hibákat is okozhatnak a kimenetben. Ez nagyon komoly probléma azoknál az alkalmazásoknál, amelyek a chip pontosságától és megbízhatóságától függenek.

A chipek és rendszerek tervezésénél természetesen komolyan figyelembe veszik a leesés jelenségét. A leállások csökkentésének leggyakoribb módszerei a tápegység szétkapcsolása, a feszültségszabályozás, az áramkör optimalizálása és a rendszerszintű energiagazdálkodás. A leesés-csökkentő megoldások tervezésekor gondosan figyelembe veszik azokat a feltételeket és működési környezetet, amelyben a chip fog működni.

Modern kor problémái

Ahogy az SoC-k összetettebbé válnak, a leállási problémák is meglehetősen bonyolulttá válhatnak. Az SoC tervezését a teljesítmény, az energia, a költség, a formai tényező stb. szempontjából optimalizálni kell, a leesés csökkentésére való optimalizálás mellett. Néha ezek az optimalizálási célok versenghetnek egymással, és ellentmondanak, és kompromisszumokat kell kötni. Például az SoC építészek növelhetik az üzemi feszültséget, növelve a tartalékot, hogy megkerüljék a helyi és globális lecsengést, de ez az emelkedés négyzetesen növeli a teljesítményt. Alternatív megoldásként a tervezők az óragenerációt alkalmazkodhatják a lecsengéshez, ami a teljesítményt az óragenerálás kapcsolási idejének függvényévé teszi.

Következésképpen az adatközpont számítási területén és az AI-térben található nagy SoC-k különösen érzékenyek a leesésre. Az ügyfelek munkaterhelése nagyon változatos és dinamikus, ami jelentős ingadozásokhoz vezet a váltási tevékenységben és az áramfelvételben. Természetesen a rendszerek nem engedhetik meg maguknak, hogy az elakadt problémákat figyelmen kívül hagyják. A chipek pontatlan kimenete vagy katasztrofális meghibásodása miatti potenciális felelősség túl magas a mai rendszerek és alkalmazások számára.

Lokalizált lemorzsolódási problémák

Az alkalmazás-specifikus gyorsítókat széles körben használják az általános célú processzorokkal párhuzamosan, hogy biztosítsák a mai igényes számítási környezetekben megkövetelt teljesítményt és energiahatékonyságot. De ezek a gyorsítók, valamint a magok növekvő száma és a munkaterhelések aszimmetrikus jellege növelik a helyi feszültségesések kockázatát. Ezek a lokalizált feszültségesések a kapcsolási aktivitás hirtelen megnövekedésének következményei, és átmeneti hibákat és potenciális küldetési mód meghibásodásokat okozhatnak.

Ha lokális leesés lép fel, a hatás dinamikus frekvenciaskálázással mérsékelhető. Ez az áramkör időzítésének programozható óra segítségével történő beállításával érhető el. A programozható óra lehetővé teszi az órafrekvencia és az időzítés dinamikus beállítását az áramkör aktuális működési feltételei alapján.

A Movellus megkönnyíti a helyi leállások kezelését

A Movellus, a vezető digitális rendszer-IP szolgáltató kifejlesztette az Aeonic Generate termékcsaládot a helyi leállások kezelésére. A Movellus Aeonic portfóliója adaptív órajel-megoldásokat kínál, amelyek gyorsan reagálnak a leállásra. A portfólió tartalmazza az adaptív órarendszert. Az építőelemek szintetizálható Verilogból készülnek, így alapvetően rugalmasak. A megoldások konfigurálhatók, szkennelhetők és folyamatban hordozhatók a fejlett SoC alkalmazások széles skálájához.

Az Aeonic Generate termékcsalád is lényegesen kisebb, mint a hagyományos analóg megoldások. Ennek eredményeként a tervezők a kívánt részletességgel példányosíthatják az IP-t anélkül, hogy ez jelentős hatást gyakorolna a területre. Ezen túlmenően, ahogy a tervek finomabb folyamatgeometriák felé haladnak, az Aeonic Generate terület folyamatosan méreteződik, így ideális megoldás a jövőbeli tervekhez.

Egy pár használati eset

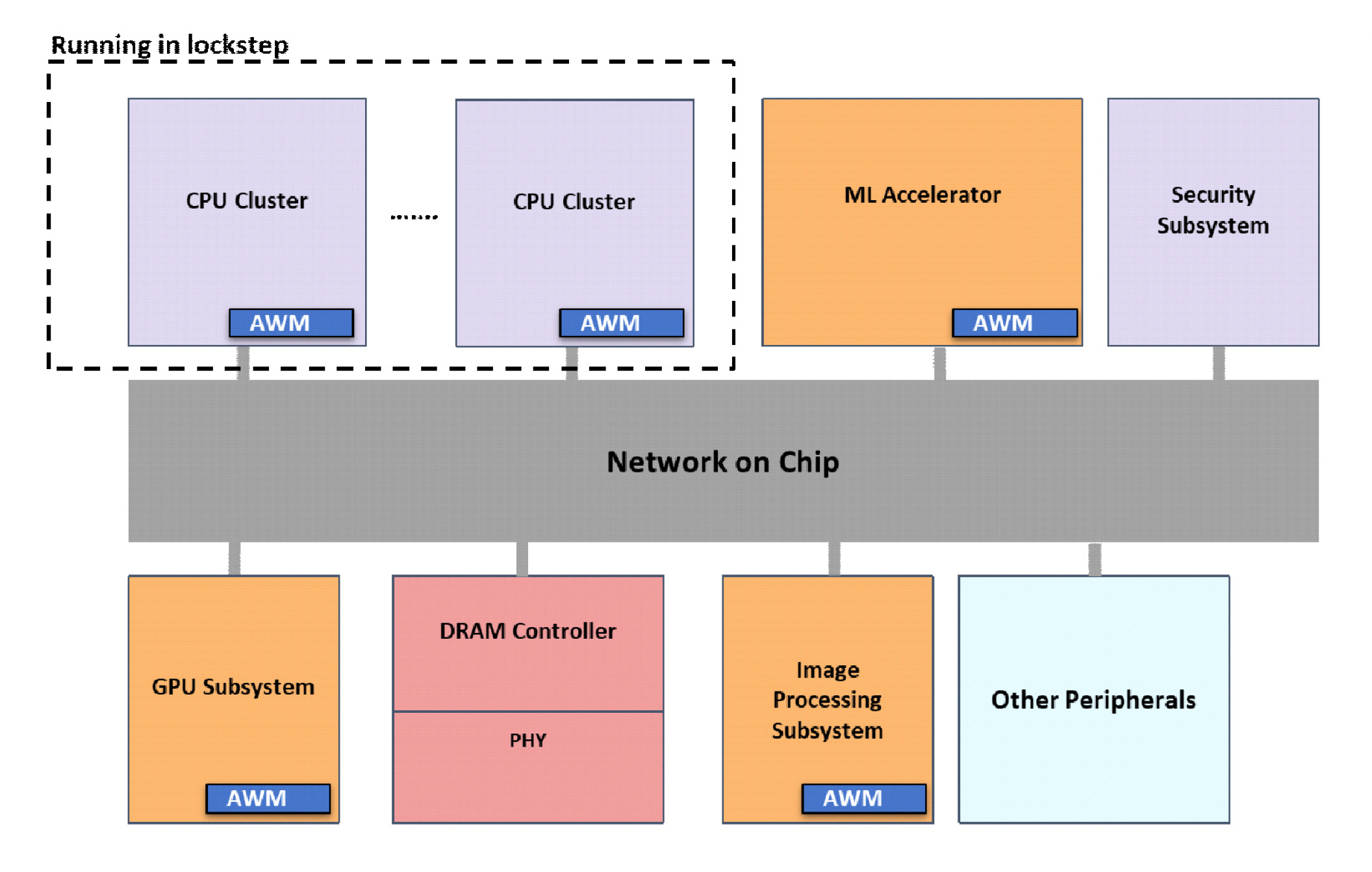

A Movellus következő ábrája egy ADAS processzor példáját mutatja be az Aeonic Generate AWM platformmal a honosított leállás támogatásához. Az építész az AWM modult egy alkalmazás-specifikus alblokkkal vagy gyorsítóval párosítaná, hogy öt órajel cikluson belül hibamentes és gyors frekvenciaváltásokkal reagáljon a munkaterhelés által vezérelt lokalizált leállásokra. Ez a megközelítés megbízható és hatékony megoldást kínál az ADAS, 5G és adatközponti hálózatok piacán jelentkező lokalizált leállások kihívásainak kezelésére.

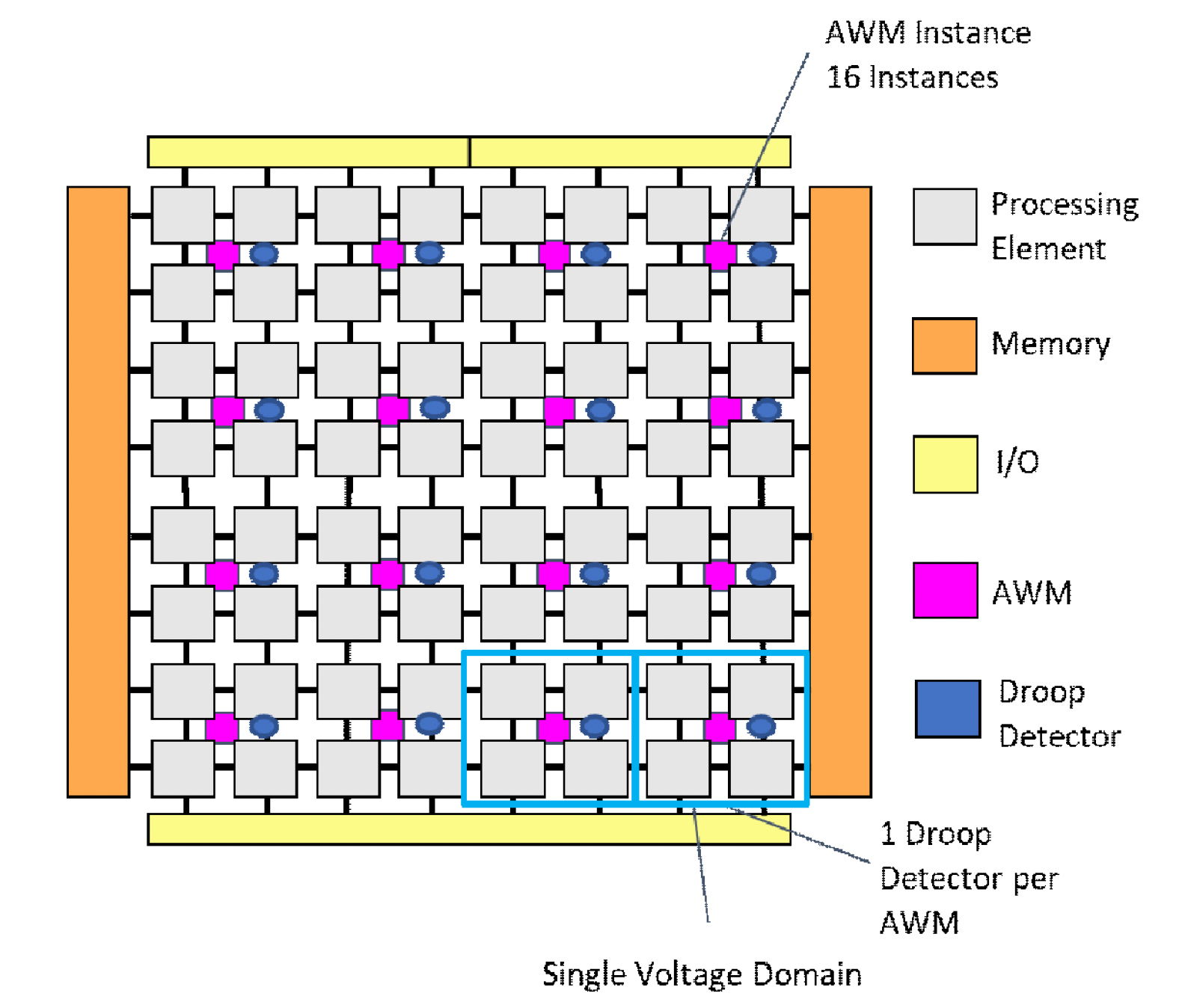

A Movellus következő ábrája egy példa architektúrát mutat be egy tengernyi processzor-SoC-re, amely Aeonic Generate-tel rendelkezik a lokalizált leállás támogatásához. Egy építész egy Aeonic Generate AWM modult párosítana a processzorfürthöz és a hozzá tartozó feszültségtartományhoz tartozó leállás-érzékelővel, hogy gyorsan reagálhasson a munkaterhelés által kiváltott lokalizált leállásokra. Ez lehetővé teszi a tervezők számára, hogy lokalizált és független leállási választ biztosítsanak a szomszédos processzorfürtök teljesítményének megváltoztatása nélkül.

Összegzésként

Az alkalmazás-specifikus gyorsítókat tartalmazó heterogén SoC-ekben lokalizált feszültségesések fordulhatnak elő. Ezek az elakadások időzítési hibákhoz, átmeneti hibákhoz és küldetési üzemmódbeli hibákhoz vezethetnek az ADAS-ban, az adatközponti hálózatokban és az 5G-alkalmazásokban. A rendszertervezők alkalmazkodó órajelet alkalmazhatnak, hogy reagáljanak ezekre az elakadásokra és mérsékeljék a hatást.

A Movellus™ Aeonic Generate Adaptive Workload Module (AWM) nagy teljesítményű óragenerációs IP-termékek családja az Aeonic Intelligent Clock Network™ architektúra részét képezi. További információkért lásd a Movellus' Aeonic Generate™ AWM oldal.

Is Read:

A nagy léptékű szinkron órajeles tartományok előnyei az AI chip-tervezésben

Itt az ideje az intelligens óra hálózatoknak

A teljesítmény, a teljesítmény és a terület (PPA) előnyei az intelligens órahálózatokon keresztül

Oszd meg ezt a bejegyzést ezen keresztül:

- SEO által támogatott tartalom és PR terjesztés. Erősödjön még ma.

- Platoblockchain. Web3 metaverzum intelligencia. Felerősített tudás. Hozzáférés itt.

- Forrás: https://semiwiki.com/ip/326488-adaptive-clock-technology-for-real-time-droop-response/

- :is

- 5G

- a

- gázpedál

- gyorsítók

- pontosság

- elért

- tevékenység

- alkalmazkodni

- ADAs

- mellett

- Ezen kívül

- cím

- címzés

- Beállított

- fejlett

- AI

- lehetővé teszi, hogy

- és a

- alkalmazások

- megközelítés

- építészet

- VANNAK

- TERÜLET

- AS

- társult

- At

- alapján

- BE

- válik

- lent

- Előnyök

- Blokk

- Blocks

- Épület

- épült

- by

- TUD

- Kaphat

- nem tud

- gondosan

- esetek

- végzetes

- Okoz

- Központ

- kihívások

- csip

- játékpénz

- óra

- Fürt

- Közös

- versenyez

- teljes

- bonyolult

- Kiszámít

- számítástechnika

- Körülmények

- megfontolás

- figyelembe vett

- fogyasztás

- tovább

- vesztegetés

- Költség

- tudott

- Számláló

- Pár

- tanfolyam

- Jelenlegi

- vevő

- ciklusok

- dátum

- Adatközpont

- Datacenter

- nap

- szállít

- igényes

- Design

- tervezett

- tervezők

- tervezés

- tervek

- fejlett

- digitális

- megosztott

- számos

- domain

- domainek

- húzott

- Csepp

- cseppek

- dinamikus

- dinamikusan

- minden

- hatékonyság

- hatékony

- elemek

- Környezet

- környezetek

- hibák

- stb.

- példa

- Kudarc

- Vízesés

- család

- Ábra

- rugalmas

- ingadozások

- következő

- A

- forma

- Frekvencia

- ból ből

- funkció

- jövő

- Általános rendeltetésű

- generál

- generáció

- kap

- Globális

- Go

- Célok

- történik

- megtörténik

- Legyen

- Magas

- nagy teljesítményű

- tart

- HTTPS

- ideális

- Hatás

- Hatások

- végre

- in

- pontatlan

- magában foglalja a

- Növelje

- <p></p>

- Növeli

- növekvő

- független

- információ

- integrált

- integráció

- Intelligens

- önmagában

- IP

- kérdés

- kérdések

- IT

- nagy

- nagyarányú

- vezet

- vezető

- szint

- felelősség

- élet

- helyi

- hosszabb

- készült

- fenntartása

- KÉSZÍT

- Gyártás

- vezetés

- Margó

- piacok

- max-width

- mód

- Enyhít

- enyhítő

- enyhítés

- modul

- Modulok

- több

- a legtöbb

- mozog

- Természet

- igények

- hálózat

- hálózatba

- Zaj

- nevezetesen

- szám

- of

- Ajánlatok

- on

- ONE

- üzemeltetési

- Művelet

- optimalizálás

- optimalizált

- optimalizálása

- Más

- teljesítmény

- rész

- teljesítmény

- előadó

- jelenség

- emelvény

- Plató

- Platón adatintelligencia

- PlatoData

- portfolió

- állás

- potenciális

- hatalom

- Tápegység

- folyamat

- feldolgozás

- Processzor

- processzorok

- Termékek

- ellátó

- biztosít

- emel

- hatótávolság

- gyors

- gyorsan

- Olvass

- real-time

- miatt

- Csökkent

- Szabályozás

- megbízhatóság

- megbízható

- kötelező

- Reagálni

- válasz

- eredményez

- kapott

- Emelkedik

- Kockázat

- futás

- Skála

- skálázás

- SEA

- súlyos

- felépítés

- szigorú

- Műszakok

- Műsorok

- Jel

- jelentős

- jelentősen

- kisebb

- okos

- megoldások

- Megoldások

- néhány

- Hely

- ilyen

- hirtelen

- kínálat

- támogatás

- fogékony

- rendszer

- Systems

- Tandem

- Technológia

- terminológia

- hogy

- A

- A terület

- azok

- Őket

- Ezek

- Keresztül

- idő

- alkalommal

- időzítés

- nak nek

- mai

- is

- hagyományos

- használ

- nagyon változatos

- keresztül

- Feszültség

- JÓL

- jól ismert

- ami

- széles

- Széleskörű

- széles körben

- lesz

- val vel

- belül

- nélkül

- lenne

- zephyrnet