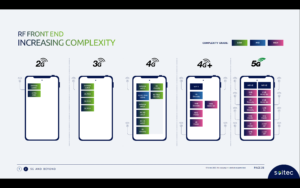

Dans la marche vers des systèmes plus performants, plus rapides, plus petits et à moindre consommation, la loi de Moore a donné aux logiciels un tour de passe-passe pendant plus de 30 ans uniquement sur l'évolution des processus de semi-conducteurs. Le matériel informatique a fourni chaque année des mesures de performances/surface/puissance améliorées, permettant aux logiciels de gagner en complexité et d'offrir plus de fonctionnalités sans inconvénients. Ensuite, les victoires faciles sont devenues moins faciles. Des processus plus avancés ont continué à fournir un nombre de portes plus élevé par unité de surface, mais les gains en performances et en puissance ont commencé à se stabiliser. Puisque nos attentes en matière d’innovation ne se sont pas arrêtées, les progrès de l’architecture matérielle sont devenus plus importants pour combler le vide.

Facteurs favorisant l’augmentation du nombre de cœurs

Une première étape dans cette direction a utilisé des processeurs multicœurs pour accélérer le débit total en threadant ou en virtualisant un mélange de tâches simultanées sur les cœurs, réduisant ainsi la consommation si nécessaire en mettant au ralenti ou en mettant hors tension les cœurs inactifs. Le multicœur est aujourd'hui la norme et une tendance au multicœur (encore plus de processeurs sur une puce) est déjà évidente dans les options d'instance de serveur disponibles sur les plates-formes cloud d'AWS, Azure, Alibaba et autres.

Les architectures multicœurs constituent un pas en avant, mais le parallélisme via les clusters de processeurs est grossier et a ses propres limites de performances et de puissance, grâce à la loi d'Amdahl. Les architectures sont devenues plus hétérogènes, ajoutant des accélérateurs pour l'image, l'audio et d'autres besoins spécialisés. Les accélérateurs d’IA ont également poussé le parallélisme à granularité fine, en passant aux réseaux systoliques et à d’autres techniques spécifiques à un domaine. Ce qui fonctionnait plutôt bien jusqu'à ce que ChatGPT apparaisse avec 175 milliards de paramètres, GPT-3 évoluant vers GPT-4 avec 100 XNUMX milliards de paramètres – des ordres de grandeur plus complexes que les systèmes d'IA d'aujourd'hui – forçant des fonctionnalités d'accélération encore plus spécialisées au sein des accélérateurs d'IA.

Sur un autre front, les systèmes multicapteurs dans les applications automobiles s'intègrent désormais dans des SoC uniques pour une meilleure sensibilisation à l'environnement et un meilleur PPA. Ici, de nouveaux niveaux d'autonomie dans l'automobile dépendent de la fusion des entrées de plusieurs types de capteurs au sein d'un seul appareil, dans des sous-systèmes se répliquant par 2X, 4X ou 8X.

Selon Michał Siwinski (CMO chez Arteris), un échantillon de discussions sur un mois avec plusieurs équipes de conception sur un large éventail d'applications suggère que ces équipes se tournent activement vers un nombre de cœurs plus élevé pour atteindre leurs objectifs en matière de capacité, de performances et de puissance. Il me dit qu’ils voient également cette tendance s’accélérer. Les avancées en matière de processus contribuent toujours au nombre de portes SoC, mais la responsabilité d'atteindre les objectifs de performances et de puissance est désormais fermement entre les mains des architectes.

Plus de cœurs, plus d'interconnexion

Plus de cœurs sur une puce impliquent plus de connexions de données entre ces cœurs. Au sein d'un accélérateur entre des éléments de traitement voisins, vers le cache local, vers des accélérateurs pour une matrice clairsemée et d'autres traitements spécialisés. Ajoutez une connectivité hiérarchique entre les tuiles accélératrices et les bus au niveau du système. Ajoutez une connectivité pour le stockage du poids sur puce, la décompression, la diffusion, la collecte et la recompression. Ajoutez la connectivité HBM pour le cache fonctionnel. Ajoutez un moteur de fusion si nécessaire.

Le cluster de contrôle basé sur le processeur doit se connecter à chacun de ces sous-systèmes répliqués et à toutes les fonctions habituelles : codecs, gestion de la mémoire, îlot de sécurité et racine de confiance le cas échéant, UCIe en cas d'implémentation multi-chiplets, PCIe pour les E/S à large bande passante. , et Ethernet ou fibre pour la mise en réseau.

Cela représente beaucoup d’interconnexions, avec des conséquences directes sur la commercialisation des produits. Dans les processus inférieurs à 16 nm, l'infrastructure NoC contribue désormais à hauteur de 10 à 12 % en superficie. Plus important encore, en tant qu'autoroute de communication entre les cœurs, elle peut avoir un impact significatif sur les performances et la puissance. Il existe un réel danger qu'une mise en œuvre sous-optimale gaspille les performances et les gains de puissance attendus de l'architecture, ou pire encore, qu'elle entraîne de nombreuses boucles de reconception pour converger. Pourtant, trouver une bonne implémentation dans un plan de SoC complexe dépend toujours de lentes optimisations par essais et erreurs dans des calendriers de conception déjà serrés. Nous devons passer à une conception NoC physiquement consciente, pour garantir des performances complètes et une prise en charge de la puissance des hiérarchies NoC complexes et nous devons accélérer ces optimisations.

Les conceptions NoC physiquement conscientes maintiennent la loi de Moore sur la bonne voie

La loi de Moore n’est peut-être pas morte, mais les progrès en matière de performances et de puissance proviennent aujourd’hui de l’architecture et de l’interconnexion des NoC plutôt que des processus. L'architecture pousse davantage de cœurs d'accélérateurs, davantage d'accélérateurs au sein des accélérateurs et davantage de réplication de sous-systèmes sur puce. Tout cela augmente la complexité de l’interconnexion sur puce. À mesure que les conceptions augmentent le nombre de cœurs et évoluent vers des géométries de traitement à 16 nm et moins, les nombreuses interconnexions NoC couvrant le SoC et ses sous-systèmes ne peuvent prendre en charge tout le potentiel de ces conceptions complexes que si elles sont mises en œuvre de manière optimale dans le respect des contraintes physiques et temporelles – via un réseau physiquement conscient. sur la conception des puces.

Si ces tendances vous inquiètent également, vous voudrez peut-être en savoir plus sur la technologie Arteris FlexNoC 5 IP. ICI.

Partagez cet article via:

- Contenu propulsé par le référencement et distribution de relations publiques. Soyez amplifié aujourd'hui.

- Platoblockchain. Intelligence métaverse Web3. Connaissance Amplifiée. Accéder ici.

- La source: https://semiwiki.com/artificial-intelligence/326727-interconnect-under-the-spotlight-as-core-counts-accelerate/

- :est

- $UP

- 100

- a

- Qui sommes-nous

- accélérer

- accélérer

- accélération

- accélérateur

- accélérateurs

- à travers

- activement

- Avancée

- avances

- à opposer à

- AI

- Systèmes d'IA

- Alibaba

- Tous

- Permettre

- déjà

- ainsi que

- paru

- applications

- approprié

- architecture

- SONT

- Réservé

- AS

- At

- acoustique

- l'automobile

- disponibles

- AWS

- Azure

- Bande passante

- BE

- devenez

- ci-dessous

- jusqu'à XNUMX fois

- Milliards

- diffusion

- Bus

- by

- cachette

- CAN

- capable

- ChatGPT

- puce

- le cloud

- Grappe

- CMO

- comment

- Communication

- complexe

- complexité

- calcul

- concurrent

- NOUS CONTACTER

- Connexions

- Connectivité

- Conséquences

- contraintes

- a continué

- des bactéries

- converger

- Core

- Processeur

- DANGER

- données

- parfaite

- livrer

- livré

- dépend

- Conception

- Avec nos Bagues Halo

- dispositif

- différent

- direction

- discussions

- down

- inconvénients

- chacun

- "Early Bird"

- éléments

- Moteur

- Environment

- Pourtant, la

- Chaque

- évolution

- évolution

- Développer vous

- attentes

- attendu

- plus rapide

- Fonctionnalités:

- trouver

- fermement

- Pour

- Avant

- Test d'anglais

- de

- avant

- plein

- fonctions

- la fusion

- Gains

- Objectifs

- Bien

- guarantir

- Maniabilité

- Mains

- Matériel

- Vous avez

- aider

- ici

- Haute

- augmentation

- Autoroute

- HTTPS

- image

- Impact

- la mise en oeuvre

- mis en œuvre

- important

- amélioré

- in

- inactif

- Améliore

- croissant

- Infrastructure

- Innovation

- instance

- Intégration

- IP

- île

- IT

- SES

- saut

- Droit applicable et juridiction compétente

- APPRENTISSAGE

- Niveau

- niveaux

- limites

- locales

- Lot

- faire

- gestion

- Mars

- Matrice

- largeur maximale

- Découvrez

- réunion

- Mémoire

- Métrique

- pourrait

- Mois

- PLUS

- Bougez

- en mouvement

- plusieurs

- Besoin

- nécessaire

- Besoins

- réseau et

- de mise en réseau

- Nouveauté

- nombreux

- of

- on

- Options

- passer commande

- Autre

- Autres

- propre

- paramètres

- performant

- Physique

- Physiquement

- Plateformes

- Platon

- Intelligence des données Platon

- PlatonDonnées

- Post

- défaillances

- power

- Alimentation

- assez

- processus

- les process

- traitement

- Produit

- purement

- Poussé

- Poussant

- gamme

- plutôt

- réal

- réduire

- répliquées

- réplication

- responsabilité

- résultat

- Rouler

- racine

- Sécurité

- semi-conducteur

- significative

- depuis

- unique

- mou

- lent

- faibles

- So

- Logiciels

- matrice clairsemée

- spécialisé

- Spotlight

- Standard

- j'ai commencé

- étapes

- Encore

- Arrêter

- storage

- Suggère

- Support

- combustion propre

- Système

- tâches

- équipes

- techniques

- Technologie

- raconte

- qui

- Les

- Ces

- Avec

- débit

- timing

- à

- aujourd'hui

- aujourd'hui

- Total

- Trend

- Trends

- Billion

- La confiance

- Tournant

- types

- sous

- unité

- via

- poids

- WELL

- qui

- large

- Large gamme

- sera

- Gagne

- comprenant

- dans les

- de travail

- an

- années

- zéphyrnet