Au cours de la décennie 2010, les avantages de la loi de Moore ont commencé à s'effondrer. La loi de Moore stipulait que la densité des transistors doublait tous les deux ans, le coût du calcul diminuerait d'un montant correspondant de 50 %. Le changement dans la loi de Moore est dû à la complexité accrue de la conception et à l'évolution de la structure des transistors, des dispositifs planaires aux Finfets. Les Finfets ont besoin de plusieurs motifs pour la lithographie afin d'atteindre des dimensions de dispositif inférieures à 20 nm.

Au début de cette décennie, les besoins informatiques ont explosé, principalement en raison de la prolifération des centres de données et de la quantité de données générées et traitées. En fait, l’adoption de l’intelligence artificielle (IA) et de techniques telles que l’apprentissage automatique (ML) est désormais utilisée pour traiter un nombre toujours croissant de données et a conduit les serveurs à augmenter considérablement leur capacité de calcul.

Les serveurs ont ajouté beaucoup plus de cœurs de processeur, ont intégré des GPU plus grands utilisés exclusivement pour le ML, qui ne sont plus utilisés pour les graphiques, et ont intégré des accélérateurs d'IA ASIC personnalisés ou un traitement d'IA complémentaire basé sur FPGA. Les premières conceptions de puces d'IA ont été mises en œuvre à l'aide de SoC monolithiques plus grands, certains d'entre eux atteignant la limite de taille imposée par le réticule, environ 700 mm.2.

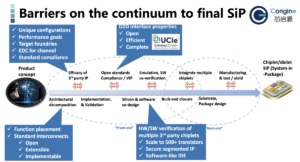

À ce stade, la désagrégation en un SoC plus petit ainsi que divers chipsets de calcul et d’E/S semble être la bonne solution. Plusieurs fabricants de puces, comme Intel, AMD ou Xilinx, ont choisi cette option pour les produits entrant en production. Dans l'excellent livre blanc du Linley Group, « Chiplets Gain Rapid Adoption: Why Big Chips Are Getting Small », il a été démontré que cette option entraîne de meilleurs coûts par rapport aux SoC monolithiques, en raison de l'impact sur le rendement d'un SoC plus grand.

L'impact majeur de cette tendance sur les fournisseurs IP concerne principalement les fonctions d'interconnexion utilisées pour relier les SoC et les chipsets. À ce stade (T3 2021), plusieurs protocoles sont utilisés, l’industrie essayant d’élaborer des normes formalisées pour beaucoup d’entre eux.

Les principales normes D2D actuelles incluent i) Advanced Interface Bus (AIB, AIB2) initialement défini par Intel, et offre désormais une utilisation libre de droits, ii) High Bandwidth Memory (HBM) où les puces DRAM sont empilées les unes sur les autres au-dessus d'un interposeur en silicium. et sont connectés à l'aide de TSV, iii) le sous-groupe Open Domain-Specific Architecture (ODSA), un groupe industriel, a défini deux autres interfaces, Bunch of Wires (BoW) et OpenHBI.

La conception hétérogène des chiplets nous permet de cibler différentes applications ou segments de marché en modifiant ou en ajoutant uniquement les chiplets pertinents tout en gardant le reste du système inchangé. De nouveaux développements pourraient être lancés plus rapidement sur le marché, avec des investissements nettement inférieurs, car la refonte n'impactera que le substrat du boîtier utilisé pour loger les chipsets.

Par exemple, le chipset de calcul peut être repensé de TSMC 5 nm à TSMC 3 nm pour intégrer un cache L1 plus grand ou des cœurs de processeur plus performants, tout en gardant le reste du système inchangé. À l’opposé du spectre, seul le chipset intégrant SerDes peut être repensé pour des débits plus rapides sur de nouveaux nœuds de processus offrant plus de bande passante IO pour un meilleur positionnement sur le marché.

Intel PVC est un parfait exemple d'intégration hétérogène (divers chipsets fonctionnels, CPU, switch, etc.) que l'on pourrait appeler intégration verticale, lorsqu'un même fabricant de puces possède les différents composants du chiplet (à l'exception des dispositifs de mémoire).

Les fabricants de puces développant des SoC pour des applications haut de gamme, telles que le HPC, les centres de données, l'IA ou les réseaux, seront probablement les premiers à adopter les architectures chiplet. Des fonctions spécifiques, comme les SRAM pour un cache L3 plus grand, ou les accélérateurs d'IA, les normes Ethernet, PCIe ou CXL devraient être les premières interfaces candidates pour les conceptions de chipsets.

Lorsque ces premiers utilisateurs auront démontré la validité des chipsets hétérogènes exploitant plusieurs modèles commerciaux différents, et évidemment la faisabilité de la fabrication pour les tests et le conditionnement, cela créera un écosystème essentiel pour prendre en charge cette nouvelle technologie. À ce stade, nous pouvons nous attendre à une adoption plus large sur le marché, et pas seulement pour les applications hautes performances.

On pourrait imaginer que des produits hétérogènes puissent aller plus loin, si un fabricant de puces lançait sur le marché un système composé de différents chipsets ciblant les fonctionnalités de calcul et d'E/S. Cette approche rend obligatoire la convergence sur un protocole D2D, car un fournisseur IP proposant des chipsets avec un protocole D2D interne n'est pas attractif pour l'industrie.

Une analogie avec cela est la construction de SoC dans les années 2000, où les entreprises de semi-conducteurs ont commencé à intégrer diverses IP de conception provenant de différentes sources. Les fournisseurs de puces IP des années 2000 deviendront inévitablement les fournisseurs de chipsets des années 2020. Pour certaines fonctions, comme les SerDes avancés ou les protocoles complexes, comme PCIe, Ethernet ou CXL, les fournisseurs IP disposent du meilleur savoir-faire pour les implémenter sur silicium.

Pour les conceptions IP complexes, même si une vérification par simulation a été effectuée avant l'expédition aux clients, les fournisseurs doivent valider l'IP sur silicium pour garantir les performances. Pour l'IP numérique, la fonction peut être implémentée dans FPGA car elle est plus rapide et beaucoup moins coûteuse que la fabrication d'une puce de test. Pour les IP à signaux mixtes, comme un PHY basé sur SerDes, les fournisseurs sélectionnent l'option Test Chip (TC) permettant au silicium de caractériser l'IP dans le silicium avant l'expédition au client.

Même si un chiplet n’est pas simplement un TC, car il sera largement testé et qualifié avant d’être utilisé sur le terrain, la quantité de travail supplémentaire à effectuer par le fournisseur pour développer un chiplet de production est bien moindre. En d’autres termes, le fournisseur IP est le mieux placé pour publier rapidement un chipset construit à partir de sa propre IP, offrir le meilleur TTM possible et minimiser les risques.

Le modèle commercial d'intégration hétérogène est en faveur de divers chipsets fabriqués par le fournisseur IP concerné (par exemple, ARM pour les chipsets de processeur basés sur ARM, Si-Five pour les chipsets de calcul basés sur Risc-V et Alphawave pour les chipsets SerDes à haute vitesse) puisque ils sont propriétaires de la propriété intellectuelle de conception.

Rien de tout cela n’empêche les fabricants de puces de concevoir leurs propres chipsets et de créer des IP de conception complexe pour protéger leurs architectures uniques ou mettre en œuvre des interconnexions faites maison. À l'instar de la propriété intellectuelle de conception de SoC dans les années 2000, la décision d'acheter ou de fabriquer des chipsets sera pondérée entre la protection des compétences de base et l'approvisionnement en fonctions non différenciées.

Nous avons constaté que la croissance historique et moderne de l'activité Design IP depuis les années 2000 a été soutenue par l'adoption continue de l'approvisionnement externe. Les deux modèles coexisteront (chiplet conçu en interne ou par un fournisseur IP), mais l'histoire a montré que la décision d'achat finit par prendre le pas sur la marque.

Il existe désormais un consensus dans l'industrie selon lequel une focalisation maniaque sur la réalisation de la loi de Moore n'est plus valable pour les nœuds technologiques avancés, par exemple. 7 nm et moins. L'intégration des puces se poursuit, avec davantage de transistors ajoutés par mm² à chaque nouveau nœud technologique. Cependant, le coût par transistor augmente également à chaque nouveau nœud.

La technologie Chiplet est une initiative clé pour favoriser une intégration accrue du SoC principal tout en utilisant des nœuds plus anciens pour d'autres fonctionnalités. Cette stratégie hybride réduit à la fois le coût et le risque de conception associés à l'intégration d'autres IP de conception directement sur le SoC principal.

IPnest estime que cette tendance aura deux effets principaux dans le secteur des interfaces IP : l'un sera la forte croissance des revenus IP D2D prochainement (2021-2025) et l'autre sera la création d'un marché de chipsets hétérogènes pour augmenter le silicium haut de gamme. Marché de la propriété intellectuelle.

Ce marché devrait être constitué de fonctions de protocoles complexes comme PCIe, CXL ou Ethernet. Les fournisseurs IP proposant une interface IP intégrée dans les SoC d'E/S (USB, HDMI, DP, MIPI, etc.) peuvent décider de fournir des chipsets d'E/S à la place.

Les autres catégories IP impactées par cette révolution seront les IP des fournisseurs de compilateurs de mémoire SRAM, pour le cache L3. Par nature, la taille du cache devrait varier en fonction du processeur. Néanmoins, la conception d'un chiplet de cache L3 peut être un moyen pour le fournisseur IP d'augmenter les revenus de la conception IP en proposant un nouveau type de produit.

De plus, la catégorie IP NVM peut être impactée positivement, car les IP NVM ne sont plus intégrées dans les SoC conçus sur des nœuds de processus avancés. Ce serait un moyen pour les fournisseurs IP NVM de générer de nouvelles affaires en proposant des chipsets.

Nous pensons que les chipsets FPGA et accélérateurs d'IA constitueront une nouvelle source de revenus pour les fabricants de puces ASSP, mais nous ne pensons pas qu'ils puissent être strictement classés parmi les fournisseurs IP.

Si les fournisseurs d'Interface IP seront des acteurs majeurs de cette révolution du silicium, les fonderies de silicium s'occupant des nœuds les plus avancés comme TSMC et Samsung joueront également un rôle clé. Nous ne pensons pas que les fonderies concevront des chipsets, mais elles pourraient prendre la décision de soutenir les fournisseurs IP et les pousser à concevoir des chipsets à utiliser avec les SoC en 3 nm, comme elles le font aujourd'hui lorsqu'elles aident les fournisseurs IP avancés à commercialiser leurs SerDes haut de gamme. comme IP dur en 7 nm et 5 nm.

La récente transition d'Intel vers 3rd les fonderies tierces devraient également tirer parti des adresses IP tierces, ainsi que de l’adoption de chipsets hétérogènes par les poids lourds des semi-conducteurs. Dans ce cas, nul doute que les Hyperscalaires comme Microsoft, Amazon et Google adopteront également des architectures chiplet… s'ils ne précèdent pas Intel dans l'adoption des chiplets.

By Eric Estève (PhD.) Analyste, Propriétaire IPnest

Partagez cet article via: Source : https://semiwiki.com/semiconductor-services/ipnest/303790-chiplet-are-you-ready-for-next-semiconductor-revolution/

- 2021

- accélérateur

- accélérateurs

- Adoption

- Technologie avancée

- AI

- Permettre

- Amazon

- AMD

- analyste

- applications

- architecture

- BRAS

- intelligence artificielle

- Intelligence artificielle (AI)

- ase

- LES MEILLEURS

- construire

- Développement

- Bouquet

- bus

- la performance des entreprises

- modèle d'affaires

- acheter

- Appelez-nous

- Compétences

- Change

- puce

- chips

- Venir

- Sociétés

- calcul

- informatique

- Consensus

- Costs

- Clients

- données

- livrer

- Conception

- développer

- Compatibles

- numérique

- "Early Bird"

- adopteurs précoces

- risque numérique

- etc

- évolution

- Prénom

- Focus

- fpga

- gratuitement ici

- fonction

- GPU

- Réservation de groupe

- Croissance

- Croissance

- Haute

- Histoire

- Villa

- HTTPS

- Hybride

- Impact

- Améliore

- industrie

- initiative

- l'intégration

- Intel

- Intelligence

- un investissement

- IP

- IT

- en gardant

- ACTIVITES

- lancer

- Droit applicable et juridiction compétente

- conduisant

- apprentissage

- LED

- Levier

- LINK

- machine learning

- majeur

- fabricant

- Fabrication

- fabrication

- Marché

- Microsoft

- ML

- modèle

- de mise en réseau

- nouveau produit

- nœuds

- code

- offrant

- ouvert

- Option

- Autre

- propriétaire

- l'emballage

- Papier

- performant

- Produit

- Vidéo

- Produits

- protéger

- protection

- Tarifs

- reconcevoir

- REST

- Analyse

- Courir

- Samsung

- semi-conducteur

- Livraison

- simulation

- Taille

- Normes

- de Marketing

- Support

- Interrupteur

- combustion propre

- Target

- techniques

- Technologie

- tester

- top

- us

- usb

- fournisseurs

- Vérification

- papier blanc

- des mots

- activités principales

- années

- Rendement