Plus tôt, j'ai blogué sur Vérification fonctionnelle IC et ASIC, il est donc temps aujourd'hui de compléter cela avec l'état de la vérification fonctionnelle du FPGA. Le Wilson Research Group compile un rapport FPGA tous les deux ans depuis 2018, c'est donc la troisième fois qu'il se concentre sur ce segment de conception. À 5.8 milliards de dollars, le marché des FPGA est considérable et devrait atteindre 8.1 milliards de dollars d'ici 2025. Les FPGA ont débuté en 1984 avec une capacité de porte limitée et se sont maintenant développés pour inclure des millions de portes, de processeurs et de protocoles de données standardisés.

Les applications à faible volume bénéficient du NRE des dispositifs FPGA, et les ingénieurs peuvent rapidement prototyper leurs conceptions en vérifiant et en validant rapidement. Les FPGA incluent désormais des processeurs, tels que : Xilinx Zynq UltraSCALE, Intel Stratix, Micropuce SmartFusion. Parmi les 980 participants à l'étude de vérification fonctionnelle, les styles de conception FPGA et SoC programmable FPGA sont les plus populaires.

Comme la taille des FPGA a récemment augmenté, la probabilité d'une version de production sans bogue est tombée à seulement 17 %, ce qui est encore pire que les 30 % de projets IC et ASIC pour un premier silicium correct. De toute évidence, nous avons besoin d'une meilleure vérification fonctionnelle pour les systèmes FPGA complexes.

Les types de bugs trouvés en production se répartissent en plusieurs catégories :

- 53% - Logique ou Fonctionnel

- 31 % – Micrologiciel

- 29% - Pointage

- 28% - Timing, chemin trop lent

- 21 % - Timing, chemin trop rapide

- 18 % - Interface à signaux mixtes

- 9% - Fonction de sécurité

- 8% - Fonction de sécurité

En zoomant sur la plus grande catégorie de pannes, logiques ou fonctionnelles, il existe cinq causes profondes.

Les projets FGPA ne se terminaient généralement pas à temps, encore une fois en raison de la taille plus importante des systèmes, de la complexité de la logique et même des méthodes de vérification utilisées.

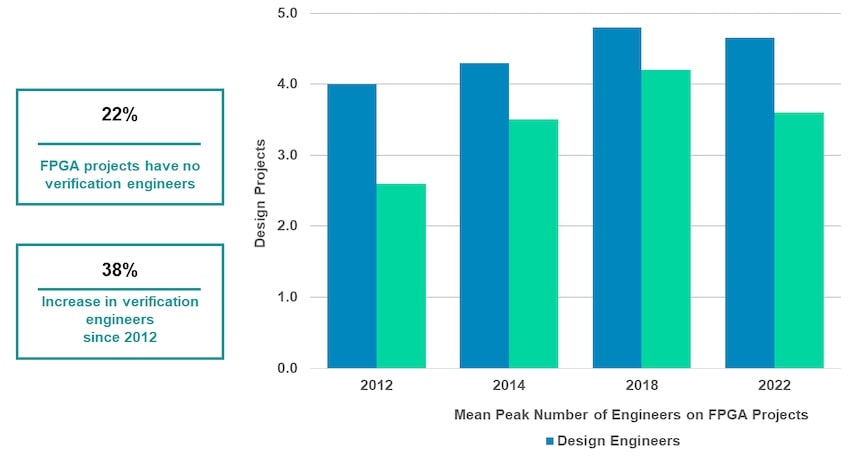

Les ingénieurs d'une équipe FPGA peuvent avoir des titres distincts comme ingénieur de conception ou ingénieur de vérification, mais sur 22 % des projets, il n'y avait pas d'ingénieurs de vérification, ce qui signifie que les ingénieurs de conception ont effectué une double tâche et ont vérifié leur propre propriété intellectuelle. Au cours des 10 dernières années, il y a eu une augmentation de 38 % du nombre d'ingénieurs de vérification sur un projet FPGA, c'est donc un progrès vers une production sans bug.

Les ingénieurs de vérification sur les projets FPGA ont passé la plupart de leur temps sur des tâches de débogage à 47 % :

- 47 % - Débogage

- 19 % - Création de tests et simulation d'exécution

- 17 % - Développement de bancs d'essai

- 11 % - Planification des tests

- 6 % – Autre

Le nombre de processeurs embarqués n'a cessé d'augmenter au fil du temps, de sorte que 65 % des conceptions de FPGA ont désormais un ou plusieurs cœurs de processeur, ce qui augmente le nombre de vérifications entre le matériel et les interfaces logicielles ; et la gestion des réseaux sur puce.

Le très populaire processeur RISC-V est intégré dans 22 % des FPGA et les accélérateurs d'IA sont utilisés dans 23 % des projets. Il y a 3 à 4 nombres moyens de domaines d'horloge utilisés sur les FPGA, et ils nécessitent des simulations de synchronisation au niveau de la porte pour la vérification, ainsi que l'utilisation d'outils statiques de croisement de domaine d'horloge (CDC) pour la vérification.

Des fonctionnalités de sécurité sont ajoutées à 49 % des conceptions de FPGA pour contenir des données sensibles, et 42 % des projets FPGA respectent des normes ou des directives critiques en matière de sécurité. Sur SemiWiki, nous avons souvent blogué sur ISO 26262 et de DO-254 normes. Les efforts de conception de la sécurité fonctionnelle (FuSa) prennent entre 25 % et 50 % du temps total du projet.

Les trois principaux langages de vérification sont VHDL, SystemVerilog et Verilog ; mais notez également les sauts récents dans les langages Python et C/C++.

Les méthodologies FPGA les plus populaires et les bibliothèques de cas de base de testbench sont : Accellera UVM, OSVVM et UVVM. Basé sur Python cocotte a même été ajoutée comme nouvelle catégorie pour 2022.

Les langages d'assertion sont menés par SystemVerilog Assertions (SVA) à 45 %, suivi par Accellera Open Verification Library (OVL) à 13 % et PSL à 11 %. Les conceptions FPGA peuvent combiner VHDL pour la conception RTL et SVA pour les assertions.

La vérification formelle des propriétés se développe parmi les projets FPGA, d'autant plus que des applications formelles plus automatiques ont été introduites par les fournisseurs EDA.

Les approches de vérification basées sur la simulation au cours des 10 dernières années montrent une adoption constante, classées par ordre de pertinence : couverture de code, couverture fonctionnelle, assertions, aléatoire contraint.

Résumé

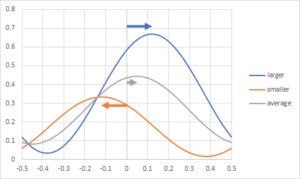

Le faible nombre de 17 % sans bug pour les projets FPGA en 2022 qui sont entrés en production était le chiffre le plus surprenant pour moi, car l'effort de rappel ou de reprogrammation d'un appareil sur le terrain est coûteux et prend du temps à corriger. Une approche de vérification fonctionnelle plus robuste devrait conduire à moins d'échappements de bogues dans la production, et la division des participants à l'étude en deux groupes montre l'avantage.

Lire le complet Livre blanc de 18 pages ici.

Blogs connexes

Partagez cet article via:

- Contenu propulsé par le référencement et distribution de relations publiques. Soyez amplifié aujourd'hui.

- Platoblockchain. Intelligence métaverse Web3. Connaissance Amplifiée. Accéder ici.

- La source: https://semiwiki.com/eda/324651-the-state-of-fpga-functional-verification/

- 1

- 10

- 2018

- 2022

- a

- A Propos

- accélérateurs

- ajoutée

- adhérer

- Adoption

- AI

- parmi

- montant

- et de

- applications

- une approche

- approches

- applications

- ase

- Automatique

- moyen

- va

- profiter

- Améliorée

- jusqu'à XNUMX fois

- Milliards

- Punaise

- bogues

- Compétences

- catégories

- Catégories

- Causes

- causé

- les causes

- CDC

- Chance

- vérification

- clairement

- horloge

- code

- combiner

- complet

- complexe

- complexité

- couverture

- La création

- critique

- données

- Conception

- Avec nos Bagues Halo

- dispositif

- Compatibles

- DID

- distinct

- domaine

- domaines

- chuté

- effort

- efforts

- intégré

- ingénieur

- Les ingénieurs

- notamment

- Pourtant, la

- Chaque

- cher

- Échec

- Automne

- Fonctionnalités:

- champ

- Prénom

- concentré

- suivi

- formel

- trouvé

- fpga

- De

- fonctionnel

- Portes

- Réservation de groupe

- Groupes

- Croître

- Croissance

- cultivé

- lignes directrices

- Matériel

- appuyez en continu

- HTML

- HTTPS

- in

- comprendre

- Améliore

- increased

- croissant

- Intel

- interfaces

- introduit

- IP

- IT

- sauts

- Langues

- plus importantes

- le plus grand

- conduire

- LED

- bibliothèques

- Bibliothèque

- limité

- Listé

- Faible

- LES PLANTES

- les gérer

- Marché

- largeur maximale

- sens

- méthodologies

- méthodes

- des millions

- PLUS

- (en fait, presque toutes)

- Le Plus Populaire

- Besoin

- réseaux

- Nouveauté

- nombre

- ONE

- ouvert

- de commander

- global

- propre

- Papier

- participants

- passé

- chemin

- Platon

- Intelligence des données Platon

- PlatonDonnées

- plus

- Populaire

- Post

- Processeur

- processeurs

- Vidéo

- Progrès

- Projet

- projets

- propriété

- protocoles

- prototype

- Python

- vite.

- aléatoire

- récent

- récemment

- libérer

- pertinence

- rapport

- exigent

- un article

- groupe de recherche

- robuste

- racine

- Round

- pour le running

- Sécurité

- sécurité

- clignotant

- sensible

- plusieurs

- devrait

- montrer

- Spectacles

- Siemens

- Silicium

- depuis

- considérable

- Taille

- So

- Logiciels

- vitesse

- dépensé

- Normes

- j'ai commencé

- Région

- stable

- Étude

- surprenant

- Système

- Prenez

- tâches

- équipe

- techniques

- tester

- La

- L'État

- leur

- Troisièmement

- trois

- fiable

- timing

- titres

- à

- aujourd'hui

- trop

- les outils

- top

- vers

- types

- utilisé

- fournisseurs

- Vérification

- vérifié

- vérifier

- via

- le volume

- qui

- blanc

- papier blanc

- Wilson

- années

- zéphyrnet