Quand vous pensez « FPGA », qu'est-ce qui vous vient à l'esprit ? Des pièces massives et coûteuses capables de contenir beaucoup de logique mais aussi de consommer beaucoup d'énergie. Plates-formes reconfigurables pouvant avaler RTL pour une conception de SoC dans les tests pré-silicium. De grandes acquisitions d'entreprises éclaboussantes où les investisseurs ont fait des tonnes d'argent. Emballage 3D exotique et interconnexions avancées. Mais probablement pas bon marché, petit boîtier, faible nombre de broches, pièces à faible consommation d'énergie en veille, n'est-ce pas ? L'eFPGA de Flex Logix revient à l'essentiel pour une logique programmable à faible consommation qui peut prendre en charge des dispositifs à moindre coût, à volume plus élevé et à taille limitée.

Deux routes programmables présentées au choix

Au risque de me dater, ma première exposition à ce qu'on appelait alors la technologie FPGA remonte à l'époque où Altera a sorti sa famille EPROM EP1200 dans un boîtier DIP à 40 broches avec son horloge de 16 MHz, sa puissance active de 400 mW et sa veille de 15 mW. pouvoir. Il est venu avec un éditeur de schémas et une bibliothèque de macros de porte. Les concepteurs dessinaient leur logique, « brûlaient » leur pièce, la testaient, la jetaient sous une lampe UV et l'effaçaient si elle ne fonctionnait pas, et réessayaient.

Peu de temps après, une carte est apparue dans un autre de nos laboratoires avec certains des premiers FPGA Xilinx. Celles-ci étaient basées sur la RAM au lieu d'être basées sur l'EPROM - plus grandes, plus rapides et reprogrammées sans que la lampe UV n'attende ou ne retire la pièce de la carte. La logique à l'intérieur était également plus complexe, avec l'introduction de multiplicateurs rapides. Ces pièces pourraient non seulement balayer la logique, mais pourraient également être utilisées pour explorer une capacité de traitement de signal numérique personnalisée avec des cycles de reconception rapides.

Cela a déclenché la course aux armements en silicium programmable et une bifurcation s'est développée entre le PLD - dispositif logique programmable - et le FPGA. Les fabricants ont fait des choix, Altera et Xilinx prenant la voie haute de l'évolutivité FPGA et Actel, Lattice et d'autres prenant la voie inférieure de la flexibilité PLD pour la « logique de liaison » afin de réduire les coûts de nomenclature.

eFPGA décale l'équation logique programmable basse consommation

Tout cela ressemble à un marché mature, avec une barrière à l'entrée élevée d'un côté et une offre plus standardisée de l'autre. Mais que se passerait-il si la logique programmable était un bloc IP qui pourrait être conçu dans n'importe quelle puce de cette ère sans usine, y compris un petit FPGA basse consommation ? Cela contournerait la barrière (au moins dans les offres bas et milieu de gamme) et la banalisation.

Flex Logix a relevé ce défi avec la dalle EFLX 1K eFPGA. Chaque tuile logique dispose de 560 tables de consultation (LUT) à six entrées avec RAM, horloge et interconnexion. La mise en réseau des tuiles EFLX permet de gérer divers rôles logiques et DSP. Mais ses caractéristiques les plus importantes peuvent être sa taille et sa gestion de l'alimentation.

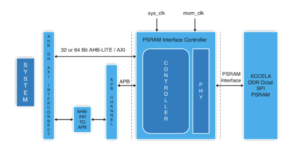

Fabriqué en TSMC 40ULP, le carreau EFLX 1K tient dans 1.5 mm2 et offre un blocage de l'alimentation pour les modes de veille profonde avec rétention d'état - beaucoup plus agressif que les PLD traditionnels. EFLX 1K possède également des fonctionnalités prêtes pour la production empruntées aux FPGA. Il présente des interfaces AXI ou JTAG pour la configuration du flux binaire, des circuits de relecture permettant une vérification logicielle des erreurs et un mode de test avec des vecteurs rationalisés améliorant la couverture et réduisant les temps de test.

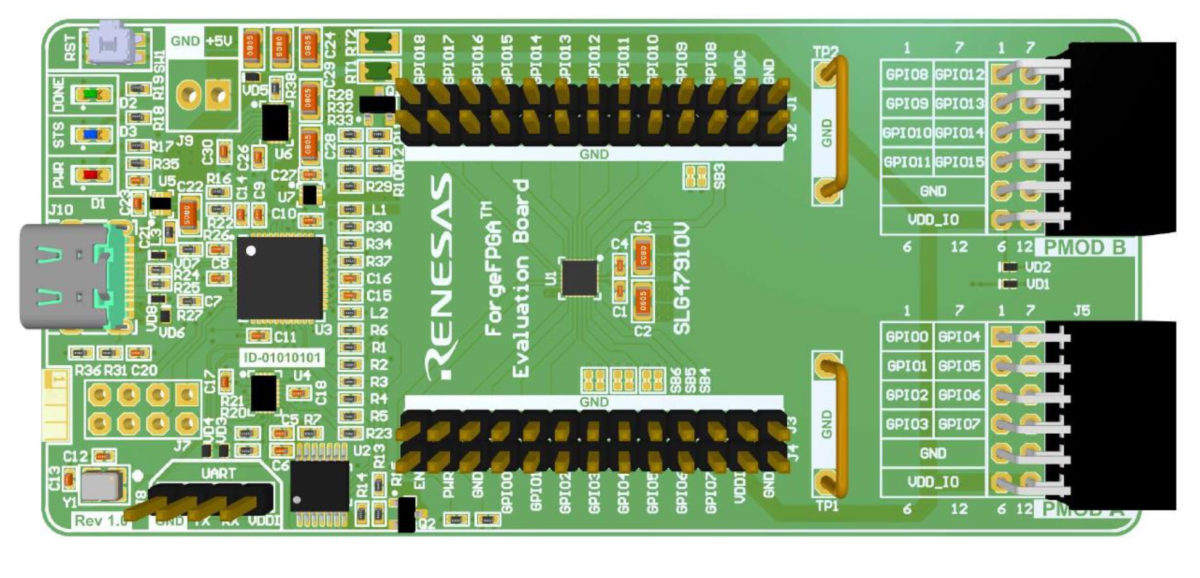

Vous voyez la puce au centre de cette image suivante ? Il s'agit d'un ForgeFPGA de Renesas dans un package QFN-24, basé sur EFLX 1K IP, que Renesas propose à des prix inférieurs à 1 $ en volume. Son courant cible de veille s'enregistre à moins de 20 uA. Une taille plus petite, un coût inférieur et moins de puissance ouvrent des portes auparavant fermées aux FPGA. La lignée de ForgeFPGA remonte à Silego Technology, puis à Dialog Semiconductor, acquis par Renesas en 2021.

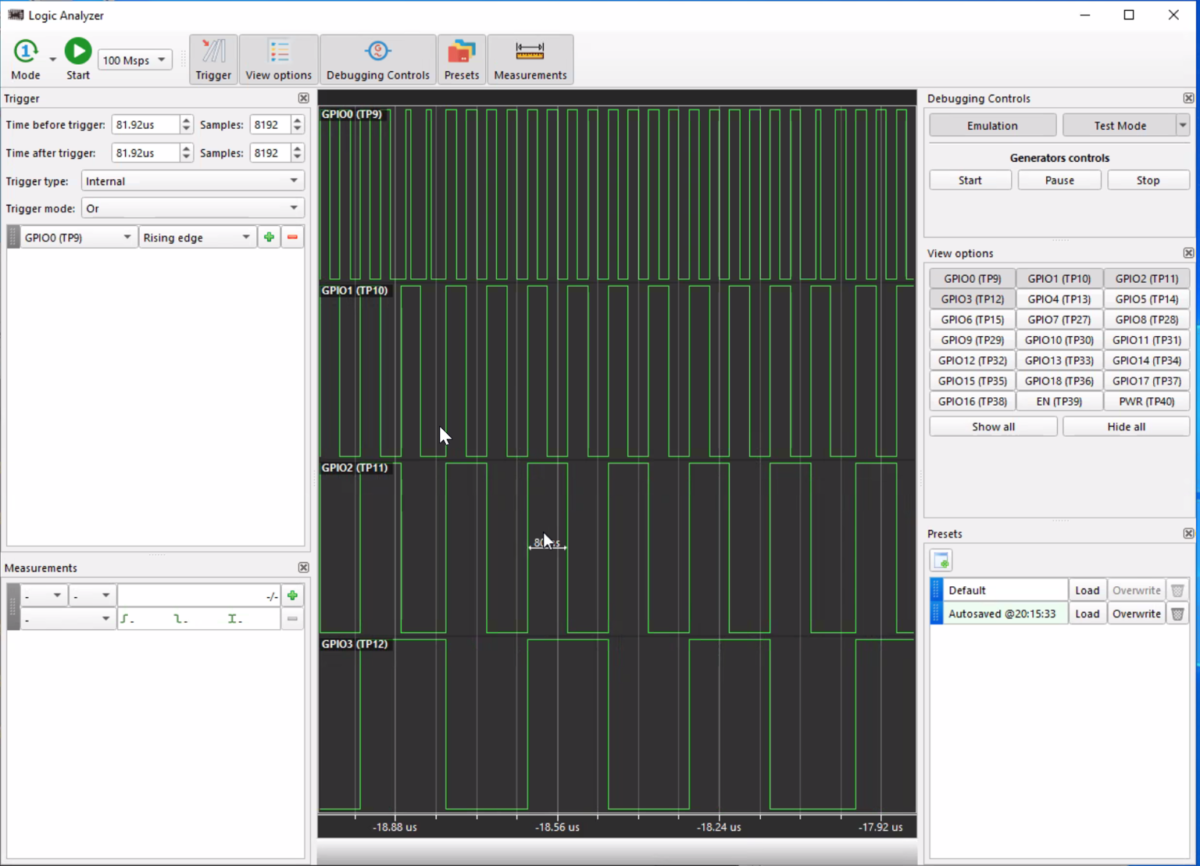

Renesas apporte l'environnement Go Configure IDE, mettant une interface utilisateur graphique au-dessus du compilateur Flex Logix EFLX. Il prend en charge le mappage des broches ForgeFPGA, la compilation de Verilog, la génération d'un flux binaire et dispose d'un analyseur logique léger.

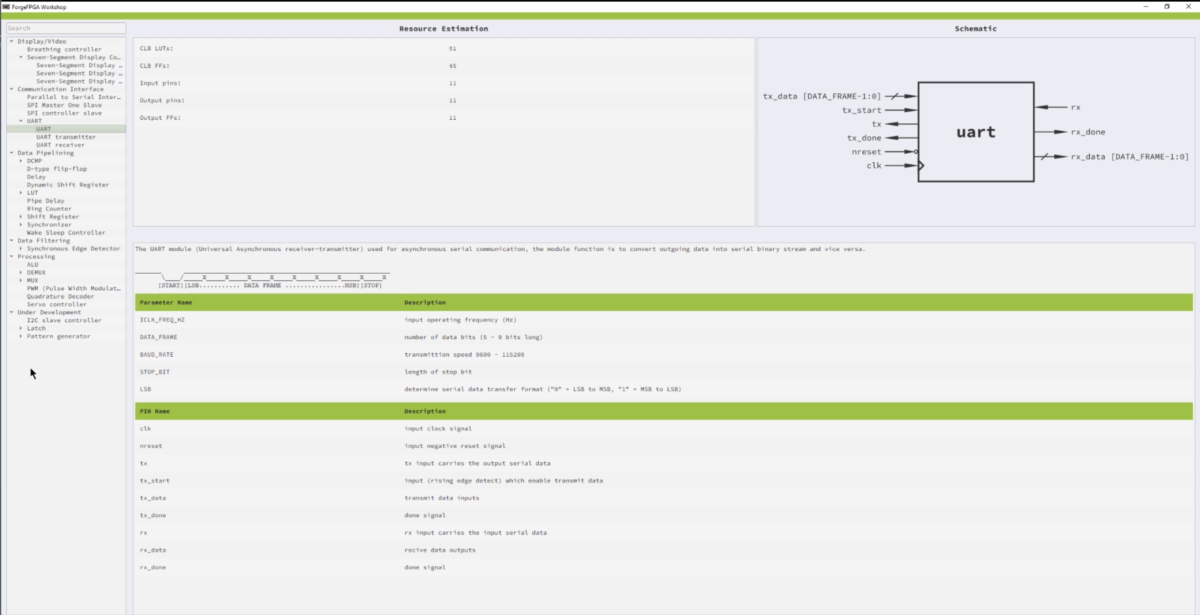

Les blocs d'application pré-construits pour le ForgeFPGA en ont un intéressant que Geoff Tate de Flex Logix souligne : un UART. Créer un UART en logique n'est pas si difficile, mais il s'avère que tout le monde s'y est pris différemment, et c'est juste assez de logique pour être plus que quelques puces discrètes. Un ForgeFPGA est un morceau de logique reconfigurable qui peut résoudre ce problème, permettant à une implémentation matérielle de s'adapter rapidement à diverses configurations.

ForgeFPGA n'est qu'un exemple de ce qui peut être fait avec la tuile eFPGA Flex Logix EFLX 1K. Flex Logix peut adapter l'adresse IP pour différents nœuds de processus, et la capacité de mosaïque mixte offre une évolutivité. Il atteint de nouveaux bas pour la logique programmable basse consommation et permet aux fabricants de puces de différencier les solutions de manière remarquable. Pour plus d'informations, veuillez visiter :

Lisez aussi:

eFPGA gérant la crypto-agilité pour les SoC avec PQC

Flex Logix : le premier système basé sur un Mini-ITX intégré à l'IA de l'industrie

Flex Logix s'associe à Intrinsic ID pour sécuriser la plate-forme eFPGA

Partagez cet article via:

- Contenu propulsé par le référencement et distribution de relations publiques. Soyez amplifié aujourd'hui.

- Platoblockchain. Intelligence métaverse Web3. Connaissance Amplifiée. Accéder ici.

- La source: https://semiwiki.com/efpga/flex-logix/325926-efpga-goes-back-to-basics-for-low-power-programmable-logic/

- :est

- $UP

- 1

- 2021

- 3d

- a

- capacité

- A Propos

- à propos de ça

- Atteint

- a acquise

- acquisitions

- infection

- adapter

- Avancée

- Après

- agressif

- AI

- Tous

- Permettre

- permet

- et les

- Une autre

- Application

- At

- RETOUR

- une barrière

- basé

- Basics

- BE

- jusqu'à XNUMX fois

- Big

- plus gros

- Block

- Blocs

- planche

- emprunté

- Apportez le

- Apporté

- by

- appelé

- CAN

- capable

- Canaux centraux

- challenge

- vérification

- Contrôles

- puce

- chips

- choix

- horloge

- fonds à capital fermé

- complexe

- configuration

- Entreprises

- Prix

- Costs

- pourriez

- Couples

- couverture

- La création

- Courant

- Customiser

- cycles

- Rencontres

- profond

- Conception

- un

- designers

- développé

- dispositif

- Compatibles

- dialogue

- différencier

- difficile

- numérique

- Trempez

- portes

- chacun

- éditeur

- permettant

- assez

- entrée

- Environment

- Ère

- erreur

- évaluation

- tout le monde

- exemple

- Exotique

- cher

- explorez

- Exposition

- famille

- RAPIDE

- plus rapide

- Fonctionnalités:

- Prénom

- Flexibilité

- Pour

- fpga

- De

- générateur

- donne

- Go

- Goes

- manipuler

- Maniabilité

- Matériel

- Vous avez

- Haute

- augmentation

- tenue

- HTTPS

- ID

- image

- la mise en oeuvre

- l'amélioration de

- in

- Y compris

- de l'industrie

- peu coûteux

- info

- plutôt ;

- des services

- intéressant

- Interfaces

- interfaces

- intrinsèque

- Introduction

- Investisseurs

- IP

- IT

- SES

- jpg

- juste un

- Labs

- Bibliothèque

- léger

- comme

- Lot

- Faible

- abaissement

- Dépressions dans l'air

- Macro

- macros

- LES PLANTES

- Décideurs

- gestion

- Fabricants

- cartographie

- Marché

- massif

- mature

- largeur maximale

- l'esprit

- Mode

- modes

- de l'argent

- PLUS

- (en fait, presque toutes)

- Nouveauté

- next

- nœuds

- of

- offrant

- Offrandes

- Offres Speciales

- on

- ONE

- ouvert

- Autre

- Autres

- paquet

- l'emballage

- partie

- partenaires,

- les pièces

- broches

- Plateformes

- Platon

- Intelligence des données Platon

- PlatonDonnées

- veuillez cliquer

- des notes bonus

- Post

- power

- présenté

- cadeaux

- précédemment

- prix

- Probablement

- Problème

- processus

- traitement

- important

- Putting

- vite.

- Race

- RAM

- Nos tests de diagnostic produisent des résultats rapides et précis sans nécessiter d'équipement de laboratoire complexe et coûteux,

- Lire

- reconcevoir

- réduire

- remarquables

- enlever

- rétention

- Analyse

- routières

- routes

- rôle

- Évolutivité

- sécurisé

- semi-conducteur

- set

- Changements

- Signal

- Silicium

- Taille

- sleep

- petit

- faibles

- Soft

- Solutions

- RÉSOUDRE

- quelques

- Région

- rationalisé

- Les soutiens

- Sweep

- Prenez

- prise

- Target

- Technologie

- tester

- Essais

- qui

- La

- leur

- Ces

- fois

- à

- tonnes

- top

- traditionnel

- TSMC

- sous

- Utilisateur

- Interface utilisateur

- divers

- via

- Visiter

- le volume

- attendez

- façons

- Quoi

- qui

- comprenant

- sans

- activités principales

- pourra

- zéphyrnet