Depuis ses débuts dans les années 1980 avec des réseaux locaux partagés à 10 Mbps sur des câbles coaxiaux, Ethernet a connu des progrès constants, avec désormais le potentiel de prendre en charge des vitesses allant jusqu'à 1.6 Tb/s. Cette progression a permis à Ethernet de servir une gamme plus large d'applications, telles que la diffusion en direct, les réseaux d'accès radio et le contrôle industriel, soulignant l'importance d'un transfert de paquets fiable et d'une qualité de service. Avec une bande passante Internet actuelle d’environ 500 Tbit/s, il existe une demande croissante pour une meilleure gestion du trafic back-end intra-centre de données. Bien que les serveurs individuels ne fonctionnent pas encore au niveau du térabit par seconde, le trafic global du centre de données se rapproche de cette échelle, ce qui incite le groupe 802.3dj de l'IEEE à entreprendre des efforts de normalisation et nécessite des contrôleurs Ethernet robustes et des SerDes pour gérer le flux de données en expansion. Dans ce contexte de demandes croissantes, la communication entre processeurs atteint déjà ces vitesses.

La communication entre processeurs est à l'origine du besoin de débits de 1.6 T avec une latence minimale. Alors que les appareils individuels sont limités par leurs capacités de traitement inhérentes et la taille de leurs puces, la combinaison de puces peut étendre considérablement ces capacités. La première génération d'applications devrait être suivie par des connexions switch-to-switch intra-centre de données, permettant la mise en commun de processeurs et de mémoire hautes performances, renforçant ainsi l'évolutivité et l'efficacité du cloud computing.

Initiative 802.3dj de l'IEEE : faire progresser les normes Ethernet pour une interopérabilité à 1.6 Tbit/s

La conformité aux efforts de normalisation en constante évolution est essentielle pour une interopérabilité transparente des écosystèmes. Le groupe 802.3dj de l'IEEE est en train de formuler la prochaine norme Ethernet, qui englobe les couches physiques et les paramètres de gestion pour des vitesses allant de 200G à 1.6 térabits par seconde. L’objectif du groupe est un débit de données MAC Ethernet de 1.6 Tb/s, visant un taux d’erreur binaire maximum ne dépassant pas 10-13 au niveau de la couche MAC. D'autres dispositions incluent des interfaces d'unité de fixation (AUI) optionnelles à 16 et 8 voies adaptées à différentes applications de puces, exploitant les SerDes 112G et 224G. Physiquement, la spécification 1.6 Tbps implique la transmission via 8 paires de câbles twinax en cuivre jusqu'à un mètre et 8 paires de fibre pour des distances allant de 500 mètres à 2 km. Bien que la ratification complète de la norme soit prévue d’ici le printemps 2026, l’achèvement de l’ensemble des fonctionnalités de base est prévu pour 2024.

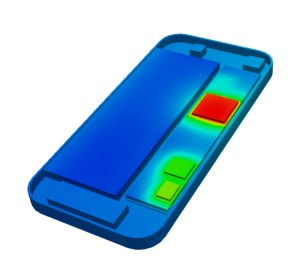

Surcharge de bande passante et correction d'erreurs dans un sous-système Ethernet 1.6T

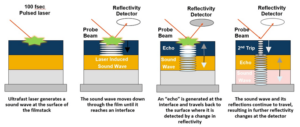

Fig. 1 : Schéma illustrant les composants d'un sous-système Ethernet 1.6T.

Dans les itérations Ethernet précédentes, le PCS se concentrait principalement sur le codage des données pour une détection fiable des paquets. Cependant, avec l'évolution vers des vitesses Ethernet de 1.6 T, la nécessité d'une correction d'erreur directe (FEC) devient évidente, en particulier pour contrecarrer la dégradation du signal, même sur des liaisons courtes. À cette fin, Ethernet 1.6T continue d'utiliser le FEC Reed-Solomon. Cette approche construit un mot de code comprenant 514 symboles de 10 bits codés dans un bloc de 544 symboles, ce qui entraîne une surcharge de bande passante de 6 %. Ces mots de code FEC sont répartis sur les liaisons physiques AUI afin que chaque liaison physique (8 pour Ethernet 1.6T) ne transporte pas un mot de code complet. Cette méthode offre non seulement une protection supplémentaire contre les salves d'erreurs, mais permet également la parallélisation au niveau du décodeur distant, réduisant ainsi la latence.

Le Physical Medium Attachment (PMA), doté d'une boîte de vitesses et de SerDes, amène le signal Ethernet sur les canaux transmis. Pour Ethernet 1.6T, cela implique 8 canaux fonctionnant chacun à 212 Gbit/s, ce qui représente une surcharge FEC de 6 %. La technique de modulation utilisée est la modulation d'amplitude d'impulsion à 4 niveaux (PAM-4), qui code deux bits de données pour chaque symbole de transmission, doublant ainsi efficacement la bande passante lorsqu'elle est juxtaposée à l'approche traditionnelle sans retour zéro (NRZ). Le mécanisme de transmission repose sur la conversion numérique-analogique, tandis qu'à la réception, une conversion analogique-numérique combinée à des DSP garantit une extraction précise du signal.

De plus, il est important de noter que le PCS Ethernet introduit un « FEC externe » qui s’étend de bout en bout sur une liaison Ethernet. Pour renforcer les canaux à plus longue portée, une couche supplémentaire de correction d'erreurs pour les lignes physiques individuelles est en préparation, en adoptant probablement un code de jambon FEC. Cette correction devrait trouver sa principale application dans les modules émetteurs-récepteurs optiques où une telle correction est impérative.

Fig. 2 : Diagramme illustrant la surcharge supplémentaire ajoutée lors de l'utilisation d'un FEC concaténé pour une portée étendue.

Dans l'exemple de système représenté sur la figure 2, le MAC et le PCS sont connectés via un module optique et un tronçon de fibre. Le PCS a un taux d'erreur sur les bits de 10-5 au niveau de la liaison du module optique, plus les erreurs provenant de la liaison optique elle-même. Utiliser un seul RS-FEC de bout en bout ne suffirait pas pour atteindre les 10- 13 Norme Ethernet, rendant la liaison peu fiable. Une option serait une triple implémentation de RS FEC distincte sur chaque saut, augmentant considérablement les coûts et la latence. Une solution plus efficace consiste à intégrer un code de Hamming concaténé FEC spécifiquement pour la liaison optique, répondant aux erreurs aléatoires typiques des connexions optiques. Cette couche FEC interne crée une expansion supplémentaire du débit de ligne de 212 Gbit/s à 226 Gbit/s, il est donc essentiel que les SerDes puissent prendre en charge ce débit de ligne.

Problèmes de latence dans les systèmes Ethernet 1.6T

Fig. 3 : Chemin de latence pour le sous-système Ethernet 1.6T.

Divers composants contribuent à la latence Ethernet : la file d'attente de transmission, la durée de transmission, le temps de parcours du support et plusieurs temps de traitement et de réception. Pour visualiser cela, considérons la figure 3, qui présente un sous-système Ethernet 1.6T complet. Même si la latence peut être influencée par le temps de réaction de l'application distante, ce facteur est externe à Ethernet et est donc souvent exclu lors de l'analyse de la latence. Minimiser la latence au niveau de l'interface Ethernet nécessite de comprendre les circonstances spécifiques. Par exemple, la latence peut ne pas être une préoccupation majeure pour les connexions principales entre les commutateurs en raison des retards inhérents aux liaisons client plus lentes. La distance joue également un rôle ; des longueurs plus grandes introduisent plus de latence. Bien entendu, cela ne signifie pas que nous devons négliger la latence dans d’autres scénarios : la réduction de la latence est toujours un objectif.

La latence de transmission est intrinsèquement liée au débit Ethernet et à la taille de trame. Plus précisément, pour un système Ethernet 1.6T, la transmission d'un paquet de taille minimale nécessite 0.4 ns, soit essentiellement une trame Ethernet par tick d'une horloge de 2.5 GHz. D'un autre côté, la transmission d'une trame standard de taille maximale prend 8 ns, s'étendant jusqu'à 48 ns pour les trames Jumbo. Le support choisi dicte en outre la latence. Par exemple, la fibre optique subit généralement une latence de 5 ns par mètre, tandis que le câblage en cuivre est légèrement plus rapide, à 4 ns par mètre.

Une partie importante de la latence globale est enracinée dans le contrôleur du récepteur. Le décodeur RS FEC introduit intrinsèquement une latence. Pour lancer la correction d'erreur, le système doit recevoir 4 mots de code, ce qui, à 1.6 Tbps, équivaut à 12.8 ns. Les activités ultérieures, notamment la correction d’erreurs et la mise en mémoire tampon, amplifient cette latence. Bien que la durée de stockage du mot de passe FEC reste cohérente, la latence lors de la réception du message dépend de la mise en œuvre spécifique. Néanmoins, la latence peut être optimisée en employant des stratégies de conception numérique méticuleuses.

Essentiellement, il existe une latence inhérente et inévitable due au mécanisme FEC et à la distance physique ou à la longueur du câble. Au-delà de ces facteurs, l'expertise en conception joue un rôle central pour minimiser la latence du contrôleur Ethernet. L’exploitation d’une solution complète qui intègre et optimise les systèmes MAC, PCS et PHY ouvre la voie à une mise en œuvre la plus efficace et à faible latence.

Résumé

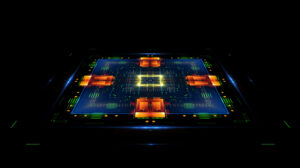

Fig. 4 : Succès du premier passage du silicium pour l'IP PHY Ethernet Synopsys 224G dans un processus 3 nm présentant des yeux PAM-4 hautement linéaires.

Ethernet 1.6 Tbit/s est conçu pour les applications les plus exigeantes en bande passante et sensibles à la latence. Avec l'émergence de la technologie 224G SerDes, associée aux avancées en matière d'IP MAC et PCS, des solutions complètes sont désormais accessibles et se conforment en permanence aux normes Ethernet 1.6T en évolution. De plus, en raison de la latence intrinsèque au protocole et aux méthodes de correction d'erreurs, la conception numérique et analogique IP doit être soigneusement conçue par des concepteurs experts pour éviter d'introduire une latence inutile dans le chemin de données.

Atteindre des performances optimales pour les conceptions de SoC 1.6T nécessite une architecture optimisée efficacement et des pratiques de conception méticuleuses pour chaque composant de puce. Cela met l'accent sur la conservation de l'énergie et minimise l'empreinte silicium, faisant des débits de données de 1.6 T une réalité. Synopsys 224G Ethernet PHY IP éprouvé au silicium a préparé le terrain pour le contrôleur MAC et PCS 1.6T. Grâce à des techniques de conception, d'analyse, de simulation et de mesure de pointe, Synopsys continue de fournir une intégrité de signal et des performances de gigue exceptionnelles, avec un solution Ethernet complète comprenant MAC+PCS+PHY.

- Contenu propulsé par le référencement et distribution de relations publiques. Soyez amplifié aujourd'hui.

- PlatoData.Network Ai générative verticale. Autonomisez-vous. Accéder ici.

- PlatoAiStream. Intelligence Web3. Connaissance Amplifiée. Accéder ici.

- PlatonESG. Carbone, Technologie propre, Énergie, Environnement, Solaire, La gestion des déchets. Accéder ici.

- PlatoHealth. Veille biotechnologique et essais cliniques. Accéder ici.

- La source: https://semiengineering.com/latency-considerations-for-1-6t-ethernet-designs/

- :possède

- :est

- :ne pas

- :où

- $UP

- 1

- 12

- 16

- 2024

- 2026

- 212

- 220

- 362

- 500

- 8

- a

- accès

- accessible

- Comptabilité

- Avec cette connaissance vient le pouvoir de prendre

- atteindre

- à travers

- d'activités

- ajoutée

- Supplémentaire

- En outre

- L'adoption d'

- progrès

- de suivre

- à opposer à

- Visée

- permis

- déjà

- aussi

- Bien que

- toujours

- au milieu de

- quantités

- amplifier

- an

- selon une analyse de l’Université de Princeton

- ainsi que le

- Prévoir

- Application

- applications

- une approche

- architecture

- SONT

- AS

- At

- éviter

- Back-end

- toile de fond

- Bande passante

- BE

- devient

- jusqu'à XNUMX fois

- Au-delà

- Bit

- Block

- traversin

- stimuler

- Apportez le

- construit

- mais

- by

- câble

- cet ensemble de câbles polyvalent

- CAN

- capacités

- porter

- globaux

- Voies

- puce

- chips

- choisi

- conditions

- client

- horloge

- le cloud

- le cloud computing

- code

- combiné

- combinant

- Communication

- complet

- achèvement

- composant

- composants électriques

- complet

- comprenant

- informatique

- PROBLÈMES DE PEAU

- conjonction

- connecté

- Connexions

- CONSERVATION

- Considérer

- considérations

- cohérent

- continue

- continuellement

- contribuer

- des bactéries

- contrôleur

- Conversion

- Cuivre

- Core

- Costs

- contrer

- cours

- Fabriqué

- crée des

- Courant

- données

- Datacenter

- début

- retards

- livrer

- Demande

- exigeant

- demandes

- représentant

- Conception

- designers

- Avec nos Bagues Halo

- Détection

- Compatibles

- dicte

- différent

- numérique

- diligemment

- affiche

- distance

- distribué

- Ne fait pas

- doubler

- deux

- durée

- pendant

- chacun

- Plus tôt

- risque numérique

- Efficace

- de manière efficace

- efficace

- efficace

- efficacement

- efforts

- émergence

- souligne

- mettant l'accent

- employés

- employant

- permet

- permettant

- englobe

- fin

- end-to-end

- Assure

- Tout

- erreur

- Erreurs

- escalade

- essence

- essential

- essentiellement

- Ether (ETH)

- Pourtant, la

- Chaque

- évident

- évolution

- exemple

- exceptionnel

- exclu

- expansion

- avec des données

- attendu

- expert

- nous a permis de concevoir

- étendre

- extension

- externe

- extraction

- Yeux

- facteur

- facteurs

- loin

- plus rapide

- Fonctionnalités:

- Doté d'

- Figure

- Trouvez

- Prénom

- Première génération

- flux

- concentré

- suivi

- numérique

- Pour

- formuler

- Avant

- CADRE

- De

- plus

- génération

- donne

- plus grand

- Réservation de groupe

- Groupes

- Croissance

- main

- Maniabilité

- Haute

- haute performance

- très

- Cependant

- HTML

- HTTPS

- impératif

- la mise en oeuvre

- importance

- important

- amélioré

- in

- Dans d'autres

- comprendre

- Y compris

- croissant

- individuel

- industriel

- influencé

- inhérent

- intrinsèquement

- initier

- initiative

- instance

- Intègre

- l'intégration

- intégrité

- Interfaces

- interfaces

- Internet

- Interopérabilité

- développement

- intrinsèque

- introduire

- Introduit

- Découvrez le tout nouveau

- implique

- IP

- IT

- itérations

- SES

- lui-même

- jpg

- Voie

- Latence

- couche

- poules pondeuses

- Longueur

- niveaux

- en tirant parti

- Probable

- Gamme

- lignes

- LINK

- Gauche

- le travail

- plus long

- Faible

- mac

- Fabrication

- gérer

- gestion

- largeur maximale

- maximales

- Mai..

- signifier

- mesures

- mécanisme

- moyenne

- Mémoire

- message

- méthode

- méthodes

- méticuleux

- minimal

- minimiser

- minimise

- réduisant au minimum

- module

- Modules

- PLUS

- (en fait, presque toutes)

- must

- approchant

- Besoin

- réseaux

- Néanmoins

- aucune

- noter

- maintenant

- objectif

- of

- souvent

- on

- ONE

- uniquement

- d'exploitation

- optimisé

- Optimise

- Option

- or

- Autre

- plus de

- global

- paires

- paramètres

- particulièrement

- chemin

- PC

- /

- performant

- performances

- Physique

- Physiquement

- pipeline

- pivot

- Platon

- Intelligence des données Platon

- PlatonDonnées

- joue

- plus

- défaillances

- power

- pratiques

- qui se déroulent

- primaire

- processus

- traitement

- processeurs

- progression

- projetée

- protection

- protocole

- impulsion

- but

- Poussant

- qualité

- Radio

- aléatoire

- gamme

- Tarif

- Tarifs

- nous joindre

- atteindre

- réaction

- Réalité

- recevoir

- recevoir

- réception

- réduire

- fiable

- reste

- rendu

- a besoin

- limité

- résultant

- robuste

- Rôle

- enraciné

- pour le running

- Évolutivité

- Escaliers intérieurs

- scénarios

- fluide

- Deuxièmement

- vu

- clignotant

- sensible

- séparé

- besoin

- service

- set

- plusieurs

- commun

- Shorts

- devrait

- mettre en valeur

- Signal

- de façon significative

- Silicium

- simulation

- Taille

- So

- sur mesure

- Solutions

- travées

- le fer de lance

- groupe de neurones

- spécifiquement

- spécification

- vitesses

- printemps

- Étape

- Standard

- standardisation

- Normes

- storage

- les stratégies

- streaming

- ultérieur

- Ces

- succès

- tel

- convient

- Support

- symbole

- combustion propre

- prend

- technique

- techniques

- Technologie

- que

- qui

- La

- leur

- Là.

- ainsi

- donc

- Ces

- this

- Avec

- Ainsi

- tique

- Attaché

- fiable

- fois

- à

- top

- traditionnel

- circulation

- transférer

- transmettre

- Tripler

- deux

- débutante

- typiquement

- inévitable

- compréhension

- entreprendre

- unité

- prochain

- sur

- en utilisant

- utiliser

- via

- visualiser

- Façon..

- we

- quand

- qui

- tout en

- plus large

- comprenant

- dans les

- pourra

- encore

- zéphyrnet

- zéro