Sen 1980-luvun debyyttistään lähtien, jossa 10 Mbps jaetut LAN-verkot koaksiaalikaapeleiden kautta, Ethernet on nähnyt johdonmukaisia edistysaskeleita, ja nyt se voi tukea jopa 1.6 Tbps:n nopeuksia. Tämä kehitys on mahdollistanut Ethernetin palvelevan laajempia sovelluksia, kuten suoratoistoa, radioliityntäverkkoja ja teollista ohjausta, mikä korostaa luotettavan pakettisiirron ja palvelun laadun merkitystä. Internetin nykyisen kaistanleveyden jyllääessä ~500 Tbps:ssä, parannetun palvelinkeskuksen sisäisen taustaliikenteen kysyntä kasvaa. Vaikka yksittäiset palvelimet eivät vielä toimi terabitin sekunnissa -tasolla, palvelinkeskusten yleinen liikenne on lähellä tätä mittakaavaa, mikä saa IEEE:n 802.3dj-ryhmän ryhtymään standardointitoimiin ja vaativat vankat Ethernet-ohjaimia ja SerDe-laitteita laajenevan tietovirran hallitsemiseksi. Keskellä tätä kasvavien tarpeiden taustaa prosessorien välinen viestintä on jo saavuttamassa näitä nopeuksia.

Prosessorien välinen viestintä on edelläkävijä 1.6 T:n nopeuksille minimaalisella latenssilla. Vaikka yksittäisiä laitteita rajoittavat niiden luontainen prosessointikapasiteetti ja sirukoko, sirujen yhdistäminen voi merkittävästi laajentaa näitä kapasiteettia. Ensimmäisen sukupolven sovellusten odotetaan seuraavan palvelinkeskuksen sisäiset kytkimestä kytkimeen -yhteydet, jotka mahdollistavat tehokkaiden prosessorien ja muistin yhdistämisen, mikä lisää skaalautuvuutta ja tehokkuutta pilvipalveluissa.

IEEE:n 802.3dj-aloite: Ethernet-standardien kehittäminen 1.6 Tbps:n yhteentoimivuudelle

Kehittyvien standardointitoimien noudattaminen on keskeistä saumattoman ekosysteemien yhteentoimivuuden kannalta. IEEE:n 802.3dj-ryhmä laatii parhaillaan tulevaa Ethernet-standardia, joka kattaa fyysiset tasot ja hallintaparametrit nopeuksille 200 G - 1.6 terabittiä sekunnissa. Ryhmän tavoitteena on 1.6 Tbps Ethernetin MAC-tiedonsiirtonopeus, jonka tavoitteena on enintään 10-13 bittivirhesuhde MAC-kerroksessa. Muita varusteita ovat valinnaiset 16- ja 8-kaistaiset liitännät (AUI), jotka soveltuvat erilaisiin sirusovelluksiin ja jotka hyödyntävät 112G- ja 224G-serDes. Fyysisesti 1.6 Tbps:n spesifikaatio sisältää lähetyksen 8 parin kuparisia twinax-kaapeleita enintään yhden metrin ja 8 parin kuitujen kautta 500 metrin ja 2 km:n välisillä etäisyyksillä. Vaikka standardin täydellinen ratifiointi on odotettavissa kevääseen 2026 mennessä, ydinominaisuuksien ennustetaan valmistuvan vuonna 2024.

Kaistanleveyden lisäkustannukset ja virheiden korjaus 1.6T Ethernet-alijärjestelmissä

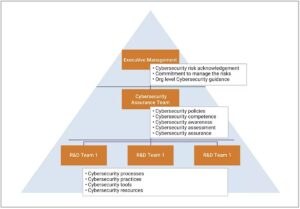

Kuva 1: Kaavio, joka esittää 1.6T Ethernet-alijärjestelmän komponentteja.

Aiemmissa Ethernet-iteraatioissa PCS keskittyi ensisijaisesti datan koodaukseen luotettavaa pakettien havaitsemista varten. 1.6 T Ethernetin nopeuksien kasvaessa FEC (Forward Error Correction) -korjauksen tarve tulee kuitenkin ilmeiseksi erityisesti signaalin heikkenemisen estämiseksi jopa lyhyiden linkkien aikana. Tätä tarkoitusta varten 1.6T Ethernet käyttää edelleen Reed-Solomon FEC:tä. Tämä lähestymistapa rakentaa koodisanan, joka sisältää 514 10-bittistä symbolia koodattuina 544 symbolilohkoon, mikä johtaa 6 %:n kaistanleveyteen. Nämä FEC-koodisanat on jaettu AUI:n fyysisten linkkien kesken, joten jokainen fyysinen linkki (8 1.6T Ethernetille) ei sisällä koko koodisanaa. Tämä menetelmä ei ainoastaan anna lisäsuojaa virhepurskeita vastaan, vaan mahdollistaa myös rinnakkaisuuden etäpään dekooderissa, mikä vähentää latenssia.

Physical Medium Attachment (PMA), jossa on vaihdelaatikko ja SerDes, tuo Ethernet-signaalin lähetetyille kanaville. 1.6T Ethernetissä tämä sisältää 8 kanavaa, joista kukin toimii nopeudella 212 Gbps, mikä vastaa 6 % FEC-yleiskustannuksia. Käytetty modulaatiotekniikka on 4-tasoinen pulssiamplitudimodulaatio (PAM-4), joka koodaa kaksi databittiä kullekin lähetyssymbolille, mikä tehokkaasti kaksinkertaistaa kaistanleveyden, kun se rinnastetaan perinteisen Non-Return Zero (NRZ) -lähestymistavan kanssa. Lähetysmekanismi perustuu digitaali-analogiamuunnoksiin, kun taas vastaanottopäässä analogia-digitaalimuunnos yhdistettynä DSP:ihin varmistaa tarkan signaalin erotuksen.

Lisäksi on tärkeää huomata, että Ethernet PCS ottaa käyttöön "ulomman FEC:n", joka kattaa Ethernet-linkin päästä päähän. Pidemmän kattavuuden kanavien vahvistamiseksi yksittäisille fyysisille linjoille on valmisteilla lisätty virheenkorjauskerros, joka todennäköisesti käyttää hamming-koodia FEC. Tämän korjauksen odotetaan löytävän ensisijaisen sovelluksensa optisissa lähetin-vastaanotinmoduuleissa, joissa tällainen korjaus on välttämätöntä.

Kuva 2: Kaavio, joka esittää lisäkustannuksia, jotka on lisätty käytettäessä ketjutettua FEC:tä laajemman ulottuvuuden saavuttamiseksi.

Kuvassa 2 esitetyssä esimerkkijärjestelmässä MAC ja PCS on yhdistetty optisen moduulin ja kuitulangan kautta. PCS:n bittivirheprosentti on 10-5 optisen moduulin linkissä sekä itse optisen linkin virheet. Ainoan RS-FEC-päästä päähän käyttäminen ei riittäisi 10:n saavuttamiseen-13 Ethernet-standardi, mikä tekee linkistä epäluotettavan. Vaihtoehtona olisi erillisen RS FEC:n kolminkertainen käyttöönotto jokaisessa hyppyssä, mikä lisää kustannuksia ja viivettä merkittävästi. Tehokkaampi ratkaisu on ketjutetun Hamming Code FEC:n integrointi erityisesti optista linkkiä varten, mikä huomioi optisten yhteyksien tyypilliset satunnaiset virheet. Tämä sisäinen FEC-kerros lisää linjanopeuden lisälaajennusta 212 Gbps:stä 226 Gbps:iin, joten on oleellista, että SerDes tukee tätä linjanopeutta.

Latenssihaasteet 1.6T Ethernet-järjestelmissä

Kuva 3: Latenssipolku 1.6T Ethernet-alijärjestelmälle.

Eri komponentit vaikuttavat Ethernetin latenssiin: lähetysjono, lähetyksen kesto, keskipitkän läpikulkuaika sekä useat käsittely- ja vastaanottoajat. Tämän visualisoimiseksi harkitse kuvaa 3, joka näyttää kattavan 1.6T Ethernet-alijärjestelmän. Vaikka latenssiin voi vaikuttaa etäpääsovelluksen reaktioaika, tämä tekijä on Ethernetin ulkopuolinen ja siksi se jätetään usein pois latenssianalyysin aikana. Latenssin minimoiminen Ethernet-liitännässä edellyttää erityisten olosuhteiden ymmärtämistä. Esimerkiksi viive ei ehkä ole ensisijainen huolenaihe kytkimien välisissä runkoyhteyksissä hitaampien asiakaslinkkien luontaisten viiveiden vuoksi. Etäisyydellä on myös merkitystä; pidemmät pituudet lisäävät latenssia. Tämä ei tietenkään tarkoita, että meidän pitäisi unohtaa latenssi muissa skenaarioissa, latenssin vähentäminen on aina tavoite.

Lähetysviive on luonnostaan sidottu Ethernetin nopeuteen ja kehyskokoon. Tarkemmin sanottuna 1.6T Ethernet-järjestelmässä vähimmäiskokoisen paketin lähettäminen vaatii 0.4 ns:n – käytännössä yhden Ethernet-kehyksen 2.5 GHz:n kellon tikkua kohden. Toisaalta normaalin enimmäiskokoisen kehyksen lähettäminen kestää 8 ns, joka ulottuu Jumbo Frame -kehyksille 48 ns:iin. Valittu media sanelee edelleen latenssia. Esimerkiksi optisen kuidun latenssi on tyypillisesti 5 ns per metri, kun taas kuparikaapelointi on hieman nopeampi 4 ns per metri.

Huomattava osa kokonaislatenssista on juurtunut vastaanottimen ohjaimeen. RS FEC -dekooderi sisältää luonnostaan latenssin. Virheenkorjauksen aloittamiseksi järjestelmän on vastaanotettava 4 koodisanaa, mikä nopeudella 1.6 Tbps on 12.8 ns. Myöhemmät toiminnot, mukaan lukien virheenkorjaus ja puskurointi, vahvistavat tätä latenssia. Vaikka FEC-koodisanan tallennuskesto pysyy yhtenäisenä, viestin vastaanoton aikainen latenssi on riippuvainen tietystä toteutuksesta. Latenssia voidaan kuitenkin optimoida käyttämällä tarkkoja digitaalisia suunnittelustrategioita.

Pohjimmiltaan on olemassa luontainen, väistämätön latenssi, joka johtuu FEC-mekanismista ja fyysisestä etäisyydestä tai kaapelin pituudesta. Näiden tekijöiden lisäksi suunnitteluosaamisella on keskeinen rooli Ethernet-ohjaimen viiveen minimoimisessa. Täydellisen ratkaisun hyödyntäminen, joka integroi ja optimoi MAC:n, PCS:n ja PHY:n, tasoittaa tietä tehokkaimmalle, alhaisen latenssin toteutukselle.

Yhteenveto

Kuva 4: Synopsys 224G Ethernet PHY IP:n ensimmäisen kierron piin menestys 3nm:n prosessissa, jossa on erittäin lineaariset PAM-4-silmät.

1.6 Tbps Ethernet on räätälöity kaikkein kaistanleveyttä vaativimpiin ja viiveherkimpiin sovelluksiin. 224G SerDes -teknologian ja MAC- ja PCS IP -kehitysten myötä saatavilla on nyt kattavia ratkaisuja, jotka ovat jatkuvasti kehittyvien 1.6T Ethernet -standardien mukaisia. Lisäksi protokollalle ja virheenkorjausmenetelmille ominaisen latenssin vuoksi asiantuntijasuunnittelijoiden on suunniteltava huolellisesti IP-digitaalinen ja analoginen suunnittelu, jotta vältytään tarpeettomasta latenssista tietopolulle.

Huippusuorituskyvyn saavuttaminen 1.6T SoC -malleissa edellyttää tehokkaasti optimoitua arkkitehtuuria ja huolellisia suunnittelukäytäntöjä jokaiselle sirukomponentille. Tämä korostaa virransäästöä ja minimoi piijalanjäljen, mikä tekee 1.6 T:n tiedonsiirtonopeudesta todellisuutta. Piin testattu Synopsys 224G Ethernet PHY IP on asettanut vaiheen 1.6T MAC- ja PCS-ohjaimelle. Käyttämällä huippuluokan suunnittelu-, analyysi-, simulointi- ja mittaustekniikoita, Synopsys tarjoaa edelleen poikkeuksellista signaalin eheyttä ja värinää. täydellinen Ethernet-ratkaisu, mukaan lukien MAC+PCS+PHY.

- SEO-pohjainen sisällön ja PR-jakelu. Vahvista jo tänään.

- PlatoData.Network Vertical Generatiivinen Ai. Vahvista itseäsi. Pääsy tästä.

- PlatoAiStream. Web3 Intelligence. Tietoa laajennettu. Pääsy tästä.

- PlatoESG. hiili, CleanTech, energia, ympäristö, Aurinko, Jätehuolto. Pääsy tästä.

- PlatonHealth. Biotekniikan ja kliinisten kokeiden älykkyys. Pääsy tästä.

- Lähde: https://semiengineering.com/latency-considerations-for-1-6t-ethernet-designs/

- :on

- :On

- :ei

- :missä

- $ YLÖS

- 1

- 12

- 16

- 2024

- 2026

- 212

- 220

- 362

- 500

- 8

- a

- pääsy

- saatavilla

- kirjanpito

- tarkka

- Saavuttaa

- poikki

- toiminta

- lisä-

- lisä-

- Lisäksi

- hyväksymällä

- edistysaskeleet

- etenee

- vastaan

- Tähtäimessä

- sallittu

- jo

- Myös

- Vaikka

- aina

- keskellä

- määrät

- vahvistaa

- an

- analyysi

- ja

- ennakoitua

- Hakemus

- sovellukset

- lähestymistapa

- arkkitehtuuri

- OVAT

- AS

- At

- välttää

- Back-end

- taustakulissi

- kaistanleveys

- BE

- tulee

- välillä

- Jälkeen

- Bitti

- Tukkia

- vahvistaa

- lisäämällä

- Tuo

- rakentaa

- mutta

- by

- kaapeli

- kaapelit

- CAN

- valmiuksia

- kuljettaa

- haasteet

- kanavat

- siru

- sirut

- valittu

- olosuhteet

- asiakas

- kello

- pilvi

- cloud computing

- koodi

- yhdistetty

- yhdistely

- Viestintä

- täydellinen

- valmistuminen

- komponentti

- osat

- kattava

- joka käsittää

- tietojenkäsittely

- Koskea

- yhdessä

- kytketty

- Liitännät

- CONSERVATION

- Harkita

- näkökohdat

- johdonmukainen

- jatkuu

- jatkuvasti

- edistävät

- ohjaus

- ohjain

- Muuntaminen

- Kupari

- Ydin

- kustannukset

- ehkäistä

- kurssi

- muotoillun

- luo

- Nykyinen

- tiedot

- Datacenter

- debyytti

- viiveet

- toimittaa

- Kysyntä

- vaativa

- vaatii

- kuvaava

- Malli

- suunnittelijat

- mallit

- Detection

- Laitteet

- sanelee

- eri

- digitaalinen

- ahkerasti

- näytöt

- etäisyys

- jaettu

- ei

- kaksinkertaistui

- kaksi

- kesto

- aikana

- kukin

- Aikaisemmin

- ekosysteemi

- Tehokas

- tehokkaasti

- tehokkuus

- tehokas

- tehokkaasti

- ponnisteluja

- syntyminen

- painottaa

- korostaen

- Työllisiä

- käyttämällä

- mahdollistaa

- mahdollistaa

- kattaa

- loppu

- päittäin

- varmistaa

- Koko

- virhe

- virheet

- laajenemisen

- ydin

- olennainen

- olennaisesti

- Eetteri (ETH)

- Jopa

- Joka

- ilmeinen

- kehittyvä

- esimerkki

- poikkeuksellinen

- ulkopuolelle

- laajenee

- laajeneminen

- odotettu

- asiantuntija

- asiantuntemus

- laajentaa

- ulottuu

- ulkoinen

- uuttaminen

- katse

- tekijä

- tekijät

- paljon

- nopeampi

- Ominaisuudet

- Featuring

- Kuva

- Löytää

- Etunimi

- Ensimmäinen sukupolvi

- virtaus

- keskityttiin

- seurannut

- Jalanjälki

- varten

- muotoilu

- Eteenpäin

- FRAME

- alkaen

- edelleen

- sukupolvi

- antaa

- suurempi

- Ryhmä

- Ryhmän

- Kasvava

- käsi

- Käsittely

- Korkea

- korkea suorituskyky

- erittäin

- Kuitenkin

- HTML

- HTTPS

- imperatiivi

- täytäntöönpano

- merkitys

- tärkeä

- parani

- in

- Muilla

- sisältää

- Mukaan lukien

- lisää

- henkilökohtainen

- teollinen

- vaikuttaneet

- luontainen

- luonnostaan

- aloittaa

- aloite

- esimerkki

- integroi

- integraatio

- eheys

- liitäntä

- rajapinnat

- Internet

- Interoperability

- tulee

- luontainen

- esitellä

- Esittelee

- käyttöön

- liittyy

- IP

- IT

- toistojen

- SEN

- itse

- jpg

- kaista

- Viive

- kerros

- kerrokset

- Pituus

- tasot

- vipuvaikutuksen

- Todennäköisesti

- linja

- linjat

- LINK

- linkit

- elää

- kauemmin

- Matala

- mac

- Tekeminen

- hoitaa

- johto

- max-width

- maksimi

- Saattaa..

- tarkoittaa

- mittaus

- mekanismi

- keskikokoinen

- Muisti

- viesti

- menetelmä

- menetelmät

- huolellinen

- minimi

- minimoida

- minimoi

- minimointia

- moduuli

- Moduulit

- lisää

- eniten

- täytyy

- loppusuoralla

- Tarve

- verkot

- silti

- Nro

- huomata

- nyt

- tavoite

- of

- usein

- on

- ONE

- vain

- toiminta

- optimoitu

- Optimismi

- Vaihtoehto

- or

- Muut

- yli

- yleinen

- paria

- parametrit

- erityisesti

- polku

- PC

- varten

- suorituskyky

- Esitykset

- fyysinen

- fyysisesti

- putki

- keskeinen

- Platon

- Platonin tietotieto

- PlatonData

- soittaa

- plus

- mahdollinen

- teho

- käytännöt

- pääasiallisesti

- ensisijainen

- prosessi

- käsittely

- prosessorit

- eteneminen

- ennustetaan

- suojaus

- protokolla

- pulssi

- tarkoitus

- Työnnä

- laatu

- radio

- satunnainen

- alue

- hinta

- Hinnat

- tavoittaa

- päästäisiin

- reaktio

- Todellisuus

- vastaanottaa

- vastaanottava

- vastaanotto

- vähentämällä

- luotettava

- jäännökset

- mallinnus

- Vaatii

- rajoitettu

- Saatu ja

- luja

- Rooli

- juurtunut

- juoksu

- skaalautuvuus

- Asteikko

- skenaariot

- saumaton

- Toinen

- nähneet

- segmentti

- sensible

- erillinen

- palvella

- palvelu

- setti

- useat

- yhteinen

- Lyhyt

- shouldnt

- esittelylle

- signaali

- merkittävästi

- Pii

- simulointi

- Koko

- So

- ratkaisu

- Ratkaisumme

- jännevälien

- kärjessä

- erityinen

- erityisesti

- määrittely

- nopeudet

- kevät

- Vaihe

- standardi

- standardointi

- standardit

- Levytila

- strategiat

- streaming

- myöhempi

- merkittävä

- menestys

- niin

- sopiva

- tuki

- symboli

- järjestelmä

- Räätälöity

- vie

- tekniikka

- tekniikat

- Elektroniikka

- kuin

- että

- -

- heidän

- Siellä.

- siten

- siksi

- Nämä

- tätä

- Kautta

- Näin

- rasti

- tied

- aika

- kertaa

- että

- ylin

- perinteinen

- liikenne

- siirtää

- lähettää

- Kolminkertaistaa

- kaksi

- tyypillinen

- tyypillisesti

- väistämätön

- ymmärtäminen

- sitoutuvat

- yksikkö

- tuleva

- päälle

- käyttämällä

- käyttää

- kautta

- havainnollistaa

- Tapa..

- we

- kun

- joka

- vaikka

- laajempi

- with

- sisällä

- olisi

- vielä

- zephyrnet

- nolla-