Chiplets on yksinkertaistanut yhtä suunnittelualuetta, mutta avannut Pandoran lippaan toisella puolella. Jokaisen simulaation monimutkaisuus siru on pienempi, mutta nyt sirujen välisestä yhteydestä on tullut monimutkainen. Ihmiset kokeilevat erilaisia yhteenliittämisprotokollia, UCIe:n muunnelmia, UCIe-asetusten, rajapintojen nopeuksien, fyysisten kerrosten lukumäärän ja niin edelleen muokkaamista. Lisää nyt sekoitukseen vanhoja standardeja, kuten AXI, uusia protokollia, kuten PICe6.0, ja välimuistin johdonmukaisuutta.

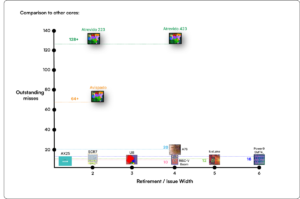

Kaiken kaikkiaan tämä luo täysin uudenlaisia kokeiluja. Sellainen, jossa perinteinen emulointi ja RTL-mallinnus eivät toimi. Sinun on ensin ponnisteltava arkkitehtuurin kompromisseihin, ei vain komponenttien valintaan. Tämä tarkoittaa, että sinun on suoritettava liikenneanalyysi, sovellusten osiointi, järjestelmän koko ja erilaisten fyysisten kerrosten vaikutus. Myös sovelluksesta riippuen vertailuarvo on hyvin erilainen.

UCIe-spesifikaatio on uusi, eikä siinä ole selkeitä vertailuarvoja. Lisäksi UCIe-spesifikaatio antaa vain ohjeita viiveestä ja tehosta. Molemmat ovat tiukkoja vaatimuksia. Tämä tarkoittaa, että Power-Performance-Area -tutkimus on välttämätön. Koska sinulla on protokolla-protokolla-protokolla-muunnos, kuten PCIe 6.0:sta UCIe:ksi AXI:ksi, mallinnusasetukset ovat monimutkaiset.

Yksi ratkaisu on tarkastella järjestelmän mallintamista VisualSim alkaen mirabilis Design. He ovat äskettäin julkaisseet UCIe-järjestelmätason IP-mallin ja esittelevät useita yhteenliittämisen käyttötapauksia Chiplet Summit. Suunnittelijoiden ohjaamiseksi he ovat julkaisseet oppaan, jossa on paljon käyttötapauksia, odotettavissa olevia teho-suorituskykytuloksia ja optimointivaihtoehtoja. Heillä on sekä paperiesitys että osasto huippukokouksessa. Toivottavasti nähdään siellä!

Tässä on myös linkki paperiin, jonka ihmiset voivat saada: UCIe Interconnect -arkkitehtuuriin perustuva heterogeenisen laskentajärjestelmän suorituskyvyn mallinnus

Tiivistelmä:

Nykypäivän monimutkaiset sirusuunnittelut eturivin solmuissa koostuvat yleensä useista muotteista (tai siruista). Lähestymistapa mahdollistaa eri valmistajien tai prosessien muotit sekä uudelleenkäytettävän IP:n. Suunnittelijat tarvitsevat järjestelmätason mallin arvioidakseen tällaisten monimutkaisten tilanteiden erilaisia toteutuksia.

Esimerkkijärjestelmä koostuu I/O-sirusta, pienitehoisesta ydinsirusta, korkean suorituskyvyn ydinsirusta, audio-video-sirusta ja analogisesta piirilevystä, jotka on yhdistetty Universal Chiplet Interconnect Express (UCIe) -standardin avulla.

Tiimimme harkitsi useita skenaarioita ja kokoonpanoja, mukaan lukien edistyneitä ja vakiopaketteja, erilaisia liikenneprofiileja ja resursseja sekä aikakatkaisijaa kattavuuden laajentamiseksi ja tapahtumien arvioimiseksi aikakatkaisun aikana. Tehtäväsovellusten UCIe-yhdysliitännän vahvuuksien ja heikkouksien tunnistaminen auttoi meitä saamaan kullekin osajärjestelmälle optimaalisen kokoonpanon suorituskyvyn, tehon ja toiminnallisten vaatimusten täyttämiseksi.

Tietoja: Mirabilis Design Inc.

Mirabilis Design on Piilaakson ohjelmistoyritys, joka tarjoaa ohjelmisto- ja koulutusratkaisuja tuotespesifikaatioiden riskien tunnistamiseen ja eliminoimiseen, ennakoiden tarkasti tuotteen kehittämiseen tarvittavat henkilö- ja aikaresurssit ja parantavat kommunikaatiota erilaisten suunnittelutoimien välillä.

joukkueet.

VisualSim Architect yhdistää henkisen omaisuuden, järjestelmätason mallinnuksen, simuloinnin, ympäristöanalyysin ja sovellusmallit parantaakseen merkittävästi mallin rakentamista, simulointia, analysointia ja RTL-varmennusta. Ympäristön ansiosta suunnittelijat voivat siirtyä nopeasti suunnitelmaan, joka täyttää erilaiset toisistaan riippuvat aika- ja tehovaatimukset. Sitä käytetään hyvin varhaisessa suunnitteluprosessissa kirjallisen spesifikaation rinnalla (ja apuna) ennen tuotteen käyttöönottoa (esimerkiksi RTL, ohjelmistokoodi tai kaavio).

Lue myös:

WEBINAARI: Kuinka saavuttaa 95 %+ tarkka tehomittaus arkkitehtuuritutkimuksen aikana

SysML:n yhdistäminen laitteistoarkkitehtuuriin

Mallipohjaiset suunnittelukurssit opiskelijoille

Jaa tämä viesti:

- SEO-pohjainen sisällön ja PR-jakelu. Vahvista jo tänään.

- PlatoData.Network Vertical Generatiivinen Ai. Vahvista itseäsi. Pääsy tästä.

- PlatoAiStream. Web3 Intelligence. Tietoa laajennettu. Pääsy tästä.

- PlatoESG. hiili, CleanTech, energia, ympäristö, Aurinko, Jätehuolto. Pääsy tästä.

- PlatonHealth. Biotekniikan ja kliinisten kokeiden älykkyys. Pääsy tästä.

- Lähde: https://semiwiki.com/ip/mirabilis-design-ip/341339-chiplets-open-pandoras-box/

- :on

- :On

- :ei

- a

- tarkka

- tarkasti

- Saavuttaa

- lisätä

- kehittynyt

- Tuki

- mahdollistaa

- pitkin

- Myös

- an

- analyysi

- ja

- Toinen

- Hakemus

- sovellukset

- lähestymistapa

- arkkitehtuuri

- OVAT

- ALUE

- AS

- At

- perustua

- BE

- tulevat

- ennen

- benchmark

- Viitearvot

- välillä

- sekä

- Laatikko

- mutta

- kätkö

- CAN

- Voi saada

- tapauksissa

- siru

- selkeä

- koodi

- yhdistää

- Viestintä

- yritys

- täysin

- monimutkainen

- monimutkaisuus

- osat

- tietojenkäsittely

- Suorittaa

- Konfigurointi

- harkittu

- muodostuu

- rakentaminen

- suppenee

- Muuntaminen

- Ydin

- kurssit

- luo

- esittelyssä

- Riippuen

- Malli

- suunnitteluprosessi

- suunnittelijat

- mallit

- kehittää

- eri

- useat

- aikana

- kukin

- Varhainen

- vaivaa

- poistaa

- jäljittely

- mahdollistaa

- ympäristö

- arvioida

- Tapahtumat

- esimerkki

- odotettu

- kokeileminen

- kokeiluja

- ilmaista

- laajentaa

- Etunimi

- varten

- alkaen

- etuosa

- toiminnallinen

- yleensä

- saada

- ohjaus

- ohjaavat

- Palvelimet

- Olla

- auttanut

- tätä

- korkea suorituskyky

- toivoa

- Miten

- Miten

- HTTPS

- ihmisen

- i

- tunnistaa

- tunnistaminen

- Vaikutus

- täytäntöönpano

- toteutukset

- parantaa

- in

- Mukaan lukien

- henkinen

- tekijänoikeuksien

- toisiinsa

- liitäntä

- IP

- IT

- jpg

- vain

- Viive

- käynnistettiin

- kerros

- kerrokset

- Perintö

- Taso

- pitää

- LINK

- katso

- erien

- Matala

- alentaa

- Valmistajat

- max-width

- tarkoittaa

- välineet

- mittaus

- Tavata

- Meets

- Tehtävä

- sekoittaa

- malli

- mallintaminen

- mallintaminen

- moninkertainen

- Tarve

- Uusi

- Nro

- solmut

- nyt

- numero

- saada

- of

- on

- ONE

- vain

- avata

- avattu

- optimaalinen

- optimointi

- Vaihtoehdot

- or

- paketit

- Paperi

- Parallel

- suorituskyky

- fyysinen

- Platon

- Platonin tietotieto

- PlatonData

- Kirje

- teho

- ennustamiseen

- esitys

- prosessi

- Prosessit

- Tuotteet

- Profiilit

- omaisuus

- protokollat

- tarjoaa

- tarjoamalla

- julkaistu

- nopeasti

- tavoittaa

- Lue

- äskettäin

- tarvitaan

- vaatimukset

- Esittelymateriaalit

- tulokset

- uudelleen käytettävä

- Riski

- skenaariot

- nähdä

- valitsemalla

- setti

- settings

- setup

- useat

- merkittävästi

- Pii

- Silicon Valley

- yksinkertaistettu

- simulointi

- tilanteita

- So

- Tuotteemme

- ratkaisu

- Ratkaisumme

- määrittely

- nopeudet

- viettää

- standardi

- standardit

- vahvuudet

- tiukka

- tutkimus

- niin

- Huippukokous

- järjestelmä

- joukkue-

- malleja

- että

- -

- Siellä.

- ne

- tätä

- aika

- että

- perinteinen

- liikenne

- koulutus

- tyypit

- Yleismaailmallinen

- us

- käyttää

- käytetty

- käyttämällä

- Laakso

- vaihtelut

- Vahvistus

- hyvin

- kautta

- heikkouksia

- HYVIN

- joka

- tulee

- with

- Referenssit

- kirjallinen

- te

- zephyrnet