کارشناسان حاضر در میز: مهندسی نیمه هادی با فرانک فرو، مدیر گروه، مدیریت محصول در مورد مسیر رو به جلو برای حافظه در سیستم های ناهمگن صحبت کردند. آهنگ; استیون وو، همکار و مخترع برجسته در Rambus; جونگسین یون، تکنسین حافظه در زیمنس EDA; رندی وایت، مدیر برنامه راه حل های حافظه در دیدگاه اصلی; و فرانک شرمایستر، معاون راه حل ها و توسعه کسب و کار در شریان. آنچه در ادامه می آید گزیده ای از این گفتگو است. بخش اول این بحث را می توان یافت اینجا کلیک نمایید.

![[LR]: فرانک فرو، کادنس؛ استیون وو، رامبوس؛ جونگسین یون، زیمنس EDA؛ رندی وایت، Keysight; و فرانک شرمایستر، آرتریس.](https://platoaistream.com/wp-content/uploads/2024/01/rethinking-memory.png)

[LR]: فرانک فرو، کادنس؛ استیون وو، رامبوس؛ جونگسین یون، زیمنس EDA؛ رندی وایت، Keysight; و فرانک شرمایستر، آرتریس

SE: همانطور که ما با AI/ML و نیازهای قدرت مبارزه می کنیم، چه پیکربندی هایی باید تجدید نظر شود؟ آیا شاهد دور شدن از معماری فون نویمان خواهیم بود؟

وو: از نظر معماری سیستم، یک انشعاب در صنعت در حال وقوع است. برنامههای کاربردی سنتی که اسبهای کاری غالب هستند، که ما در فضای ابری روی سرورهای مبتنی بر x86 اجرا میکنیم، از بین نمیروند. چندین دهه نرم افزاری وجود دارد که ساخته شده و تکامل یافته است و برای عملکرد خوب به آن معماری تکیه می کند. در مقابل، AI/ML یک کلاس جدید است. مردم معماریها را بازاندیشی کردهاند و پردازندههای بسیار خاص دامنه را ساختهاند. ما می بینیم که حدود دو سوم انرژی صرف جابجایی داده ها بین یک پردازنده و یک دستگاه HBM می شود، در حالی که تنها حدود یک سوم صرف دسترسی واقعی به بیت ها در هسته های DRAM می شود. حرکت داده ها اکنون بسیار چالش برانگیزتر و پرهزینه تر است. ما قصد نداریم از شر حافظه خلاص شویم. ما به آن نیاز داریم زیرا مجموعه داده ها بزرگتر می شوند. بنابراین سوال این است که "راه درست برای آینده چیست؟" بحث های زیادی در مورد انباشته شدن وجود دارد. اگر بخواهیم آن حافظه را برداریم و مستقیماً روی پردازنده قرار دهیم، دو کار را برای شما انجام می دهد. اولاً، پهنای باند امروزه توسط ساحل یا محیط تراشه محدود شده است. اینجاست که I/Oها می روند. اما اگر قرار بود آن را مستقیماً در بالای پردازنده قرار دهید، اکنون می توانید از کل منطقه تراشه برای اتصالات توزیع شده استفاده کنید و می توانید پهنای باند بیشتری را در خود حافظه دریافت کنید و می تواند مستقیماً به پایین وارد شود. پردازنده لینکها بسیار کوتاهتر میشوند و بهرهوری انرژی احتمالاً بین ۵ برابر تا ۶ برابر افزایش مییابد. دوم اینکه، مقدار پهنای باندی که میتوانید به دلیل اتصال آرایههای مساحت بیشتر به حافظه به دست آورید، با چندین ضریب صحیح افزایش مییابد. انجام این دو کار با هم می تواند پهنای باند بیشتری را فراهم کند و مصرف انرژی را افزایش دهد. صنعت به هر نیازی که باشد تکامل مییابد، و این قطعا یکی از راههایی است که در آینده شاهد تکامل سیستمهای حافظه خواهیم بود تا بازده انرژی بیشتری داشته باشند و پهنای باند بیشتری ارائه کنند.

اهن: هنگامی که من برای اولین بار کار بر روی HBM را در حدود سال 2016 شروع کردم، برخی از مشتریان پیشرفته تر پرسیدند که آیا می توان آن را روی هم قرار داد. آنها مدت زیادی است که به دنبال نحوه قرار دادن DRAM در بالا بوده اند زیرا مزایای واضحی وجود دارد. از لایه فیزیکی، PHY اساساً ناچیز می شود، که باعث صرفه جویی زیادی در مصرف انرژی و کارایی می شود. اما اکنون شما یک پردازنده 100 واتی دارید که یک حافظه در بالای آن دارد. حافظه نمی تواند گرما را تحمل کند. این احتمالا ضعیف ترین حلقه در زنجیره گرما است که چالش دیگری را ایجاد می کند. مزایایی وجود دارد، اما آنها هنوز باید نحوه برخورد با گرما را بیابند. در حال حاضر انگیزه بیشتری برای پیشبرد این نوع معماری وجود دارد، زیرا واقعاً به طور کلی از نظر عملکرد و قدرت شما را نجات می دهد و کارایی محاسباتی شما را بهبود می بخشد. اما برخی از چالشهای طراحی فیزیکی وجود دارد که باید با آنها مقابله کرد. همانطور که استیو می گفت، ما انواع معماری ها را می بینیم که در حال بیرون آمدن هستند. من کاملاً موافقم که معماریهای GPU/CPU به جایی نمیرسند، آنها همچنان غالب خواهند بود. در همان زمان، هر شرکتی در این سیاره در تلاش است تا تله موش بهتری برای انجام هوش مصنوعی خود بیابد. ما شاهد SRAM روی تراشه و ترکیبی از حافظه با پهنای باند بالا هستیم. LPDDR این روزها در مورد نحوه استفاده از LPDDR در مرکز داده به دلیل قدرت زیاد سر خود را بالا برده است. ما حتی شاهد استفاده از GDDR در برخی از برنامه های استنتاج هوش مصنوعی و همچنین تمام سیستم های حافظه قدیمی بوده ایم. آنها اکنون در حال تلاش برای فشرده کردن هرچه بیشتر DDR5 بر روی یک ردپایی هستند. من هر معماری که فکرش را بکنید دیده ام، خواه آن معماری DDR، HBM، GDDR یا موارد دیگر. این به هسته پردازنده شما بستگی دارد که ارزش افزوده کلی شما چقدر است و سپس چگونه می توانید از معماری خاص خود عبور کنید. سیستم حافظه ای که با آن همراه است، بنابراین می توانید CPU و معماری حافظه خود را، بسته به آنچه در دسترس است، مجسمه سازی کنید.

یون: مسئله دیگر عدم نوسان است. برای مثال، اگر هوش مصنوعی مجبور باشد با فاصله زمانی بین اجرای یک هوش مصنوعی مبتنی بر اینترنت اشیا مقابله کند، ما نیاز به خاموش و روشن کردن انرژی زیادی داریم و همه این اطلاعات برای آموزش هوش مصنوعی باید بارها و بارها بچرخند. اگر نوع راهحلهایی داشته باشیم که بتوانیم آن وزنها را در تراشه ذخیره کنیم تا مجبور نباشیم همیشه برای همان وزن به جلو و عقب حرکت کنیم، در این صورت صرفهجویی زیادی در مصرف انرژی بهویژه برای هوش مصنوعی مبتنی بر اینترنت اشیا خواهد بود. راه حل دیگری برای کمک به این نیازهای قدرت وجود خواهد داشت.

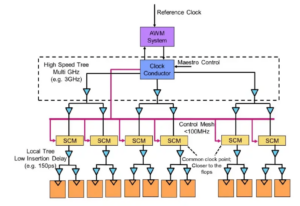

Schirrmeister: چیزی که از دیدگاه NoC برای من جذاب است، جایی است که شما باید این مسیرها را از پردازندهای که از NoC عبور میکند، بهینه کنید، به یک رابط حافظه با کنترلکنندهای که به طور بالقوه از طریق UCIe میگذرد تا یک چیپلت را به چیپلت دیگری منتقل کنید، که پس از آن حافظه در آن وجود دارد. آی تی. اینطور نیست که معماری های فون نیومن مرده باشند. اما اکنون بسته به حجم کاری که می خواهید محاسبه کنید، تغییرات زیادی وجود دارد. آنها باید در چارچوب حافظه مورد توجه قرار گیرند و حافظه تنها یک جنبه است. از کجا داده ها را از محل داده دریافت می کنید، چگونه در این DRAM مرتب شده است؟ ما در حال کار روی همه این موارد هستیم، مانند تجزیه و تحلیل عملکرد حافظه ها و سپس بهینه سازی معماری سیستم روی آن. این نوآوریهای زیادی را برای معماریهای جدید برانگیخته است، که وقتی در دانشگاه بودم و در مورد فون نویمان یاد میگرفتم هرگز به آن فکر نمیکردم. در انتهای دیگر، چیزهایی مانند مش ها دارید. در حال حاضر معماریهای بسیار بیشتری در این بین وجود دارد که باید در نظر گرفته شوند، و این به دلیل پهنای باند حافظه، قابلیتهای محاسباتی و غیره است که با سرعت یکسانی رشد نمیکند.

سفید: روندی وجود دارد که شامل محاسبات تفکیک شده یا محاسبات توزیع شده است، به این معنی که معمار باید ابزارهای بیشتری در اختیار داشته باشد. سلسله مراتب حافظه گسترش یافته است. Semantics شامل CXL و حافظه های ترکیبی مختلف است که برای فلش و DRAM در دسترس هستند. یک برنامه موازی با مرکز داده، خودروسازی است. خودرو همیشه این حسگر را با ECU (واحدهای کنترل الکترونیکی) محاسبه می کرد. من مجذوب نحوه تبدیل آن به مرکز داده هستم. به سرعت به جلو، و امروز ما گره های محاسباتی، به نام کنترل کننده دامنه، توزیع کرده ایم. همین موضوع است. این تلاش میکند تا به این موضوع بپردازد که شاید قدرت آنقدرها هم مهم نباشد، زیرا مقیاس رایانهها به این بزرگی نیست، اما تأخیر مطمئناً یک معامله بزرگ با خودرو است. ADAS به پهنای باند فوق العاده بالایی نیاز دارد و شما معاوضه های متفاوتی دارید. و سپس سنسورهای مکانیکی بیشتری دارید، اما محدودیتهای مشابهی در یک مرکز داده. شما یک فضای ذخیره سازی سرد دارید که نیازی به تأخیر کم ندارد، و سپس دیگر برنامه های کاربردی با پهنای باند بالا دارید. دیدن اینکه ابزارها و گزینههای معمار چقدر تکامل یافتهاند، شگفتانگیز است. این صنعت واقعاً کار خوبی در پاسخگویی انجام داده است و همه ما راه حل های مختلفی ارائه می دهیم که به بازار وارد می شود.

SE: ابزارهای طراحی حافظه چگونه تکامل یافته اند؟

Schirrmeister: وقتی در دهه 90 با اولین تراشههایم شروع کردم، پرکاربردترین ابزار سیستم اکسل بود. از آن زمان، من همیشه امیدوار بودم که ممکن است در یک نقطه برای کارهایی که ما در سطح سیستم، حافظه، تجزیه و تحلیل پهنای باند، و غیره انجام میدهیم، خراب شود. این خیلی روی تیم های من تأثیر گذاشت. در آن زمان، چیزهای بسیار پیشرفته ای بود. اما به نظر رندی، اکنون چیزهای پیچیده خاصی باید در سطحی از وفاداری شبیه سازی شوند که قبلاً بدون محاسبه امکان پذیر نبود. برای مثال، فرض یک تأخیر مشخص برای دسترسی DRAM میتواند منجر به تصمیمگیریهای بد در معماری و طراحی نادرست معماریهای انتقال داده بر روی تراشه شود. طرف مقابل نیز صادق است. اگر همیشه بدترین حالت را فرض کنید، معماری را بیش از حد طراحی خواهید کرد. داشتن ابزارهایی که DRAM و تجزیه و تحلیل عملکرد را انجام می دهند، و داشتن مدل های مناسب در دسترس برای کنترلرها به یک معمار اجازه می دهد تا همه آن را شبیه سازی کند، این یک محیط جذاب است. ابزار سطح سیستم ممکن است واقعاً محقق شود، زیرا برخی از تأثیرات پویا که دیگر نمیتوانید در اکسل انجام دهید، زیرا باید آنها را شبیهسازی کنید - به خصوص زمانی که یک رابط کاربری با ویژگیهای PHY را وارد میکنید و سپس لایه پیوند را وارد میکنید. ویژگی هایی مانند همه بررسی اینکه آیا همه چیز درست است و به طور بالقوه داده ها را دوباره ارسال می کند. انجام ندادن این شبیهسازیها منجر به معماری غیربهینه میشود.

اهن: اولین گام در اکثر ارزیابیهایی که انجام میدهیم این است که به آنها تست حافظه بدهیم تا شروع به بررسی کارایی DRAM کنند. این یک گام بزرگ است، حتی انجام کارهایی به سادگی اجرای ابزارهای محلی برای انجام شبیه سازی DRAM، اما سپس رفتن به شبیه سازی های کامل. ما می بینیم که مشتریان بیشتری برای آن نوع شبیه سازی درخواست می کنند. اطمینان از اینکه راندمان DRAM شما در دهه 90 بالا است، اولین قدم بسیار مهم در هر ارزیابی است.

وو: بخشی از دلیل ظهور ابزارهای شبیه سازی کامل سیستم این است که DRAM ها بسیار پیچیده تر شده اند. اکنون بسیار دشوار است که با استفاده از ابزارهای ساده ای مانند اکسل حتی در نوار برای برخی از این حجم های کاری پیچیده قرار بگیرید. اگر به دیتاشیت DRAM در دهه 90 نگاه کنید، آن برگه های داده مانند 40 صفحه بودند. اکنون آنها صدها صفحه هستند. این فقط از پیچیدگی دستگاه برای از بین بردن پهنای باند بالا صحبت می کند. این را با این واقعیت که حافظه در هزینه سیستم و همچنین پهنای باند و تأخیر مربوط به عملکرد پردازنده یک محرک است، جفت میکنید. همچنین یک محرک بزرگ در قدرت است، به طوری که اکنون باید در سطح بسیار دقیق تری شبیه سازی کنید. از نظر جریان ابزار، معماران سیستم می دانند که حافظه یک محرک بزرگ است. بنابراین ابزارها باید پیچیدهتر باشند، و باید به خوبی با ابزارهای دیگر ارتباط برقرار کنند تا معمار سیستم بهترین دید جهانی را از آنچه در حال وقوع است داشته باشد - بهویژه در مورد اینکه حافظه چگونه بر سیستم تأثیر میگذارد.

یون: همانطور که به عصر هوش مصنوعی می رویم، سیستم های چند هسته ای زیادی مورد استفاده قرار می گیرند، اما نمی دانیم کدام داده ها به کجا می روند. همچنین بیشتر به موازات تراشه پیش می رود. اندازه حافظه بسیار بزرگتر است. اگر از نوع ChatGPT از هوش مصنوعی استفاده کنیم، مدیریت دادهها برای مدلها به حدود 350 مگابایت داده نیاز دارد که مقدار زیادی داده فقط برای وزن است و ورودی/خروجی واقعی بسیار بزرگتر است. این افزایش در مقدار داده های مورد نیاز به این معنی است که اثرات احتمالی زیادی وجود دارد که قبلاً ندیده ایم. این یک تست بسیار چالش برانگیز برای دیدن تمام خطاهای مربوط به این حجم زیاد حافظه است. و ECC در همه جا استفاده می شود، حتی در SRAM، که به طور سنتی از ECC استفاده نمی کرد، اما اکنون برای بزرگترین سیستم ها بسیار رایج است. آزمایش برای همه این موارد بسیار چالش برانگیز است و باید توسط راه حل های EDA برای آزمایش همه آن شرایط مختلف پشتیبانی شود.

SE: تیم های مهندسی روزانه با چه چالش هایی روبرو هستند؟

سفید: در هر روز، مرا در آزمایشگاه خواهید یافت. آستینهایم را بالا میزنم و دستهایم را کثیف میکنم، سیمها را میکوبم، لحیم کاری میکنم و اینها. من در مورد اعتبارسنجی پس از سیلیکون فکر می کنم. ما در مورد شبیه سازی اولیه و ابزارهای روی مرگ - BiST و چیزهایی از این قبیل صحبت کردیم. در پایان روز، قبل از ارسال، میخواهیم نوعی اعتبارسنجی سیستم یا تستهای سطح دستگاه را انجام دهیم. ما در مورد چگونگی غلبه بر دیوار حافظه صحبت کردیم. ما حافظه، HBM، مواردی از این دست را با هم قرار می دهیم. اگر به تکامل فناوری بسته بندی نگاه کنیم، کار را با بسته های سرب دار شروع کردیم. آنها برای یکپارچگی سیگنال خیلی خوب نبودند. چند دهه بعد، ما به سمت یکپارچگی سیگنال بهینه شده، مانند آرایه های شبکه توپ (BGA) حرکت کردیم. ما نمی توانستیم به آن دسترسی داشته باشیم، به این معنی که شما نمی توانید آن را آزمایش کنید. بنابراین ما به این مفهوم رسیدیم که یک دستگاه interposer نامیده می شود - یک interposer BGA - و به ما امکان می دهد یک وسیله خاص را ساندویچ کنیم که سیگنال ها را به بیرون هدایت می کند. سپس میتوانیم آن را به تجهیزات آزمایشی وصل کنیم. به سرعت به امروز بروید و اکنون HBM و چیپلت ها را داریم. چگونه می توانم فیکسچر خود را در این بین روی اینترپوزر سیلیکونی قرار دهم؟ ما نمی توانیم و این مبارزه است. این چالشی است که مرا شب ها بیدار نگه می دارد. چگونه می توانیم تجزیه و تحلیل شکست را در زمینه با یک مشتری OEM یا سیستم انجام دهیم، جایی که آنها بازده 90٪ را ندارند. خطاهای بیشتری در پیوند وجود دارد، آنها نمی توانند به درستی مقداردهی اولیه کنند، و آموزش کار نمی کند. آیا مشکل یکپارچگی سیستم است؟

Schirrmeister: آیا ترجیح نمی دهید این کار را از خانه با یک رابط مجازی به جای پیاده روی به آزمایشگاه انجام دهید؟ آیا پاسخ، تجزیه و تحلیل بیشتری در تراشه نیست؟ با چیپلت ها، ما همه چیز را حتی بیشتر ادغام می کنیم. وارد کردن آهن لحیم کاری خود در آنجا واقعاً گزینه ای نیست، بنابراین باید راهی برای تجزیه و تحلیل روی تراشه وجود داشته باشد. برای NoC هم همین مشکل را داریم. مردم به NoC نگاه می کنند، و شما داده ها را ارسال می کنید و سپس از بین می روند. ما نیاز به تجزیه و تحلیل داریم تا افراد بتوانند اشکالزدایی را انجام دهند، و این به سطح تولید گسترش مییابد تا در نهایت بتوانید از خانه کار کنید و همه آنها را بر اساس تجزیه و تحلیل تراشه انجام دهید.

اهن: به خصوص با حافظه با پهنای باند بالا، شما نمی توانید از نظر فیزیکی وارد آن شوید. وقتی مجوز PHY را میدهیم، محصولی داریم که با آن مطابقت دارد، بنابراین میتوانید به تک تک آن ۱۰۲۴ بیت توجه کنید. می توانید خواندن و نوشتن DRAM را از این ابزار شروع کنید تا مجبور نباشید وارد آن شوید. من ایده interposer را دوست دارم. ما در حین آزمایش تعدادی پین را از interposer خارج می کنیم که در سیستم نمی توانید انجام دهید. ورود به این سیستم های سه بعدی واقعاً یک چالش است. حتی از نقطه نظر جریان ابزار طراحی، به نظر می رسد که اکثر شرکت ها جریان فردی خود را روی بسیاری از این ابزارهای 1,024 بعدی انجام می دهند. ما شروع به ایجاد یک راه استانداردتر برای ساختن یک سیستم 3 بعدی، از یکپارچگی سیگنال، قدرت، و کل جریان کرده ایم.

سفید: همانطور که همه چیز ادامه دارد، امیدوارم بتوانیم همچنان همان سطح دقت را حفظ کنیم. من در گروه انطباق فاکتور فرم UCIe هستم. من به دنبال این هستم که چگونه یک قالب خوب شناخته شده، یک قالب طلایی را مشخص کنم. در نهایت، این زمان بسیار بیشتری طول میکشد، اما ما میخواهیم میان عملکرد و دقت آزمایشی که به آن نیاز داریم و انعطافپذیری که در آن تعبیه شده است، واسطهای خوشایند پیدا کنیم.

Schirrmeister: اگر من به چیپلت ها و پذیرش آنها در یک محیط تولید بازتر نگاه کنم، آزمایش یکی از چالش های بزرگ در راه درست کردن آن است. اگر من یک شرکت بزرگ هستم و همه جوانب آن را کنترل میکنم، میتوانم کارها را بهطور مناسب محدود کنم تا آزمایش و غیره امکانپذیر شود. اگر بخواهم به شعار UCIe بروم که UCI تنها یک حرف با PCI فاصله دارد و آیندهای را تصور کنم که مونتاژ UCIe از منظر تولید مانند اسلاتهای PCI در رایانههای شخصی امروزی میشود، آنگاه جنبههای تست آن واقعاً هستند. چالش برانگیز. باید راه حلی پیدا کنیم. کارهای زیادی برای انجام دادن وجود دارد.

مقالات مرتبط

آینده حافظه (قسمت 1 از بالا گرد)

از تلاشها برای حل مسائل حرارتی و برق گرفته تا نقشهای CXL و UCIe، آینده فرصتهای زیادی برای حافظه دارد.

- محتوای مبتنی بر SEO و توزیع روابط عمومی. امروز تقویت شوید.

- PlatoData.Network Vertical Generative Ai. به خودت قدرت بده دسترسی به اینجا.

- PlatoAiStream. هوش وب 3 دانش تقویت شده دسترسی به اینجا.

- PlatoESG. کربن ، CleanTech، انرژی، محیط، خورشیدی، مدیریت پسماند دسترسی به اینجا.

- PlatoHealth. هوش بیوتکنولوژی و آزمایشات بالینی. دسترسی به اینجا.

- منبع: https://semiengineering.com/rethinking-memory/

- : دارد

- :است

- :نه

- :جایی که

- $UP

- 1

- 2016

- 3d

- 40

- a

- درباره ما

- بالاتر

- دسترسی

- دسترسی

- دقت

- واقعی

- واقعا

- ADA ها

- اضافه کردن

- نشانی

- اتخاذ

- پیشرفته

- مزیت - فایده - سود - منفعت

- مزایای

- از نو

- AI

- آموزش هوش مصنوعی

- AI / ML

- معرفی

- مجاز

- اجازه می دهد تا

- همچنین

- همیشه

- مقدار

- an

- تحلیل

- علم تجزیه و تحلیل

- و

- دیگر

- پاسخ

- هر

- دیگر

- هر جا

- کاربرد

- برنامه های کاربردی

- به درستی

- معماران

- معماری

- هستند

- محدوده

- دور و بر

- مرتب شده اند

- صف

- AS

- خواهان

- ظاهر

- جنبه

- مجلس

- فرض

- At

- تلاشها

- خودرو

- در دسترس

- دور

- به عقب

- بد

- توپ

- پهنای باند

- بار

- مستقر

- اساسا

- اساس

- BE

- زیرا

- شدن

- شود

- بوده

- قبل از

- بودن

- مزایای

- بهترین

- بهتر

- میان

- بزرگ

- بزرگتر

- بیت

- شکستن

- به ارمغان بیاورد

- ساختن

- ساخته

- کسب و کار

- توسعه تجاری

- اما

- by

- آهنگ

- نام

- آمد

- CAN

- می توانید دریافت کنید

- قابلیت های

- مورد

- مرکز

- معین

- قطعا

- زنجیر

- به چالش

- چالش ها

- به چالش کشیدن

- مشخصات

- مشخص کردن

- بررسی

- تراشه

- چیپس

- کلاس

- واضح

- ابر

- سرد

- ذخیره سازی سرد

- ترکیب

- بیا

- آینده

- مشترک

- شرکت

- شرکت

- پیچیده

- پیچیدگی

- انطباق

- بغرنج

- محاسبه

- کامپیوتر

- محاسبه

- مفهوم

- شرایط

- اتصال

- در نظر گرفته

- محدودیت ها

- زمینه

- کنتراست

- کنترل

- کنترل کننده

- گفتگو

- هسته

- اصلاح

- هزینه

- میتوانست

- زن و شوهر

- پردازنده

- ایجاد

- مشتری

- مشتریان

- داده ها

- مرکز داده

- مجموعه داده ها

- روز

- روز به روز

- روز

- مرده

- مقدار

- دهه

- تصمیم گیری

- قطعا

- خواسته

- بستگی دارد

- بستگی دارد

- طرح

- طراحی

- دقیق

- پروژه

- دستگاه

- مردن

- مختلف

- مشکل

- مستقیما

- مدیر

- گفتگو

- دسترس

- برجسته

- توزیع شده

- محاسبات توزیع شده

- do

- میکند

- نمی کند

- عمل

- دامنه

- غالب

- انجام شده

- آیا

- پایین

- رانده

- راننده

- در طی

- پویا

- در اوایل

- اثرات

- بهره وری

- موثر

- الکترونیکی

- پایان

- انرژی

- مهندسی

- تمام

- محیط

- تجهیزات

- عصر

- خطاهای

- به خصوص

- اتر (ETH)

- ارزیابی

- ارزیابی

- حتی

- در نهایت

- هر

- همه چیز

- در همه جا

- تکامل

- تکامل یابد

- تکامل

- تکامل می یابد

- مثال

- اکسل

- منبسط

- گران

- گسترش می یابد

- مفرط

- خیلی

- چشم ها

- چهره

- واقعیت

- عامل

- شکست

- شگفت انگیز

- FAST

- امکان پذیر است

- همکار

- وفاداری

- رشته

- شکل

- سرانجام

- پیدا کردن

- نام خانوادگی

- فلاش

- انعطاف پذیری

- فلیپ

- جریان

- به دنبال آن است

- رد پا

- برای

- فرم

- چهارم

- به جلو

- یافت

- رک

- از جانب

- کامل

- بیشتر

- آینده

- دریافت کنید

- گرفتن

- دادن

- داده

- جهانی

- Go

- می رود

- رفتن

- طلایی

- رفته

- خوب

- افرین

- کردم

- توری

- گروه

- در حال رشد

- بود

- اداره

- دست ها

- خوشحال

- آیا

- داشتن

- سر

- کمک

- سلسله مراتب

- زیاد

- دارای

- صفحه اصلی

- امید

- چگونه

- چگونه

- HTML

- HTTPS

- بزرگ

- صدها نفر

- ترکیبی

- i

- اندیشه

- if

- تصور کنید

- نهفته

- تأثیرگذاری

- مهم

- بهبود

- in

- انگیزه

- مشمول

- نادرست

- افزایش

- به طور فزاینده

- فرد

- صنعت

- اطلاعات

- ابداع

- داخل

- ادغام

- تمامیت

- به هم متصل می شود

- رابط

- به

- شامل

- موضوع

- مسائل

- IT

- ITS

- خود

- کار

- تنها

- دانستن

- شناخته شده

- آزمایشگاه

- بزرگ

- بزرگتر

- بزرگترین

- تاخیر

- بعد

- لایه

- رهبری

- یادگیری

- نامه

- سطح

- مجوز

- پسندیدن

- محدود شده

- ارتباط دادن

- لینک ها

- محلی

- نگاه کنيد

- به دنبال

- خیلی

- مقدار زیادی

- کم

- حفظ

- ساخت

- ساخت

- مدیریت

- مدیر

- تولید

- بسیاری

- بازار

- حداکثر عرض

- شاید

- me

- به معنی

- به معنای

- مکانیکی

- متوسط

- خاطرات

- حافظه

- قدرت

- مدل

- بیش

- اکثر

- حرکت

- نقل مکان کرد

- جنبش

- متحرک

- بسیار

- my

- نیاز

- نیازهای

- هرگز

- جدید

- شب

- گره

- اکنون

- عدد

- of

- خاموش

- قدیمی

- on

- ONE

- فقط

- باز کن

- فرصت ها

- بهینه سازی

- بهینه

- بهینه سازی

- گزینه

- گزینه

- or

- سفارش

- دیگر

- دیگران

- خارج

- به طور کلی

- غلبه بر

- خود

- بسته

- بسته بندی

- صفحات

- موازی

- بخش

- ویژه

- عبور

- مسیر

- راه ها

- PC

- مردم

- انجام دادن

- کارایی

- چشم انداز

- فیزیکی

- از نظر جسمی

- پین

- سیاره

- افلاطون

- هوش داده افلاطون

- PlatoData

- نقطه

- ممکن

- بالقوه

- قدرت

- رئيس جمهور

- قبلا

- شاید

- مشکل

- پردازنده

- پردازنده ها

- محصول

- مدیریت تولید

- تولید

- برنامه

- مناسب

- به درستی

- ارائه

- قرار دادن

- سوال

- کاملا

- بالا بردن

- نرخ

- نسبتا

- مطالعه

- واقعا

- مربوط

- تکیه

- ضروری

- نیاز

- تصمیم

- پاسخ دادن

- نتیجه

- خلاص شدن از شر

- راست

- طلوع

- نقش

- نورد

- دویدن

- در حال اجرا

- همان

- ذخیره

- پس انداز

- گفته

- مقیاس

- دوم

- دیدن

- مشاهده

- به نظر می رسد

- مشاهده گردید

- معنایی

- نیمه هادی

- ارسال

- حسی

- سنسور

- سرورها

- چند

- ورق

- تغییر

- کشتی

- طرف

- طرف

- زیمنس

- سیگنال

- سیگنال

- سیلیکون

- مشابه

- ساده

- شبیه سازی

- شبیه سازی

- پس از

- تنها

- اندازه

- جک پات

- So

- نرم افزار

- راه حل

- مزایا

- برخی از

- مصنوعی

- صحبت می کند

- ویژه

- صرف

- فشار دادن

- پشته

- انباشته

- پشتهسازی

- استاندارد

- دیدگاه

- شروع

- آغاز شده

- راه افتادن

- گام

- استیو

- steven

- هنوز

- ذخیره سازی

- opbevare

- مبارزه

- چنین

- پشتیبانی

- مطمئن

- سیستم

- سیستم های

- جدول

- گرفتن

- صحبت

- تیم ها

- تکنسین

- پیشرفته

- قوانین و مقررات

- آزمون

- تست

- تست

- نسبت به

- که

- La

- آینده

- شان

- آنها

- سپس

- آنجا.

- حرارتی

- اینها

- آنها

- چیز

- اشیاء

- فکر می کنم

- سوم

- این

- کسانی که

- فکر

- از طریق

- زمان

- به

- امروز

- با هم

- ابزار

- ابزار

- بالا

- کاملا

- مبادله

- سنتی

- به طور سنتی

- آموزش

- حمل و نقل

- روند

- درست

- تلاش

- دو

- دو سوم

- نوع

- فهمیدن

- واحد

- دانشگاه

- us

- استفاده کنید

- استفاده

- با استفاده از

- اعتبار سنجی

- ارزش

- تغییرات

- مختلف

- بسیار

- معاون

- معاون رئیس جمهور

- چشم انداز

- مجازی

- از

- راه رفتن

- دیوار

- می خواهم

- بود

- مسیر..

- we

- وزن

- خوب

- بود

- چی

- هر چه

- چه زمانی

- چه

- که

- در حین

- سفید

- تمام

- چرا

- اراده

- با

- بدون

- خواستگاری کردن

- مهاجرت کاری

- از خانه کار کن

- کارگر

- بدترین

- نوشته

- شما

- شما

- زفیرنت