تراشهها شروع به تأثیرگذاری بر طراحی تراشه کردهاند، حتی اگر هنوز به جریان اصلی تبدیل نشدهاند و هیچ بازار تجاری برای این نوع IP سختشده وجود ندارد.

بحثهای مداومی درباره مدیریت چرخه عمر سیلیکون، بهترین راه برای مشخص کردن و اتصال این دستگاهها، و نحوه برخورد با مسائلی مانند پیری ناهموار و عدم تطابق حرارتی وجود دارد. علاوه بر این، تلاش زیادی برای بهبود مشاهده پذیری در حال انجام است تراشه ها با گذشت زمان، چیزی که اهمیت ویژه ای دارد زیرا این دستگاه ها در برنامه های کاربردی حیاتی ایمنی و ماموریت حیاتی استفاده می شوند.

همه این مسائل باید حل شوند تا امکان پذیرش گسترده فراهم شود، و صنعت تراشه دریافته است که کند شدن قانون مور همراه با اندازههای ثابت شبکه مستلزم تغییراتی در نحوه طراحی، تولید و بستهبندی تراشهها است. از نظر فیزیکی غیرممکن است که همه توابع مورد نیاز برای بسیاری از برنامهها را در یک SoC قرار دهیم، و اکنون هدف یک رویکرد منظم، قابل پیشبینی و تکرارپذیر برای تفکیک بسیاری از این مؤلفهها است. در تئوری، این به دستگاهها اجازه میدهد تا راحتتر سفارشی شوند، زمان عرضه به بازار را سرعت بخشند و از مقیاسبندی گران قیمت اجزایی که به آن نیاز ندارند، مانند عملکردهای آنالوگ، اجتناب کنند.

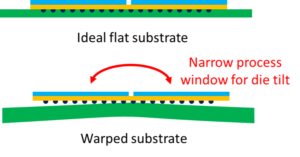

با این حال، دستیابی به این هدف مستلزم حل برخی مسائل پیچیده و خاردار است. برای یک چیز، نیاز به مشاهده، نظارت و تجزیه و تحلیل بسیار بهتری از آنچه در یک بسته وجود دارد، دارد. در حالی که مفهوم قرار دادن چند تراشه در یک بسته به دهه 1990 برمی گردد ماژول های چند تراشه ایبا تراشهها، قالبها معمولاً کوچکتر و نازکتر هستند و دینامیک نحوه توصیف، آزمایش و مشاهده آنها بهطور قابل توجهی تغییر کرده است.

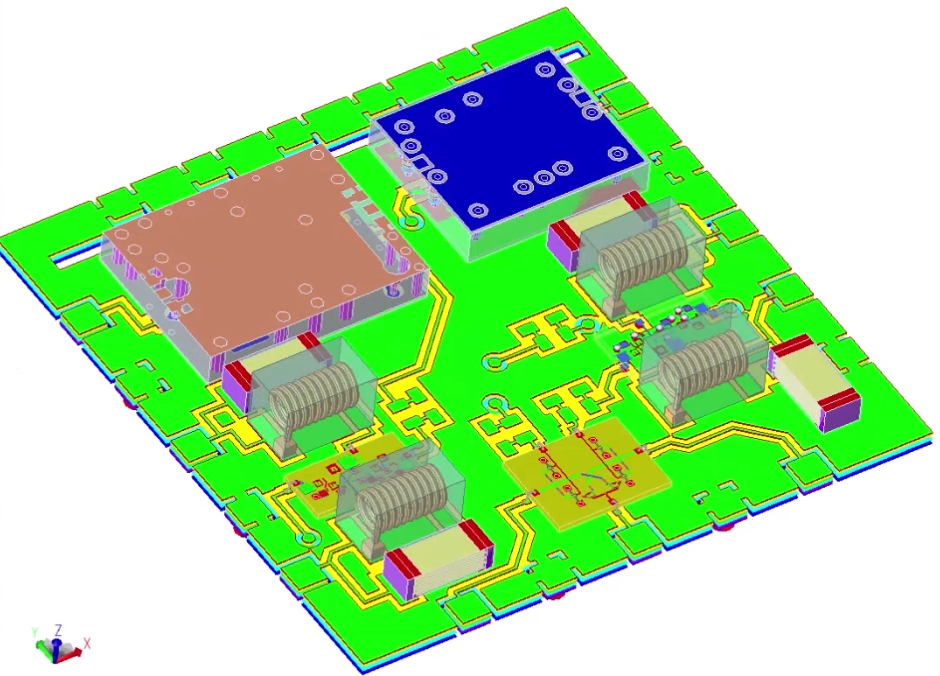

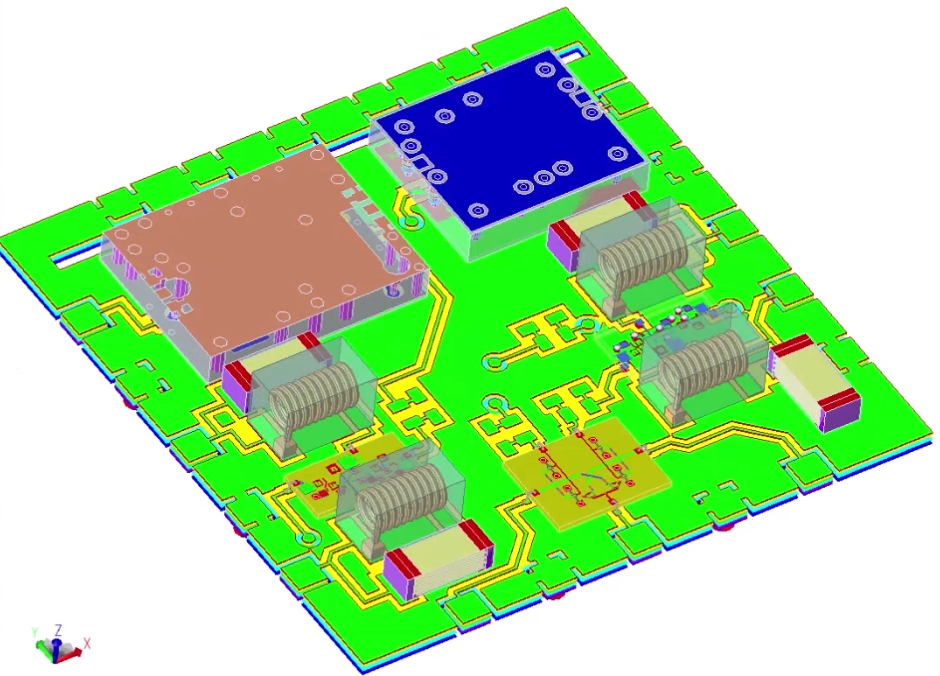

نیلش کامدار، سرپرست پورتفولیوی RF/مایکروویو در شرکت، گفت: «از لحاظ تاریخی ما این ماژولهای چند تراشهای را که امروزه در دنیای بیسیم بسیار محبوب هستند، نامیدهایم. دیدگاه اصلی. شما هر گوشی هوشمندی را برمی دارید، و قطعه بی سیم گوشی هوشمند یک ماژول جلویی است که 20 تا 30 تراشه در فضای کوچکی که کوچکتر از یک ناخن است به هم فشرده شده است. حداقل یک دهه است که در صنعت اتفاق می افتد، اگر نه بیشتر. همچنین، چندین مشکل هوافضا و سایر مشکلات فرکانس بالا به این نوع ادغام نیاز داشته است، بنابراین ما در گذشته این کار را انجام دادهایم.»

شکل 1. طرح ماژول RF چند تراشه ای نشان داده شده در Keysight's PathWave ADS. منبع: Keysight

تغییر بزرگی که اکنون در حال انجام است شامل کاربرد بسیار گستردهتری برای این رویکرد، و همچنین بهبودهایی در طراحی چیپلتها، و روشهای استاندارد برای اتصال، آزمایش و اندازهگیری آنچه در داخل خود چیپلتها اتفاق میافتد، و همچنین بسته پیشرفتهای که آنها را احاطه کرده است، است.

کامدار گفت: «خودرو نمونه عالی از آنچه در حال تغییر است است. در کنفرانس اخیر، یکی از معاونان یک OEM بزرگ در مورد عدم توانایی در گرفتن یک مرکز داده و قرار دادن آن در صندلی عقب خودرو صحبت کرد، زیرا این چیزی است که امروزه برای داشتن یک وسیله نقلیه خودران نیاز است. اگر یکپارچه سازی بیشتری انجام دهید - و اگر به نوعی باعث ناپدید شدن تخته شوید و همه چیز به هم فشرده شود - شاید به صورت عمودی بتوانیم آن را به صندلی عقب ماشین فشار دهیم. موارد استفاده مشابه زیادی وجود دارد. اگر مراکز داده فیزیکی را در نظر بگیرید، نیاز به برق برای چیپلت ها ممکن است کمتر باشد. مزایای زیادی وجود دارد و این چیزی است که امروزه چیپلت ها را به حرکت در می آورد.»

با این حال، این تغییرات به طرز فریبندهای پیچیده هستند و صنعت ممکن است در این مورد به مدرسه بازگردد. او گفت: «ساخت چیپلتها در مقیاس بسیار مدل متفاوتی است که همه ما باید مهارتهای خود را دوباره ارزیابی کنیم. ما باید نحوه راه اندازی سازمان ها و چگونگی ایجاد معماری را مورد ارزیابی مجدد قرار دهیم. ما باید نقش یک طراح سیستم را دوباره ارزیابی کنیم. آنها ممکن است به شکل دیگری به مسائل نگاه کرده باشند، و ممکن است گفته باشند، "من یک طراح سیستم هستم." من مشخصات سیستم ها را طراحی می کنم. من آن را به اجزای سطح کوچکتر، آی سی های جداگانه تقسیم می کنم و مشخصات را توزیع می کنم. من راه میروم و شش ماه بعد برمیگردم و میبینم که همه چطور بودند. شاید این حتی امکان پذیر نباشد. شاید چندین طراح سیستم وجود داشته باشد که باید در زنجیره بالا و پایین وجود داشته باشد. اینها انواع گفتگوهایی است که باید اتفاق بیفتد. در میان بزرگترین بازیگران صنایع، این گفتگوها در حال حاضر اتفاق می افتد، اما نه در همه جا.

تعداد فعل و انفعالات بالقوه در زمینه طراحی چند تراشه قابل توجه است و در بسیاری از موارد برای طراحی خاص است. شخار کاپور، مدیر ارشد مدیریت خط تولید، گفت: «اگر به چند قالب اعتقاد دارید، اگر به چیپلتها اعتقاد دارید، باید باور داشته باشید که این تنها مشکل [طراحی و یکپارچهسازی] را تشدید میکند. گروه سینوپسیس EDA. «چیپلتها از مکانهای مختلف، از منابع بسیاری خواهند آمد. انتخاب های زیادی وجود خواهد داشت، گزینه های زیادی برای همه. بزرگترین مشکل استفاده های فعلی در مورد همه اینها است. شرکت های بزرگ این کار را به صورت سفارشی و سفارشی انجام می دهند. اما اگر استانداردسازی را به طور گسترده دنبال کنید، چگونه میدانید که چیپلتی که وارد میشود با محیط، محصولی که میخواهید بسازید، جا بیفتد؟»

علیرغم تمرکز بر استانداردهایی مانند UCIe و Bunch of Wires، هنوز تفاوتهای ظریفی از نظر نحوه توصیف تراشههای منفرد در زمینه یک سیستم وجود دارد. واقعاً چگونه مشخصات آن را میدانید؟ اینجاست که نظارت بیشتر در تصویر ظاهر می شود، که تقریباً مانند یک امضا است.» کاپور گفت. شما می توانید آن را بخوانید و بدانید که آیا برای محیط شما ایده آل است یا خیر. با توجه به اینکه صنعت در حال حرکت به سمت فعال سازی بیشتر چیپلت ها است، این یک نکته اساسی خواهد بود. الزامات بیشتری ظاهر می شود، استانداردهای بیشتری پدیدار می شود، بنابراین می توانید ببینید که آیا چیزی مناسب است یا خیر.

چالش های دیگری نیز برای غلبه بر آن وجود دارد.

سو هونگ فانگ، مدیر بازاریابی خط تولید UCIe در گفت: با چیپلتها، همه سیگنالهای پرسرعت در بسته قرار دارند، بنابراین قابلیت مشاهده بسیار چالش برانگیزتر است. آهنگ. این را می توان از طریق بررسی خطای پیوند، اسکن چشم، BiST و غیره انجام داد تا به یک قالب خوب شناخته شده (KGD) برسیم. روش های تست همه بر این اساس ساخته شده اند. علاوه بر این، داشتن مانیتورهای خوب برای سلامت لینک ارزشمند خواهد بود و پیشنهادات جدید و متفاوتی از سوی فروشندگان مختلف وجود دارد.

نکته کلیدی، نظارت بر کیفیت سیگنال در زمینه بقیه اجزای یک بسته است، که با تفکیک عملکردهای بیشتر به چیپلتها، دشوارتر میشود.

آیا میتوانیم سیگنالها و کیفیت آنها را در حین انتقال داده نظارت کنیم؟ هانگ فانگ خاطرنشان کرد: تکنیکهای آموزشی قبل از حالت ماموریت برای بهبود استحکام انتقال داده انجام میشوند. "بازآموزی مطلوب نیست زیرا می تواند باعث وقفه در داده ها شود. ما باید بتوانیم به طور مداوم هر خط را نظارت و گزارش کنیم و هر رویدادی را که ممکن است باعث خرابی قبل از وقوع خرابی شود، شناسایی کنیم. پیشگیری از خرابی سیستم و تعمیر آن خرابیها شامل نقشهبرداری مجدد خطوط اضافی یا سایر روشهای تعمیر برای تشخیص خطوط با شکست نهایی است. آموزش و نظارت مستمر این سیگنالهای چیپلت داخلی چالشهایی برای تجزیه و تحلیل رفتار پیوند است.

گروه های کاری برای UCIe به دنبال استانداردسازی برخی از این قابلیت مشاهده هستند تا یک اکوسیستم پیوند باز داشته باشند. اما افزودن قابلیت مشاهده و نظارت نیز می تواند بر اساس بخش عمودی بسیار متفاوت باشد.

رندی فیش، مدیر مدیریت خط تولید گروه Synopsys EDA، توضیح داد که چون رویکرد استانداردی وجود ندارد و عرضهکنندگان تجاری کمی برای راهحلهای قابل مشاهده وجود ندارد، تقریباً همه راهحلها سفارشی شدهاند. او گفت: «اگر وارد هر یک از نیمههای پیشرو شوید، آنها کاری انجام میدهند. سوال این است که آیا عملکردهایی در اطراف چند قالب وجود دارد که ما را مجبور به استانداردسازی برای داشتن یک زیرساخت منسجم یا منسجم برای نظارت و اشکالزدایی میکند - اساساً برای اینکه ببینیم چه اتفاقی میافتد به خصوص اگر چندین قالب را از چندین تامینکننده دریافت میکنید. برخی از راهحلهای چند قالبی وارد خودروسازی میشوند و در آنجا به چیزهایی مانند پیری و اتفاقی که برای این قالبها میافتد اهمیت میدهند. و همانطور که می دانیم، این گره های پیشرفته است. اینطور نیست که شما 6 تا از فناوری های بالغ 10 ساله داشته باشید. اینها گره های پیشرفته ای هستند که سابقه طولانی ندارند. به همین دلیل، عوامل متعددی وجود دارد که این اتفاق را وادار می کند.»

چیپلت ها تضادهای جالبی را نیز معرفی می کنند. کامدار از Keysight خاطرنشان کرد که در طی یک پنل مدیر عامل اخیر، یکی از اعضای پنل گفت که چیپلتها دوگانگی منحصربهفردی دارند. از یک طرف، هر چیپلت میتواند یک IP مستقل باشد که میتوانید آن را از یک فروشنده IP تهیه کرده و با هزینه نسبتاً کم و نسبتاً آسان آن را در سیستم خود ادغام کنید. با این حال، کل مجموعهای که میخواهید بسازید، ناگهان شما را مجبور میکند همه چیز را بدانید. قبلاً میتوانستید بگویید: «من به شش چیز نیاز دارم. من از یک فروشنده IP میخواهم پنج عدد را از قفسه بخرم و آنها متوجه خواهند شد که به چه چیزی نیاز دارد. من روی یکی تمرکز خواهم کرد.' اما اکنون ممکن است در انجام این کار موفق نباشید. ممکن است واقعاً لازم باشد که بدانید چگونه هر شش مورد را انجام دهید، و بفهمید که چگونه همه اینها اتفاق می افتد زیرا پیچیدگی مشکل به تازگی بالا رفته است. این ممکن است صنعت را مجبور کند که در ابتدا فقط به بازیگران بزرگ اجازه دهد تا این موضوع را کشف کنند. ممکن است زمان زیادی طول بکشد تا فروشندگان کوچکتر بتوانند در این محیط موفق شوند.

با این وجود، شتاب بخشیدن به ادغام و پذیرش چیپلت به بیش از یک شرکت نیاز دارد.

کامدار گفت: «کیسایت در سمپوزیوم TSMC که یک رویداد عمومیتر است، شرکت کرد و در ادامه کارگاهی فقط با شرکای 3D Fabric Alliance برگزار شد. TSMC کل روز را با صحبت در مورد اینکه چگونه همه ما باید روی این موضوع با هم کار کنیم، شروع کرد و به پایان رساند، که توسط سایر شرکتکنندگان از جمله AMD و Qualcomm تکرار شد. سخنرانان هر دو شرکت گفتند که حتی یک شرکت EDA نمی داند چگونه مشکل چیپلت را به تنهایی حل کند. کل صنعت باید با هم کار کنند.»

چالش های فنی

یکی دیگر از نگرانی های کلیدی چیپلت ها اتلاف گرما است. این بخشی از خصوصیات است، اما به شدت به موارد استفاده، انتخاب های بسته بندی و معماری کلی سیستم در بسته نیز بستگی دارد.

Rishi Chugh، معاون بازاریابی محصول، گروه IP در Cadence، میگوید: «برای تراشههای حاشیهای در طراحی، با توجه به PPA بهینه (هدفگیری pj/bit تهاجمی و چگالی ساحلی)، که در طراحی PHY چیپلتها بسیار مهم است، بسیار کم است. «قابلیت اطمینان برای غربالگری KGD و همچنین رسیدن به موفقیت عملیاتی تجاری، کلیدی است و همچنین قابلیت مشاهده نیز مهم است. طرحهای یکپارچگی دادهها مانند CRC (بررسی افزونگی چرخهای)، اسکن چشم، BiST و مدارهای نظارتی برای استحکام در طراحی پیادهسازی میشوند، و طراحی باید بیش از حد با مکانیسمهای خرابی برای اطمینان از انعطافپذیری خط داده تدارک دیده شود.

Chugh افزود، یک فصل کامل در پروتکل UCIe به مقداردهی اولیه و آموزش مرتبط با پروتکل UCIe اختصاص دارد که جنبه مشاهده پذیری پروتکل را پوشش می دهد.

علاوه بر این، بحث در مورد اینکه آیا اصول واقعی افزودن قابلیت مشاهده به یک سیستم سخت ترین بخش است یا اینکه تغییر در تفکر پیرامون این مفاهیم دشوارتر است، وجود دارد.

"در واقع در مقایسه با چیزهای دیگر چندان پیچیده نیست زیرا "فقط" یک بلوک دیگر است که باید به آن متصل شود. فرانک شرمایستر، معاون راهحلها و توسعه کسبوکار در شرکت، گفت: مشاهده وجود دارد و ما تواناییهایی برای ردیابی چیزها داریم. آرتریس IP. "کاربران در حال حاضر چیزهایی مانند نگاه کردن به رجیسترها از منظر نرم افزاری را درخواست می کنند. بنابراین اکنون چالش در دسترس قرار دادن این ثبتها در NoC است. از منظر NoC، پروتکلهایی مانند CHI، ACE، AMBA، OCP یا موارد دیگر وجود دارند، و اینها مکانیسمهای زبان هستند - نحوه صحبت و تعامل آنها. در NoC، با پروتکلهای پیچیدهتر، چیزهایی در چرخههای متعدد اتفاق میافتند، بنابراین باید منتظر پاسخها باشید، چیزهایی را در خط لوله قرار دهید.»

این شبیه به اجرای حدس و گمان در پردازنده ها است. Schirrmeister توضیح داد: "ما در مورد این اعتبارات صحبت می کنیم، مانند مدت زمانی که باید منتظر پاسخ باشم و غیره." «اینها همه بخشهایی از پروتکلها هستند. در NoC، باید مسائلی مانند عمق بافرها را بدانید؟ واقعاً چه زمانی منتظر داده هستم؟ تا حدی عملکرد است. سپس، برای مشاهده پذیری، می توانید به داده ها متصل شوید و حسگرها ممکن است از شبکه خود بسته به نحوه پیکربندی آن استفاده کنند. در مورد مانیتورهای روی تراشه، شما باید تصمیم بگیرید که مثلاً آن را روی یک گذرگاه ویژه مشاهده قرار دهید یا خیر. همیشه این بحث وجود دارد که واقعاً چقدر اشکال زدایی دارم؟ در پایان، این «فقط» یکی دیگر از اتصالات متقابل آن اجزاست و شما باید تصمیم بگیرید که چگونه آن را از تراشه خارج کنید و غیره. این که چقدر روی تراشه ذخیره میکنید، این سوال است که من حاضرم برای آن چقدر ملک سیلیکونی خرج کنم؟»

این امر به ویژه هنگام دوخت چیپپلتها اهمیت پیدا میکند. چگونه می توانم مطمئن شوم که فضای کافی برای این موجودیت محاسباتی که فقط شبیه داده است، در اختیار دارم که در واقع هیچ ارزشی به تابع فوری اضافه نمی کند؟ Gajinder Panesar، معمار ارشد Picocom می پرسد. همچنین، ممکن است من یک متخصص نظارت نباشم، اما می دانم که به آن نیاز دارم. بنابراین من به چیزی نیاز دارم که بگوید "فقط آن دکمه را فشار دهید." شما یک محیط دارید، ما در حال طراحی هستیم و "این" اتفاق می افتد. در حالت ایدهآل، ما باید رفتار عملکرد CPU را مشاهده کرده و سپس به صورت پویا جنبههای خاصی از هسته را تنظیم کنیم تا عملکرد بهتری داشته باشیم.

یکی از قطعاتی که هنوز توسعه نیافته است، کنترل پویا دستگاه ها و تنظیماتی است که می توان در طول عمر آن انجام داد.

لی هریسون، مدیر بازاریابی محصول در گروه Tessent در این باره می گوید: «بگویید که ما تمام توانایی ها را داریم که همه چیز را از قبل الگوبرداری کنیم. نرم افزار صنایع دیجیتال زیمنس. ما همه مانیتورها را برای انجام کارهای درون سیستمی تعبیه کرده ایم، اما این حلقه را می بندد. برای هندسههای جدیدتر، هنوز چیزهای زیادی برای بهینهسازی نحوه تنظیم پارامترهای مختلف دستگاه برای افزایش این قابلیت اطمینان وجود دارد. قطعه ای که این حلقه را به سیستم زندگی می بندد جایی است که ارزش زیادی وجود دارد. با این حال هنوز کار برای انجام دادن وجود دارد.

تغییر نقش های مسئولیت

چیپپلتهای تجاری یک مسئله مهم دیگر را اضافه میکنند، و آن اینکه چه کسی در هنگام مشاهده اتفاق غیرمنتظره یا اشتباه، مسئول است.

"اگر من یک تراشه ساز هستم، تراشه را می سازم و ممکن است از طریق یک تراشه بگذرم OSAT برای آزمایش، گفت: پل کارازوبا، معاون بازاریابی در Expedera. من ممکن است از ASE به عنوان یک خانه بسته بندی استفاده کنم، اما آن را با نام و ضمانت خود می فروشم. وقتی چیپلت داشته باشیم جالب می شود. در تمام جلسات ما در مورد چیپلت ها، همیشه این سوال مطرح می شود که چه کسی مسئول چه چیزی است. فرض کنید من قرار بود یک چیپلت هوش مصنوعی بسازم و با شش چیپلت شرکت دیگر به صورت یک سیستم و بسته بفروشم. کدام شرکت قرار است گارانتی کند؟ کدام شرکت خدمات را روی آن انجام خواهد داد؟ در حال حاضر اجماع واقعی وجود ندارد.»

کارازوبا گفت که ایده کاری این است که شرکتی که نام آن در قسمت بیرونی بسته قرار دارد، مسئول آن خواهد بود. این شرکت احتمالاً مسئولیت نهایی ارائه خدمات به مشتریان خود را بر عهده خواهد داشت، اما لایه دیگری از خدمات را که سازندگان چیپلت باید ارائه دهند، ارائه می دهد و این جالب خواهد بود. ترس این است که حدوداً در سال 2000، مثلث اینتل-مایکروسافت-دل همه با انگشت به سمت یکدیگر اشاره می کنند. این یک ترس ناگفته در صنعت در حال حاضر است."

و شاید یکی از چیپلت ها نباشد. اگر یک بستر یا یک اتصال فیزیکی معیوب باشد چه اتفاقی میافتد؟

کارازوبا گفت: «از نقطه نظر آزمایش، یک چیپلت ممکن است به خوبی تست شود. اما هنگامی که یک مشکل اتصال فیزیکی وجود دارد، سازنده چیپلت چگونه آن را در مقابل سازنده ماژول چند تراشه درک می کند؟ جالب میشه تنها راه حل این مسائل آزمون و خطا است. ما میتوانیم بهعنوان سازندگان نیمهرسانا، هر چقدر که بخواهیم قراردادهای قانونی طراحی کنیم، اما در اینجا در آبهای ناشناختهای هستیم و باید همه چیز را تعدیل کرد. مدلهای پشتیبانی باید به گونهای تنظیم شوند که واقعیت جدید سیلیکون یکپارچه را که وسیله اصلی فروش نیمههادی نیست، منعکس کنند.

کاپور Synopsys قبلاً بازتاب هایی را در اکوسیستم دیده است. «همیشه اکوسیستمهایی وجود داشتهاند، اما اکوسیستم فعال شما از هر کجا که هستید، شاید حلقه بعدی اطراف آن باشد. اگر در حال طراحی هستید، فقط نگران قوانین طراحی ریخته گری و کتابچه راهنمای قوانین طراحی هستید. وقتی در مورد چیپلت ها صحبت می کنید این در حال تغییر است. حتی با طراحی، اکنون بیشتر از قبل به آزمایش فکر می کنید. شما در حال صحبت با Advantest و ترادین. حتی اگر شما فقط یک طراح هستید، باید بفهمید که چه چیزی را باید از نقطه نظر ATPG وارد کنید و چگونه آزمایش می شود. اندازه اکوسیستم مربوطه در حال افزایش است.»

با این حال، صنعت چاره ای جز حل این مسائل ندارد. ما در مورد بازار چیپلت ها صحبت کرده ایم. شما می توانید یک قالب را بیرون بکشید و آن را آماده کنید. ما هنوز با آن فاصله داریم، اما گامها در مورد آنچه که باید به آن دست یابیم واضحتر میشوند. اتصال اساسی است. استانداردهای UCIe یک الزام هستند، و با آن پروتکل ها و قوانین از نقطه نظر اتصال که شما باید ایجاد کنید، همراه است. بعدی مدل های بسیار واضح تعریف شده است. چالش هایی که ما در مورد آنها صحبت می کنیم تحت تأثیر حرارت، به ویژه، و قدرت هستند. برخی از استانداردها در حال حاضر در مورد آن وجود دارد، و ما از اتصال به مدل مشخص شده خواهیم رفت، بنابراین می توانیم با اطمینان بیشتری از آن استفاده کنیم. سپس به نوعی امضا نیاز خواهیم داشت، جایی که میتوانیم از نقطه نظر آزمایشپذیری، طول عمر و اینکه چگونه همه میمیرند بهطور متفاوتی تغییر میکنند، ببینیم.»

ورودی های همه اینها از مانیتورهای تراشه و سیستم خواهد بود، که همچنین باید بر اساس استانداردها باشد.

- محتوای مبتنی بر SEO و توزیع روابط عمومی. امروز تقویت شوید.

- PlatoAiStream. Web3 Data Intelligence دانش تقویت شده دسترسی به اینجا.

- ضرب کردن آینده با آدرین اشلی. دسترسی به اینجا.

- خرید و فروش سهام در شرکت های PRE-IPO با PREIPO®. دسترسی به اینجا.

- منبع: https://semiengineering.com/chiplet-planning-kicks-into-high-gear/

- : دارد

- :است

- :نه

- :جایی که

- $UP

- 1

- 20

- 30

- 3d

- a

- توانایی

- قادر

- درباره ما

- شتاب دادن

- رسیدن

- فعال

- واقعی

- واقعا

- اضافه کردن

- اضافه

- اضافه کردن

- اضافه

- تنظیم شده

- تنظیمات

- اتخاذ

- آگهی

- پیشرفته

- هوافضا

- مهاجم

- سالخورده

- AI

- معرفی

- اتحاد

- اجازه دادن

- قبلا

- همچنین

- همیشه

- am

- AMD

- مقدار

- an

- تحلیل

- تجزیه و تحلیل

- و

- دیگر

- هر

- کاربرد

- برنامه های کاربردی

- روش

- معماری

- هستند

- دور و بر

- AS

- ظاهر

- جنبه

- مرتبط است

- At

- خودرو

- خود مختار

- وسیله نقلیه خودمختار

- در دسترس

- اجتناب از

- دور

- به عقب

- مستقر

- اساسا

- BE

- زیرا

- شود

- تبدیل شدن به

- بوده

- قبل از

- شروع

- بودن

- باور

- مزایای

- بهترین

- بهتر

- بزرگ

- بزرگترین

- بیت

- مسدود کردن

- تخته

- هر دو

- شکستن

- به ارمغان می آورد

- پهن

- گسترده تر

- ساختن

- ساخته

- دسته

- اتوبوس

- کسب و کار

- توسعه تجاری

- اما

- دکمه

- خرید

- by

- آهنگ

- نام

- CAN

- قابلیت های

- ماشین

- اهميت دادن

- مورد

- موارد

- علت

- مرکز

- مراکز

- مدیر عامل شرکت

- معین

- زنجیر

- به چالش

- چالش ها

- به چالش کشیدن

- تغییر دادن

- تغییر

- تبادل

- متغیر

- فصل

- مشخص کردن

- مشخص شده است

- بررسی

- چک

- رئیس

- تراشه

- چیپس

- انتخاب

- انتخاب

- دایره

- واضح تر

- به وضوح

- بستن

- بسته

- منسجم

- منسجم

- ترکیب شده

- بیا

- می آید

- آینده

- تجاری

- شرکت

- شرکت

- پیچیده

- پیچیدگی

- بغرنج

- اجزاء

- مفهوم

- مفاهیم

- نگرانی

- علاقمند

- کنفرانس

- اتصال

- متصل

- اتصال

- اجماع

- در نظر بگیرید

- توجه

- زمینه

- مداوم

- به طور مداوم

- قرارداد

- کنتراست

- تضادها

- کنترل

- گفتگو

- هسته

- هزینه

- میتوانست

- را پوشش می دهد

- پردازنده

- CRC

- اعتبار

- بسیار سخت

- جاری

- مشتریان

- سفارشی

- چرخه

- داده ها

- مرکز داده

- مرکز دادهها

- تاریخ

- روز

- مقدار

- مناظره

- دهه

- تصمیم گیری

- اختصاصی

- عمیق

- مشخص

- چگالی

- وابسته

- بستگی دارد

- طرح

- طراحی

- طراح

- طراحان

- طراحی

- مطلوب

- توسعه

- پروژه

- دستگاه

- دستگاه ها

- DID

- مردن

- مختلف

- مشکل

- دیجیتال

- مدیر

- ناپدید می شوند

- گفتگو

- بحث و گفتگو

- توزیع کردن

- do

- میکند

- عمل

- انجام شده

- آیا

- پایین

- رانندگی

- در طی

- پویا

- بطور پویا

- دینامیک

- هر

- به آسانی

- اکوسیستم

- اکوسیستم

- تلاش

- ظهور

- قادر ساختن

- توانمندسازی

- پایان

- کافی

- اطمینان حاصل شود

- تمام

- موجودیت

- محیط

- خطا

- به خصوص

- ایجاد

- املاک

- و غیره

- حتی

- واقعه

- حوادث

- تا کنون

- هر کس

- همه چیز

- مثال

- اعدام

- وجود داشته باشد

- وجود دارد

- گران

- کارشناس

- توضیح داده شده

- صادرات

- گسترش

- چشم

- پارچه

- عوامل

- عدم

- شکست

- بسیار

- روش

- ترس

- کمی از

- انجیر

- شکل

- ماهی

- مناسب

- ثابت

- تمرکز

- برای

- استحکام

- نیروهای

- چهارم

- ریخته گری

- از جانب

- جلو

- تابع

- توابع

- اساسی

- اصول

- چرخ دنده

- دریافت کنید

- گرفتن

- داده

- Go

- هدف

- می رود

- رفتن

- خوب

- بزرگ

- تا حد زیادی

- گروه

- گروه ها

- دست

- رخ دادن

- اتفاق می افتد

- اتفاق می افتد

- آیا

- داشتن

- he

- سلامتی

- اینجا کلیک نمایید

- زیاد

- فرکانس بالا

- خیلی

- تاریخ

- خانه

- چگونه

- چگونه

- اما

- HTTPS

- بزرگ

- i

- ICS

- اندیشه

- دلخواه

- if

- فوری

- تأثیر

- نهفته

- اجرا

- مهم

- غیر ممکن

- بهبود

- ارتقاء

- in

- شامل

- از جمله

- افزایش

- مستقل

- فرد

- لوازم

- صنعت

- شالوده

- در ابتدا

- ورودی

- ادغام

- ادغام

- تمامیت

- تعامل

- فعل و انفعالات

- جالب

- داخلی

- به

- معرفی

- IP

- موضوع

- مسائل

- IT

- ITS

- تنها

- کاپور

- کلید

- ضربات

- نوع

- دانستن

- شناخته شده

- لین

- زبان

- بزرگ

- بعد

- قانون

- لایه

- طرح

- رهبری

- برجسته

- یادگیری

- کمترین

- انسوی کشتی که از باد در پناه است

- قانونی

- سطح

- wifecycwe

- طول عمر

- عمر

- پسندیدن

- لاین

- ارتباط دادن

- طولانی

- دیگر

- به دنبال

- خیلی

- کم

- ساخته

- مسیر اصلی

- عمده

- ساخت

- سازنده

- سازندگان

- ساخت

- مدیریت

- مدیر

- کتابچه راهنمای

- ساخته

- بسیاری

- بازار

- بازار یابی (Marketing)

- بازار

- بالغ

- حداکثر عرض

- ممکن است..

- اندازه

- مکانیسم

- جلسات

- روش

- قدرت

- ماموریت

- حالت

- مدل

- مدل

- واحد

- ماژول ها

- مانیتور

- نظارت بر

- مانیتور

- یک پارچه

- ماه

- بیش

- متحرک

- بسیار

- چندگانه

- باید

- my

- نام

- نیاز

- نیازهای

- شبکه

- جدید

- بعد

- نه

- گره

- اشاره کرد

- اکنون

- عدد

- مشاهده کردن

- of

- خاموش

- on

- ONE

- مداوم

- فقط

- باز کن

- قابل استفاده

- بهینه

- بهینه سازی

- گزینه

- or

- سفارش

- سازمان های

- دیگر

- سایر شرکت کنندگان

- دیگران

- ما

- خارج

- خارج از

- روی

- به طور کلی

- غلبه بر

- خود

- بسته

- بسته بندی

- بسته بندی

- تابلو

- پارامترهای

- بخش

- شرکت کنندگان

- ویژه

- ویژه

- شرکای

- بخش

- گذشته

- پل

- کارایی

- چشم انداز

- فیزیکی

- از نظر جسمی

- انتخاب کنید

- تصویر

- قطعه

- قطعات

- خط لوله

- اماکن

- برنامه ریزی

- افلاطون

- هوش داده افلاطون

- PlatoData

- بازیکنان

- نقطه

- نقطه مشاهده

- محبوب

- مقام

- ممکن

- پتانسیل

- قدرت

- قابل پیش بینی

- رئيس جمهور

- فشار

- پیشگیری

- قبلا

- اصلی

- قبلا

- شاید

- مشکل

- مشکلات

- پردازنده ها

- محصول

- مشخصات

- پیشنهادات

- پروتکل

- پروتکل

- ارائه

- عمومی

- قرار دادن

- قرار دادن

- کوالکام

- کیفیت

- سوال

- مطرح شده

- خواندن

- اماده

- واقعی

- املاک و مستغلات

- واقعیت

- واقعا

- دلیل

- اخیر

- به رسمیت شناخته شده

- بازتاب

- بازتاب

- ثبت

- نسبتا

- مربوط

- قابلیت اطمینان

- تعمیر

- قابل تکرار

- گزارش

- نیاز

- ضروری

- مورد نیاز

- انعطاف پذیر

- پاسخ

- پاسخ

- مسئوليت

- مسئوليت

- REST

- راست

- نیرومندی

- نقش

- قانون

- قوانین

- سعید

- فروش

- گفتن

- گفته

- می گوید:

- مقیاس

- مقیاس گذاری

- اسکن

- طرح ها

- مدرسه

- پرده

- دیدن

- مشاهده گردید

- بخش

- فروش

- فروش

- نیمه هادی

- ارشد

- سنسور

- سرویس

- تنظیم

- چند

- تاقچه

- تغییر

- باید

- نشان داده شده

- طرف

- سیگنال

- سیگنال

- قابل توجه

- به طور قابل توجهی

- سیلیکون

- مشابه

- تنها

- شش

- شش ماه

- اندازه

- اندازه

- مهارت ها

- کند شدن

- کوچک

- کوچکتر

- گوشی های هوشمند

- So

- نرم افزار

- مزایا

- حل

- حل کردن

- برخی از

- چیزی

- منبع

- منابع

- فضا

- سخنرانان

- ویژه

- مشخصات

- نظری

- سرعت

- خرج کردن

- فشار دادن

- پشته

- استاندارد

- استانداردهای

- آغاز شده

- مراحل

- هنوز

- opbevare

- موفقیت

- موفق

- چنین

- تعقیب قانونی کردن

- تامین کنندگان

- پشتیبانی

- بزم پس از شام

- سیستم

- سیستم های

- گرفتن

- طول می کشد

- صحبت

- سخنگو

- هدف گذاری

- تکنیک

- فن آوری

- قوانین و مقررات

- آزمون

- تست

- نسبت به

- که

- La

- شان

- آنها

- خودشان

- سپس

- نظریه

- آنجا.

- حرارتی

- اینها

- آنها

- چیز

- اشیاء

- تفکر

- این

- کسانی که

- اگر چه؟

- از طریق

- زمان

- به

- امروز

- با هم

- نسبت به

- رد

- آموزش

- انتقال

- محاکمه

- ازمایش و خطا

- tsmc

- به طور معمول

- فهمیدن

- در حال انجام

- غیر منتظره

- منحصر به فرد

- us

- استفاده کنید

- استفاده

- ارزشمند

- ارزش

- مختلف

- وسیله نقلیه

- فروشنده

- فروشندگان

- در مقابل

- عمودی

- عمودی

- بسیار

- معاون رئیس جمهور

- چشم انداز

- صبر کنيد

- منتظر

- می خواهم

- بود

- آب

- مسیر..

- راه

- we

- خوب

- رفت

- چی

- چه شده است

- چه زمانی

- چه

- که

- در حین

- WHO

- تمام

- که

- بطور گسترده

- اراده

- مایل

- بي سيم

- با

- در داخل

- مهاجرت کاری

- همکاری

- کارگر

- کارگاه

- جهان

- خواهد بود

- اشتباه

- هنوز

- شما

- شما

- زفیرنت