چالشهای تست SoC به دلیل پیچیدگی و تنوع بلوکهای عملکردی ادغام شده در تراشه به وجود میآیند. همانطور که SoC ها پیچیده تر می شوند، دسترسی به تمام بلوک های عملکردی درون تراشه برای آزمایش دشوارتر می شود. SoC ها همچنین می توانند حاوی میلیاردها ترانزیستور باشند که آزمایش تراشه ها را بسیار وقت گیر می کند. از آنجایی که زمان آزمایش مستقیماً بر هزینه آزمایش تأثیر می گذارد، به حداقل رساندن زمان آزمایش برای مدیریت هزینه محصول نهایی بسیار مهم است. ژنراتور خودکار الگوی تست (ATPG) بخش مهمی از تست SoC است، زیرا الگوهای آزمایشی را برای تشخیص عیوب در طراحی تولید می کند. با این حال، اتوماسیون ATPG یک کار چالش برانگیز است، به خصوص برای SoC های پیچیده، به دلیل تعداد زیادی بلوک های کاربردی و نقاط تست که باید پوشش داده شوند. توسعه الگوریتمهای کارآمد و مؤثر ATPG یک چالش کلیدی برای آزمایش SoC است. اما بسیاری از ابزارهای ATPG امروزه کاملاً خودکار نیستند. کاربران باید تمام دستورات و گزینه های ارائه شده توسط ابزارها را یاد بگیرند تا بتوانند به طور موثر از آنها استفاده کنند.

آیا راه حلی وجود دارد که مقداری اتوماسیون را به فرآیند ATPG بیاورد و در نتیجه بهره وری مهندسی را افزایش دهد؟ اگر این راه حل در زمان تست نیز صرفه جویی قابل توجهی داشته باشد چه؟ راه حل Tessent Streaming Scan Network (SSN) زیمنس EDA نوید ارائه این مزایا را می دهد. این موضوع توسط اینتل، یکی از مشتریان زیمنس EDA در کنفرانس اخیر User2User اثبات شد. Toai Vo اینتل بر اساس تجربه تیمش با اولین طراحی خود با استفاده از راهکار Tessent SSN، نکات اثباتی را ارائه کرد. تیم او شامل کوین لی، جو چو و چینکو (تام) وو بود.

راه حل Tessent SSN

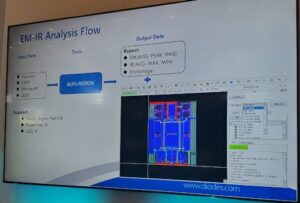

در یک رویکرد تست اسکن استاندارد، دادههای تست یک بیت در مدار بارگذاری میشوند و از طریق زنجیرههای اسکن برای مشاهده پاسخهای خروجی جابهجا میشوند. این فرآیند برای هر الگوی آزمایشی تکرار میشود، که میتواند زمانبر باشد و به زمانهای طولانی تست منجر شود. اما راهحل Tessent SSN دادههای تست را بستهبندی میکند تا تلاشهای اجرای DFT را بهطور چشمگیری کاهش دهد و زمانهای آزمایش تولید را کاهش دهد. با جدا کردن الزامات DFT در سطح هسته و سطح تراشه، هر هسته را می توان با بهینه ترین پیکربندی فشرده سازی برای آن هسته طراحی کرد. این راه حل می تواند برای آزمایش موثر تراشه های بزرگ و پیچیده ای که تعداد گره های داخلی بالایی دارند و نیاز به آزمایش دارند، استفاده شود. از یک شبکه اختصاصی برای انتقال داده های آزمایشی به صورت جریانی استفاده می کند که پردازش موازی داده ها را ممکن می کند و در نتیجه زمان آزمایش را کاهش می دهد.

مقیاس پذیری

شبکه اسکن جریانی از معماری های اسکن مقیاس پذیر پشتیبانی می کند که می توانند SoC ها را با تعداد زیادی بلوک عملکردی مدیریت کنند. این ابزار رویکرد مقیاسپذیری را برای آزمایش هر تعداد هسته به طور همزمان ارائه میکند و زمان تست و حجم دادههای اسکن را به حداقل میرساند. زیرساخت تست SSN Tessent بر اساس استاندارد IEEE 1687/IJTAG برای ارائه انعطافپذیری و مقیاسپذیری بیشتر برای مدیریت طرحها و سناریوهای آزمایشی پیچیدهتر ساخته شده است.

اتوماسیون

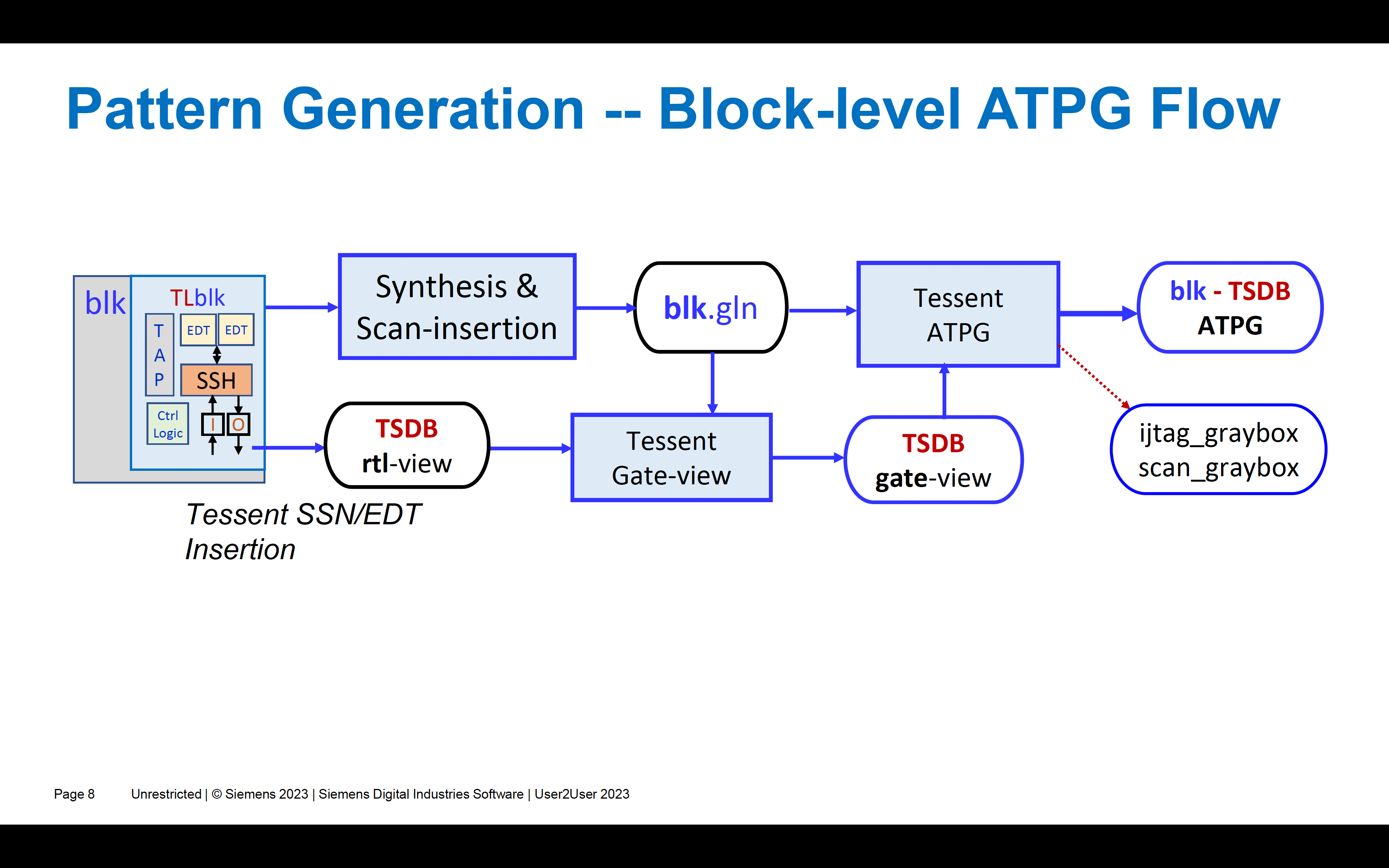

ماهیت شی گرا سلسله مراتبی زیرساخت آزمایشی خود را برای اتوماسیون آسان تر می کند. با استفاده از زیرساخت Tessent، کاربر می تواند به راحتی منطق تست را در یک تراشه وارد کند. این فرآیند با طراحی RTL آغاز می شود، جایی که منطق تست SSN با استفاده از اتوماسیون درج می شود.

صرفه جویی در زمان تست

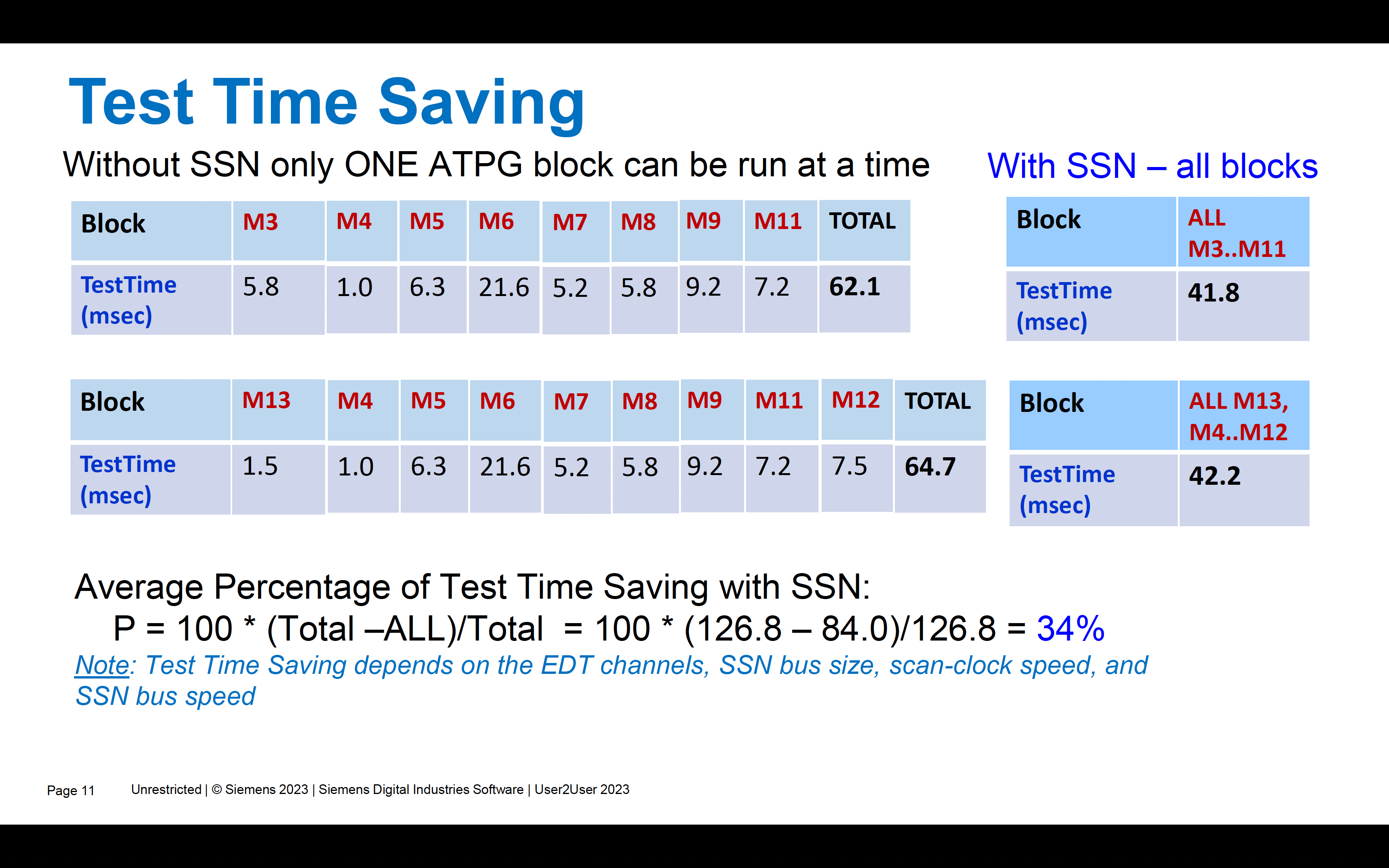

با استفاده از روش سنتی ATPG، معمولاً فقط بلوک را می توان در زمانی اجرا کرد که کل زمان آزمایش را افزایش می دهد. با رویکرد Tessent SSN ATPG، چندین بلوک را می توان به صورت موازی اجرا کرد و در نتیجه کل زمان تست را به میزان زیادی کاهش داد. جدول زیر صرفه جویی در زمان آزمایش را نشان می دهد که توسط تیم Toai در طراحی آنها به دست آمده است.

خلاصه

تیم Toai انتقال از یک کانال آزمایشی قطعی تعبیه شده سنتی (EDT) مبتنی بر ATPG به یک ATPG مبتنی بر بسته با SSN را بسیار آسان یافت. راه حل Tessent SSN تا حد زیادی تلاش مهندسی و سیلیکون را کاهش داد. و کاهش زمان تست در مقایسه با یک راه حل سنتی برای آزمایش قابل توجه بود. به قول Toai Vo، این کاملا یک راه حل آزمایشی ابتکاری است و واقعا کار می کند.

برای جزئیات بیشتر ، از صفحه محصول Tessent SSN دیدن کنید.

همچنین خواندن:

دستیابی به PPA بهینه در محل قرارگیری و انتقال آن از طریق Signoff

کاهش اثرات انتشار خطای DFE بر روی پیوندهای SerDes با سرعت بالا

ریشه سخت افزاری اعتماد برای ایمنی خودرو

اشتراک گذاری این پست از طریق:

- محتوای مبتنی بر SEO و توزیع روابط عمومی. امروز تقویت شوید.

- PlatoAiStream. Web3 Data Intelligence دانش تقویت شده دسترسی به اینجا.

- ضرب کردن آینده با آدرین اشلی. دسترسی به اینجا.

- خرید و فروش سهام در شرکت های PRE-IPO با PREIPO®. دسترسی به اینجا.

- منبع: https://semiwiki.com/eda/328395-tessent-ssn-enables-significant-test-time-savings-for-soc-atpg/

- :است

- :نه

- :جایی که

- $UP

- a

- کاملا

- دسترسی

- دست

- الگوریتم

- معرفی

- همچنین

- an

- و

- هر

- روش

- هستند

- دور و بر

- AS

- At

- خودکار

- اتوماتیک

- اتوماسیون

- خودرو

- مستقر

- BE

- شدن

- شود

- مزایای

- میلیاردها

- بیت

- مسدود کردن

- بلاک ها

- به ارمغان بیاورد

- به ارمغان می آورد

- ساخته

- اما

- by

- CAN

- حمل

- زنجیر

- به چالش

- چالش ها

- به چالش کشیدن

- کانال

- تراشه

- چیپس

- مقایسه

- پیچیده

- پیچیدگی

- کنفرانس

- پیکر بندی

- هسته

- هزینه

- پوشش داده شده

- بحرانی

- بسیار سخت

- مشتریان

- داده ها

- اختصاصی

- ارائه

- تحویل

- ارائه

- طرح

- طراحی

- طرح

- جزئیات

- در حال توسعه

- مشکل

- مستقیما

- تنوع

- به طور چشمگیری

- دو

- در طی

- هر

- آسان تر

- به آسانی

- ساده

- موثر

- به طور موثر

- اثرات

- موثر

- موثر

- تلاش

- جاسازی شده

- را قادر می سازد

- را قادر می سازد

- مهندسی

- افزایش

- خطا

- به خصوص

- تجربه

- خیلی

- گسل

- نام خانوادگی

- انعطاف پذیری

- جریان

- پیروی

- برای

- یافت

- از جانب

- کاملا

- تابعی

- تولید می کند

- نسل

- ژنراتور

- بیشتر

- تا حد زیادی

- دسته

- آیا

- زیاد

- خود را

- اما

- HTTPS

- IEEE

- if

- اثرات

- پیاده سازی

- in

- مشمول

- به طور فزاینده

- شالوده

- ابتکاری

- یکپارچه

- اینتل

- داخلی

- به

- IT

- خود

- کلید

- بزرگ

- رهبری

- یاد گرفتن

- سطح

- منطق

- طولانی

- ساخت

- مدیریت

- روش

- تولید

- بسیاری

- حداکثر عرض

- مهاجرت

- به حداقل رساندن

- بیش

- اکثر

- چندگانه

- طبیعت

- نیاز

- شبکه

- گره

- به طور معمول

- عدد

- هدف

- مشاهده کردن

- of

- ارائه شده

- on

- ONE

- فقط

- بهینه

- گزینه

- سفارش

- تولید

- با ما

- موازی

- بخش

- الگو

- الگوهای

- افلاطون

- هوش داده افلاطون

- PlatoData

- نقطه

- پست

- ارائه شده

- روند

- در حال پردازش

- محصول

- بهره وری

- وعده

- اثبات

- فراهم می کند

- خواندن

- واقعا

- اخیر

- كاهش دادن

- کاهش

- کاهش

- کاهش

- مکرر

- مورد نیاز

- پاسخ

- ریشه

- دویدن

- پس انداز

- مقیاس پذیری

- مقیاس پذیر

- اسکن

- سناریوها

- تغییر کرد

- نشان می دهد

- زیمنس

- قابل توجه

- سیلیکون

- راه حل

- برخی از

- استاندارد

- جریان

- پشتیبانی از

- جدول

- کار

- تیم

- آزمون

- تست

- که

- La

- شان

- آنها

- آنجا.

- در نتیجه

- اینها

- این

- از طریق

- زمان

- زمان بر

- بار

- به

- امروز

- ابزار

- ابزار

- جمع

- سنتی

- انتقال

- اعتماد

- استفاده کنید

- استفاده

- کاربر

- کاربران

- با استفاده از

- بسیار

- از طريق

- حجم

- بود

- چی

- که

- در حین

- با

- در داخل

- خواستگاری کردن

- کلمات

- با این نسخهها کار

- زفیرنت