در اجلاس اخیر RISC-V، آخرین جلسه پانلی در مورد چیپلت ها بود تراشههای کوچک در اکوسیستم RISC-V. مدیریت آن توسط Calista Redmond، مدیر عامل RISC-V International انجام شد. اعضای میزگرد عبارت بودند از:

- لوران مول، مدیر اجرایی شرکت آرتریس

- Aniket Saha، معاون مدیریت محصول Tenstorrent

- دیل گرینلی، معاون مهندسی ونتانا میکروسیستمز

- راب ایتکن، معمار برجسته Synopsys

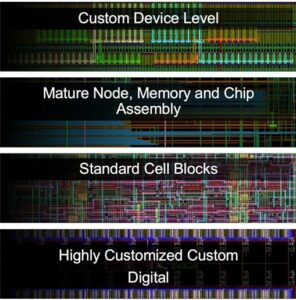

این یک ترکیب کمی عجیب از موضوعات برای من است. بدیهی است که شما می توانید یک پردازنده RISC-V را روی یک چیپلت قرار دهید اما چالش ها واقعاً با هیچ پردازنده دیگری متفاوت نیستند. اما RISC-V و چیپلت ها داغ است و شرکت هایی مانند Ventana در حال ترکیب آنها هستند.

اجازه دهید کمی پیش زمینه در مورد شرکت ها به شما ارائه دهم تا آنها را در چارچوب قرار دهید:

- همانطور که احتمالا می دانید، آرتریس شبکه های روی تراشه (NoCs) را می سازد. این یک شرکت بی طرف در میان فروشندگان چیپلت (و فروشندگان IP) است.

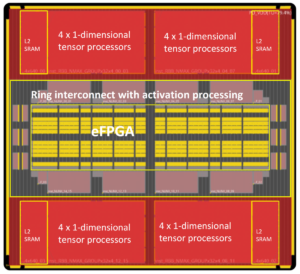

- Tenstorrent در حال طراحی مجموعه ای از تراشه های چند هسته ای RISC-V با عملکرد بسیار بالا است

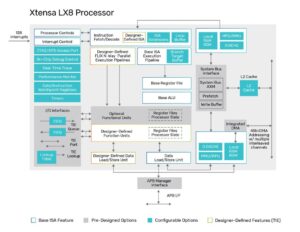

- Ventana دارای IP RISC-V است اما آن را به صورت چیپلت نیز ارائه می دهد

- Synopsys بدیهی است که یک شرکت EDA است اما آنها هسته های RISC-V را در اوایل اجلاس اعلام کردند

]

بحث واقعی

اولین سوال از Calista یک توپ سافت بال بود که می پرسید ارزش چیپلت ها چقدر است.

دیل گفت هیچ چیز خاصی در مورد RISC-V برای چیپلتها وجود ندارد، اما بازار تصمیم میگیرد که چه زمانی کارهای بزرگ یکپارچه یا چیپلتها را انجام دهید. بستگی به این دارد که مشتری برای انجام چه کاری به شما پول بدهد. "ما هم IP و هم چیپلت ها را ارائه می دهیم، برای هر دو جا وجود دارد."

Aniket گفت که "انجام چیپلت ها ارزان نیست، اما انجام چیپلت ها و RISC-V منعطف است و شما می توانید محصولات hew را سریع تولید کنید."

لوران برای هزینه های تولید رفت. کنترل NRE بسیار مهم است زیرا افراد زیادی در حال ساخت 100 میلیون قطعه هستند. بنابراین فروشندگان بیشتری درگیر هستند و یک زنجیره تامین پیچیده وجود دارد. SoC پیچیده است اما چیپلت ها بدتر هستند.

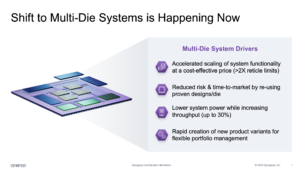

راب به ناهمگونی هایی مانند افزودن چیپلت برای RF و آنالوگ، داشتن یک شتاب دهنده اختیاری و غیره اشاره کرد. این به طور بالقوه بازارهای جدیدی را باز می کند.

کالیستا ادامه داد تا در مورد اینکه ما در خودروسازی کجا هستیم پرسید.

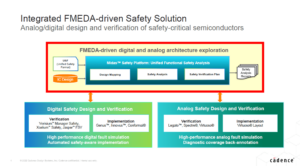

آنیکت خاطرنشان کرد که خودروسازی بسیار محافظهکار است و اکنون آنها در مورد پلتفرمهایی که میتوانند از خودروهای ارزانقیمت به خودروهای سطح بالا مقیاس شوند، تهاجمی هستند. با چیپلت ها، هیچ کس واقعاً ایمنی عملکردی را در نظر نگرفته است.

راب به هوافضا (نه کاملاً خودرو) رفت و در مورد اینکه چگونه معمولاً یک حجم فیزیکی ثابت دههها پیش تعریف شده است، بحث کرد. جا دادن چیزها در آن سخت است.

Laurent: شرکتهای خودروسازی خریداران نهایی کاتالوگ هستند و چیپلتها به آنها اجازه میدهند بهترینها را در هوش مصنوعی، رادار، سرگرمی اطلاعاتی و غیره داشته باشند.

چگونه می توانید نرم افزار را اجرا کنید؟

راب: اگر سیستم را کوچک کنید، خوب است. اما خرید کاتالوگ خودرو کار را سخت تر می کند.

Aniket: بیانیه ای را در رابطه با "اگر آن را اضافه کنید، ما از آن استفاده نخواهیم کرد". پشته های نرم افزار خودرو تا 5 سال دیگر از RISC-V پشتیبانی می کنند که سریع است. آرم 15 سال طول کشید تا به آنجا رسید.

س: برای اتصال به چه چیزی نیاز داریم؟

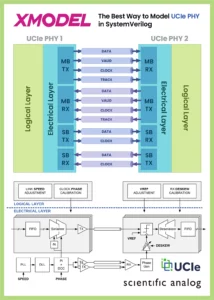

Laurent: این بسیار پیچیده است به خصوص با افرادی که در اطراف برای چیپلت خرید می کنند. PHY از فروشندگان مختلف، ممکن است قابل تعامل باشند. همه مشتاق UCIe هستند. مردم استانداردهایی را می خواهند که چیپلت ها را بهتر بسازد.

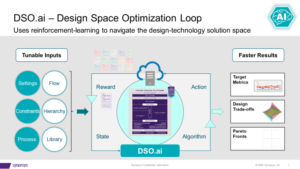

Aniket شکایت کرد که هیچ جریان طراحی استانداردی برای چیپلت وجود ندارد. کمبود بزرگ استاندارد

راب فکر میکند که میتوانیم یک جریان استاندارد داشته باشیم، اما با چیپلتهای مختلف، ما خواهان N جریان طراحی متفاوت نیستیم.

س: در 3-5 سال کجا چیزها را می بینید؟

راب: ما بیشتر همراه با متفاوت خواهیم بود

خرید کاتالوگ ممکن است بسته به OEM های خودرو باشد. تلاش صنعت زیادی را می طلبد. هر چیز ناهمگن زمان بیشتری خواهد برد.

Aniket گفت تراشهها ابتدا در مرکز داده و سپس در خودرو قرار خواهند گرفت. اما موج اول تک فروشنده خواهد بود.

خلاصه

این ترکیبی از چیزهایی است که شرکت کنندگان گفتند و نظرات خودم.

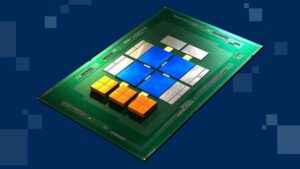

من فکر میکنم در حال حاضر، طراحیهای RISC-V مبتنی بر چیپلت تنها تلاش یک شرکت خواهد بود (به جز، شاید برای حافظه با پهنای باند بالا (HBM). ساختن طرحهایی با چیپلتهای متعدد از شرکتهای مختلف، بسیار پیچیده است. و شبکه ای برای اتصال همه آنها که معمولاً به عنوان RDL شناخته می شود.

برای آینده قابل پیشبینی، طرحها 2.5 بعدی و نه سهبعدی واقعی (جایی که قالبها روی هم چیده میشوند و با تراشههای سیلیکونی یا TSV ارتباط برقرار میکنند) خواهند بود.

خودرو مجموعه ای از چالش های خاص خود را دارد، به ویژه اطمینان از اینکه طراحی های مبتنی بر چیپلت در محیطی با ارتعاش زیاد قابل اعتماد هستند. این به آزمایش گسترده نیاز دارد. مسئله دیگر تضمین ایمنی عملکردی در یک محیط چند قالبی است.

UCIe امیدوارکننده است و تا حدودی مبتنی بر PCIe است. شرکتهای PCIe قابلیت اطمینان را از طریق plugfests تضمین کردند. نمیدانم چگونه میتوانید از لحاظ اقتصادی از قابلیت همکاری UCIe در چیپلتها از طریق مکانیسم مشابه اطمینان حاصل کنید.

در نهایت، علاوه بر چالشهای فنی، اگر بخواهیم به نیروانا برسیم که بتوانیم چیپلتها را خارج از قفسه بخریم و آنها را در سیستمها با هزینه معقول جمع کنیم، چالشهای تجاری نیز وجود دارد. بزرگترین چالش این است که چه کسی موجودی چیپلت ها را پرداخت کرده و نگه می دارد. اگر همه چیپلتها بر حسب تقاضا ساخته شوند، بسیاری از مزایای زمان چرخه سریع از بین خواهند رفت.

اما تراشههای RISC-V مطمئناً بهسرعت در قالب طرحهای چند قالبی بر روی اینترپوزرهای 2.5 بعدی که توسط یک شرکت ساخته شدهاند، عرضه میشوند.

همچنین خواندن:

NoC ها به معماران انعطاف پذیری در طراحی سیستم در RISC-V می دهند

جفت شدن هسته های RISC-V با NoC ها، پروتکل های SoC را به هم پیوند می دهد

به روز رسانی #60DAC از Arteris

اشتراک گذاری این پست از طریق:

- محتوای مبتنی بر SEO و توزیع روابط عمومی. امروز تقویت شوید.

- PlatoData.Network Vertical Generative Ai. به خودت قدرت بده دسترسی به اینجا.

- PlatoAiStream. هوش وب 3 دانش تقویت شده دسترسی به اینجا.

- PlatoESG. کربن ، CleanTech، انرژی، محیط، خورشیدی، مدیریت پسماند دسترسی به اینجا.

- PlatoHealth. هوش بیوتکنولوژی و آزمایشات بالینی. دسترسی به اینجا.

- منبع: https://semiwiki.com/ip/arteris/338888-risc-v-and-chiplets-a-panel-discussion/

- : دارد

- :است

- :نه

- :جایی که

- $UP

- 100M

- سال 15

- ٪۱۰۰

- 167

- 200

- 300

- 3d

- a

- قادر

- درباره ما

- شتاب دهنده

- واقعی

- اضافه کردن

- اضافه کردن

- اضافه

- مزایای

- هوافضا

- مهاجم

- پیش

- AI

- معرفی

- در امتداد

- همچنین

- در میان

- an

- و

- اعلام کرد

- دیگر

- هر

- معماران

- هستند

- ARM

- دور و بر

- AS

- پرسیدن

- خواهان

- At

- خودرو

- زمینه

- مستقر

- BE

- بودن

- بهترین

- بهتر

- بزرگ

- بزرگترین

- بیت

- هر دو

- ساختن

- بنا

- ساخته

- اما

- by

- نام

- CAN

- اتومبیل

- کاتالوگ

- مدیر عامل شرکت

- قطعا

- زنجیر

- به چالش

- چالش ها

- ارزان

- رنگ

- ترکیب

- ترکیب

- بیا

- آینده

- تجاری

- ارتباط

- شرکت

- شرکت

- پیچیده

- بغرنج

- اتصال

- اتصال

- محافظه کار

- در نظر گرفته

- زمینه

- کنترل

- COO

- هزینه

- هزینه

- مشتری

- چرخه

- مرکز داده

- دهه

- مشخص

- ارائه

- بستگی دارد

- بستگی دارد

- طرح

- طراحی

- طرح

- مردن

- مختلف

- بحث کردیم

- گفتگو

- برجسته

- do

- عمل

- آیا

- هر

- پیش از آن

- تلاش

- پایان

- مهندسی

- اطمینان حاصل شود

- تضمین

- حصول اطمینان از

- محیط

- به خصوص

- هر کس

- جز

- وسیع

- FAST

- پایان

- نام خانوادگی

- مناسب

- ثابت

- انعطاف پذیری

- قابل انعطاف

- جریان

- جریانها

- برای

- قابل پیش بینی

- فرم

- از جانب

- تابعی

- بیشتر

- آینده

- دریافت کنید

- دادن

- سخت

- سخت تر

- آیا

- داشتن

- زیاد

- عملکرد بالا

- نگه داشتن

- HOT

- چگونه

- HTTPS

- i

- if

- مهم

- in

- صنعت

- بین المللی

- قابلیت همکاری

- متقابل

- به

- فهرست

- گرفتار

- IP

- موضوع

- IT

- ITS

- JPG

- مشتاق

- نگاه داشتن

- دانستن

- شناخته شده

- عدم

- نام

- اجازه

- پسندیدن

- دیگر

- از دست رفته

- خیلی

- کم

- ساخت

- باعث می شود

- مدیریت

- ساخته

- بسیاری

- بسیاری از مردم

- بازار

- بازارها

- حداکثر عرض

- ممکن است..

- شاید

- me

- مکانیزم

- یک پارچه

- بیش

- چندگانه

- my

- نیاز

- شبکه

- خنثی

- جدید

- نه

- هیچ چی

- اکنون

- of

- on

- بر روی تقاضا

- ONE

- باز می شود

- دیدگاه ها

- or

- دیگر

- خارج

- خود

- تابلو

- میزگرد

- شرکت کنندگان

- ویژه

- بخش

- پرداخت

- مردم

- شاید

- فیزیکی

- سیستم عامل

- افلاطون

- هوش داده افلاطون

- PlatoData

- مقام

- پست

- بالقوه

- شاید

- پردازنده

- محصول

- مدیریت تولید

- تولید

- محصولات

- امید بخش

- پروتکل

- ارائه

- خرید

- قرار دادن

- سوال

- کاملا

- رادار

- خواندن

- واقعا

- معقول

- اخیر

- مربوط

- قابلیت اطمینان

- قابل اعتماد

- نیاز

- اتاق

- دویدن

- ایمنی

- سعید

- مقیاس

- دیدن

- جلسه

- تنظیم

- خریداران

- خريد كردن

- مشابه

- پس از

- تنها

- کوچک

- So

- نرم افزار

- تاحدی

- خاص

- انباشته

- پشته

- استاندارد

- استانداردهای

- بیانیه

- قله

- عرضه

- زنجیره تامین

- پشتیبانی

- سیستم

- سیستم های

- گرفتن

- سخنگو

- فنی

- تست

- که

- La

- آنها

- سپس

- آنجا.

- آنها

- اشیاء

- فکر می کنم

- فکر می کند

- این

- از طریق

- روابط

- زمان

- به

- هم

- در زمان

- بالا

- تاپیک

- درست

- نهایی

- زیر

- بروزرسانی

- استفاده کنید

- معمولا

- ارزش

- فروشنده

- فروشندگان

- بسیار

- از طريق

- حجم

- vp

- می خواهم

- بود

- موج

- we

- رفت

- بود

- چی

- چه زمانی

- که

- WHO

- اراده

- با

- بدتر

- سال

- شما

- زفیرنت