نشست سالانه بین المللی دستگاه های الکترونیکی (IEDM) ماه گذشته برگزار شد. یکی از ارائههای این دوره کوتاه توسط متیو متز از اینتل بود سیستم های مواد جدید برای ادامه قانون مور. در اصل این نگاهی بود به برخی از احتمالات برای آنچه پس از اتمام بخار سیلیکون به وجود می آید.

![]()

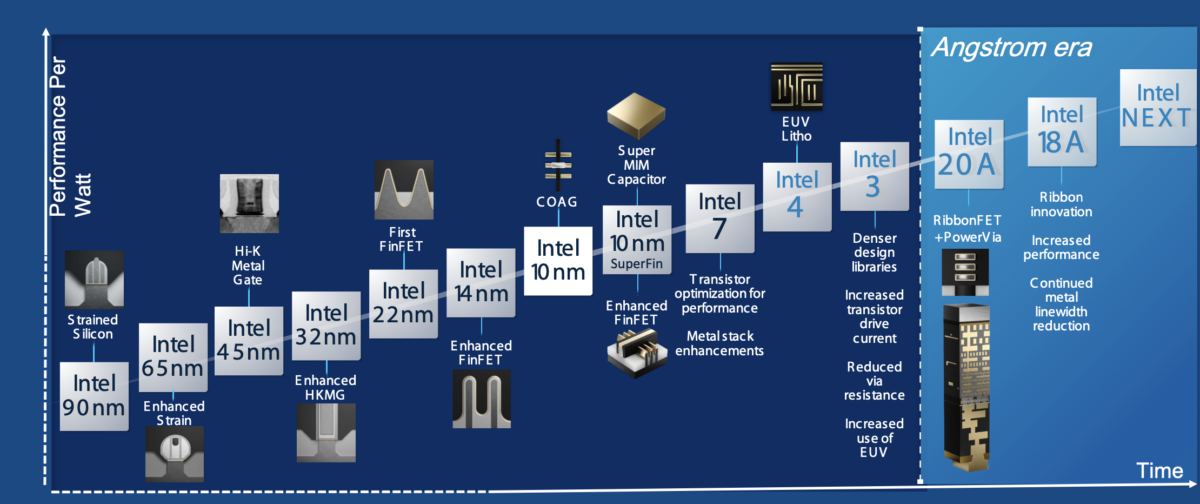

متیو با نگاهی به چگونگی تغییر جهان توسط ترانزیستور و به ویژه نوآوریهای موادی که نقشه راه فرآیند خود اینتل را طی دههها هدایت کرده است، شروع کرد. در 90 نانومتر سیلیکون صاف شده داشتیم و به دنبال آن دروازه فلزی HiK قرار داشت. اینتل اولین شرکتی بود که با FinFET وارد بازار شد (اگرچه در آن زمان آن را TriGate می نامید). در اینتل 4، لیتوگرافی EUV برای اولین بار معرفی شد.

![]()

همانطور که احتمالا می دانید، اینتل در حال توسعه فناوری 5 فرآیند در 4 سال است، که آشکارا تهاجمی است، اما ظاهراً همه هنوز در مسیر هستند. اینتل 20A اولین فرآیند با گیت همه جانبه (GAA) خواهد بود که اینتل آن را ribbonFET می نامد. اینتل همچنین یک نقشه راه بسته بندی پیشرفته تهاجمی دارد، اما از آنجایی که تمرکز بحث این بود که در آینده چه چیزی را روی ویفرها قرار خواهیم داد، نه اینکه چگونه آنها را کنار هم قرار دهیم، صرف نظر می کنم.

![]()

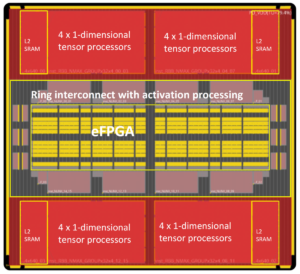

اینتل تنها نیست که از گیت های همه جانبه استفاده می کند. طی چند سال گذشته در کنفرانسهایی مانند IEDM، همه تولیدکنندگان بزرگ و سازمانهای تحقیقاتی نسخهای از نتایج همهجانبه دروازههای نانوصفحه را منتشر کردهاند. مقاطع بالا را ببینید.

نوآوری بزرگ بعدی برنامه ریزی شده FET یا CFET مکمل با n ترانزیستور بر ترانزیستور p است. در واقع این موضوع تقریباً موضوع IEDM امسال بود که بسیاری از افراد نوآوری های مختلفی را در ساخت CFET اعلام کردند تا مقیاس منطقه ای 1.5 برابر تا 2 برابر را دریافت کنند.

![]()

نوآوری دیگری که اینتل (همراه با سایرین) دنبال می کند، شبکه تحویل برق پشتی (PDN پشتی) به همراه چیزی است که اینتل PowerVia می نامد. این فناوریها اجازه میدهند سیگنالها و برق از هم جدا شوند و دیگر تداخلی با یکدیگر نداشته باشند، همانطور که در طول تاریخ اتفاق افتاده است، زمانی که تمام اتصالات در قسمت جلویی (خوب، تنها طرف تا همین اواخر) بود.

بزرگترین چالش دیوار قدرت است. دریافت بیش از 100 وات در هر سانتی متر مربع خنک کننده بسیار دشوار است. در مورد چگونگی بهبود شرایط، احتمالات مختلفی وجود دارد:

- پیشرفت های معمولی ماسفت

- نانو نوارهای ژرمانیوم سیلیکونی صاف شده (SiGe).

- نانو نوارهای Ge یا InGaAs

- FET های تونلی

- Dirac FETs (گرافن و 2D)

- NCFET خازن منفی

- محاسبه در حافظه با FerroTunnel Junction یا FerroFET

![]()

انجام مواد دو بعدی به جای چسبیدن به سه بعدی جذابیت های زیادی دارد. اما چالش های عمده ای برای یافتن مواد خوب وجود دارد. من مطمئن هستم که شما نام نانولوله های کربنی (CNT) را شنیده اید، اما علیرغم جذابیت، هیچ پیشرفت واقعی در چالش ساخت این نانولوله های قابل اعتماد برای ده سال وجود نداشته است. گرافن دوبعدی است اما فاقد شکاف باندی است که سوئیچ های ساختمانی را به یک چالش تبدیل می کند. فسفرن در دمای بالا فرار است و ساخت ترانزیستور کامل را غیرممکن می کند.

![]()

به نظر می رسد جذاب ترین راه حل توسعه دی کالکوژنیدهای فلزات واسطه یا TMD باشد. اعتراف می کنم که این اولین باری بود که حداقل با این نام در مورد اینها می شنیدم. این یکی از رویکردهای امیدوارکننده تر با استفاده از مواد دو بعدی است. TMD یک تک لایه است که کنترل گیت خوبی را ارائه می دهد بنابراین قدرت کمتری دارد. آنها تحرک بهتری نسبت به سیلیکون دارند، بنابراین عملکرد خوبی دارند. همچنین، یک باند بزرگ، تونل زنی منبع-زهکشی محدود است.

متیو جزئیات بسیار زیادی را در مورد چالش ها و وعده های تولید ترانزیستورهای دو لایه TMD، به ویژه ترانزیستورهای تک لایه دوبعدی در حال رشد، و نحوه تماس با آنها توضیح داد. برای ترکیبات ترانزیستور n جذاب ترین مواد آنتیموان (Sb) و بیسموت (Bi) به نظر می رسد. برای ترانزیستور p، روتنیوم (Ru).

![]()

بخش آخر نگاهی به کاهش نیازهای برق و سوئیچینگ پیشرفته، به ویژه دستگاه های مداری اسپین مغناطیسی-الکتریک (MESO) بود. سوئیچینگ را می توان در حدود 0.1 ولت با کاهش توان مربوطه انجام داد.

نتیجه گیری متیو این است که کارهایی که در اینتل با TMD انجام می شود، نویدبخش ادامه مقیاس CMOS است و دستگاه های MESO وعده های زیادی برای کاهش شدید توان دارند. اما این تحقیقات نسبتاً اولیه ای است و هنوز کارهای زیادی باید انجام شود تا هر یک از این فناوری ها به واقعیت عملی تبدیل شوند.

همچنین خواندن:

Big Race 2024 TSMC N2 و Intel 18A است

IEDM Buzz – اینتل نوآوری جدید مقیاس بندی ترانزیستور عمودی را پیش نمایش می کند

اینتل عصر جدیدی از بسته بندی پیشرفته با بسترهای شیشه ای را آغاز می کند

اشتراک گذاری این پست از طریق:

- محتوای مبتنی بر SEO و توزیع روابط عمومی. امروز تقویت شوید.

- PlatoData.Network Vertical Generative Ai. به خودت قدرت بده دسترسی به اینجا.

- PlatoAiStream. هوش وب 3 دانش تقویت شده دسترسی به اینجا.

- PlatoESG. کربن ، CleanTech، انرژی، محیط، خورشیدی، مدیریت پسماند دسترسی به اینجا.

- PlatoHealth. هوش بیوتکنولوژی و آزمایشات بالینی. دسترسی به اینجا.

- منبع: https://semiwiki.com/semiconductor-manufacturers/340336-iedm-what-comes-after-silicon/

- : دارد

- :است

- :نه

- 01

- 1

- 14

- ٪۱۰۰

- 2024

- 27

- 29

- 2D

- مواد سه بعدی

- 30

- 3d

- 40

- 50

- 53

- 58

- 8

- a

- درباره ما

- بالاتر

- پیشرفت

- پیشرفته

- پس از

- مهاجم

- معرفی

- اجازه دادن

- تقریبا

- تنها

- در امتداد

- همچنین

- هر چند

- am

- an

- و

- اعلام كردن

- سالیانه

- رویکردها

- هستند

- محدوده

- دور و بر

- AS

- At

- جاذبه

- جاذبه

- جالب

- به عقب

- BE

- بوده

- بهتر

- بزرگ

- بزرگترین

- بنا

- اما

- by

- نام

- تماس ها

- CAN

- کربن

- نانولوله های کربنی

- مورد

- به چالش

- چالش ها

- تغییر

- می آید

- نسبتاً

- مکمل

- کامل

- محاسبه

- نتیجه

- همایش ها

- تماس

- ادامه داد:

- متناظر

- زن و شوهر

- دوره

- صلیب

- دهه

- تحویل

- با وجود

- جزئیات

- پروژه

- دستگاه ها

- مشکل

- عمل

- انجام شده

- پایین

- رانده

- هر

- در اوایل

- هر دو

- دیگر

- عصر

- ماهیت

- هر کس

- واقعیت

- FET

- پیدا کردن

- نام خانوادگی

- بار اول

- تمرکز

- به دنبال

- برای

- جلو

- آینده

- دروازه

- دریافت کنید

- دادن

- شیشه

- رفتن

- خوب

- گرافن

- در حال رشد

- بود

- آیا

- شنیده

- زیاد

- به لحاظ تاریخی

- چگونه

- چگونه

- HTTPS

- i

- غیر ممکن

- بهبود

- in

- ابداع

- نوآوری

- در عوض

- اینتل

- مداخله کردن

- بین المللی

- به

- معرفی

- IT

- دانستن

- بزرگ

- نام

- قانون

- لایه

- کمترین

- پسندیدن

- محدود شده

- دیگر

- نگاه کنيد

- خیلی

- کاهش

- عمده

- ساخت

- ساخت

- تولید کنندگان

- تولید

- بسیاری

- بسیاری از مردم

- بازار

- مصالح

- متی

- حداکثر عرض

- نشست

- فلز

- تحرک

- ماه

- بیش

- اکثر

- نام

- شبکه

- جدید

- بعد

- نه

- of

- on

- ONE

- فقط

- or

- سازمان های

- دیگر

- خارج

- روی

- خود

- بسته بندی

- ویژه

- مردم

- برای

- کارایی

- محل

- برنامه ریزی

- افلاطون

- هوش داده افلاطون

- PlatoData

- فرصت

- پست

- قدرت

- عملی

- ارایهها در همایشهای علمی

- پریمیر لیگ در انگلستان

- شاید

- روند

- فرآیندهای

- وعده

- وعده

- امید بخش

- منتشر شده

- پیگیری

- قرار دادن

- کاملا

- نژاد

- خواندن

- واقعی

- واقعیت

- تازه

- کاهش

- مورد نیاز

- تحقیق

- نتایج

- نقشه راه

- RU

- اجرا می شود

- مقیاس گذاری

- پرده

- بخش

- بخش

- دیدن

- به نظر می رسد

- به نظر می رسد

- کوتاه

- عکس

- نشان می دهد

- طرف

- سیگنال

- سیلیکون

- پس از

- تنها

- So

- راه حل

- برخی از

- مربع

- آغاز شده

- بخار

- چسبیده

- هنوز

- مطمئن

- سیستم های

- صحبت

- فن آوری

- پیشرفته

- پیشرفت تکنولوژی

- ده

- نسبت به

- که

- La

- آینده

- جهان

- آنها

- موضوع

- سپس

- آنجا.

- اینها

- آنها

- اشیاء

- این

- زمان

- با عنوان

- به

- با هم

- در زمان

- مسیر

- انتقال

- tsmc

- زیر

- تا

- طلیعه

- با استفاده از

- مختلف

- نسخه

- عمودی

- بسیار

- از طريق

- فرار

- دیوار

- بود

- we

- خوب

- رفت

- چی

- چه زمانی

- که

- اراده

- با

- مهاجرت کاری

- جهان

- سال

- شما

- زفیرنت