قبلاً در مورد آن وبلاگ می نوشتم تأیید عملکرد IC و ASIC، بنابراین امروز وقت آن است که با وضعیت تأیید عملکرد FPGA آن را کامل کنیم. گروه تحقیقاتی ویلسون از سال 2018 هر دو سال یک بار گزارش FPGA را جمع آوری کرده است، بنابراین این سومین بار است که آنها بر روی این بخش طراحی تمرکز کرده اند. با 5.8 میلیارد دلار بازار FPGA قابل توجه است و پیش بینی می شود تا سال 8.1 به 2025 میلیارد دلار افزایش یابد. FPGA ها در سال 1984 با ظرفیت گیت محدود شروع به کار کردند و اکنون به میلیون ها گیت، پردازنده و پروتکل های داده استاندارد شده تبدیل شده اند.

برنامههای کاربردی با حجم کم از NRE دستگاههای FPGA بهره میبرند و مهندسان میتوانند به سرعت طرحهای خود را با تأیید و اعتبارسنجی در سرعت نمونهسازی کنند. اکنون FPGA ها شامل پردازنده هایی مانند: Xilinx Zynq UltraSCALE, اینتل Stratix, ریزتراشه SmartFusion. از 980 شرکتکننده در مطالعه تأیید عملکرد، سبکهای طراحی FPGA و SoC قابل برنامهریزی FPGA محبوبترین هستند.

از آنجایی که اندازه FPGA ها اخیراً افزایش یافته است، شانس انتشار تولید بدون اشکال به تنها 17 درصد کاهش یافته است که حتی بدتر از 30 درصد پروژه های IC و ASIC برای سیلیکون اول صحیح است. واضح است که برای سیستم های پیچیده FPGA به تأیید عملکرد بهتری نیاز داریم.

انواع باگ های موجود در تولید به چند دسته تقسیم می شوند:

- 53٪ - منطقی یا عملکردی

- 31٪ - سیستم عامل

- 29٪ - ساعت

- 28٪ - زمان بندی، مسیر بسیار کند است

- 21٪ - زمان بندی، مسیر خیلی سریع

- 18٪ - رابط سیگنال مختلط

- 9٪ - ویژگی ایمنی

- 8٪ - ویژگی امنیتی

با بزرگنمایی بزرگترین دسته شکست، منطقی یا عملکردی، پنج دلیل اصلی وجود دارد.

پروژه های FGPA اکثراً به موقع کامل نشدند، یک بار دیگر به دلیل اندازه بزرگتر سیستم ها، پیچیدگی منطق و حتی روش های تأیید استفاده می شود.

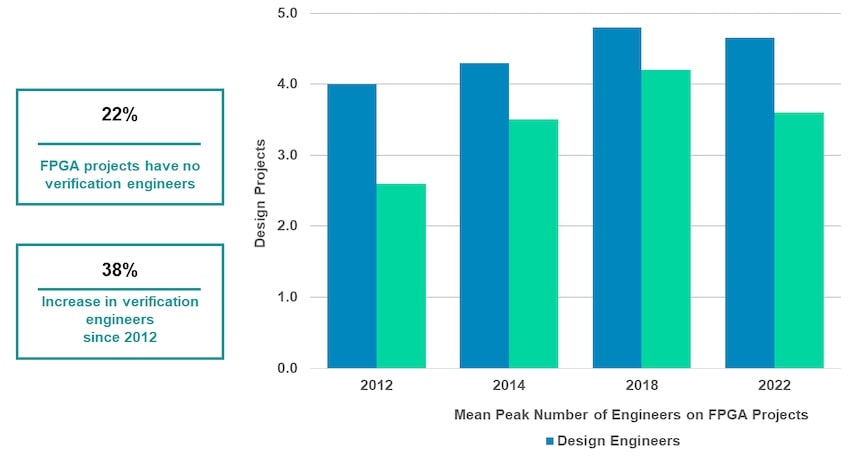

مهندسان یک تیم FPGA میتوانند عناوین متمایزی مانند مهندس طراحی یا مهندس تأیید داشته باشند، با این حال در 22 درصد از پروژهها مهندس تأیید وجود نداشت - به این معنی که مهندسان طراح دو وظیفه را انجام دادند و IP خود را تأیید کردند. در طول 10 سال گذشته، 38 درصد افزایش در تعداد مهندسان تأیید در یک پروژه FPGA وجود داشته است، بنابراین این پیشرفت به سمت تولید بدون اشکال است.

مهندسان تأیید در پروژه های FPGA بیشتر وقت خود را با 47٪ روی وظایف اشکال زدایی صرف می کنند:

- 47٪ - اشکال زدایی

- 19% - ایجاد شبیه سازی تست و اجرا

- 17٪ - توسعه Testbench

- 11% – برنامه ریزی آزمون

- 6٪ - سایر موارد

تعداد پردازنده های تعبیه شده به طور پیوسته در طول زمان افزایش یافته است، بنابراین 65٪ از طرح های FPGA در حال حاضر دارای یک یا چند هسته پردازنده هستند، که میزان تأیید بین رابط های سخت افزاری و نرم افزاری را افزایش می دهد. و مدیریت شبکه های روی تراشه

پردازنده همیشه محبوب RISC-V در 22 درصد از FPGA ها تعبیه شده است و شتاب دهنده های هوش مصنوعی در 23 درصد از پروژه ها استفاده می شود. میانگین تعداد دامنههای ساعتی 3-4 در FPGA استفاده میشود و برای تأیید به شبیهسازی زمانبندی سطح دروازه، بهعلاوه استفاده از ابزارهای Clock Domain Crossing (CDC) برای تأیید نیاز دارند.

ویژگی های امنیتی به 49 درصد از طرح های FPGA اضافه می شوند تا داده های حساس را نگهداری کنند، به علاوه 42 درصد از پروژه های FPGA از استانداردها یا دستورالعمل های حیاتی ایمنی پیروی می کنند. در SemiWiki ما اغلب در مورد آن وبلاگ می نویسیم ISO 26262 و DO-254 استانداردها تلاش های طراحی ایمنی عملکردی (FuSa) بین 25٪ تا 50٪ از زمان کلی پروژه را می گیرد.

سه زبان اصلی تأیید عبارتند از VHDL، SystemVerilog و Verilog. اما به جهش های اخیر در زبان های پایتون و C/C++ نیز توجه کنید.

محبوبترین متدولوژیهای FPGA و کتابخانههای کیس پایه آزمایشی عبارتند از: Accellera UVM، OSVVM و UVVM. مبتنی بر پایتون کوکوت حتی به عنوان یک دسته جدید برای سال 2022 اضافه شد.

زبانهای ادعایی توسط SystemVerilog Assertions (SVA) با 45% و پس از آن Accellera Open Verification Library (OVL) با 13% و PSL با 11% پیشتاز هستند. طرحهای FPGA ممکن است VHDL را برای طراحی RTL و SVA را برای ادعاها ترکیب کنند.

بررسی رسمی دارایی در بین پروژه های FPGA در حال رشد است، به خصوص که برنامه های رسمی خودکار بیشتری توسط فروشندگان EDA معرفی شده اند.

رویکردهای راستیآزمایی مبتنی بر شبیهسازی در 10 سال گذشته، پذیرش ثابت را نشان میدهد، که به ترتیب مرتبط فهرست شدهاند: پوشش کد، پوشش عملکردی، ادعاها، تصادفی محدود.

خلاصه

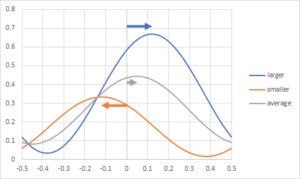

تعداد کم 17 درصد بدون اشکال برای پروژههای FPGA در سال 2022 که آن را به تولید رساند، شگفتانگیزترین عدد برای من بود، زیرا تلاش برای فراخوانی یا برنامهریزی مجدد یک دستگاه در این زمینه گران است و اصلاح آن زمان بر است. یک رویکرد راستیآزمایی عملکردی قویتر باید منجر به فرار اشکالات کمتری در تولید شود، و تقسیم شرکتکنندگان در مطالعه به دو گروه مزایای آن را نشان میدهد.

کامل را بخوانید کاغذ سفید 18 صفحه ای اینجا.

وبلاگهای مرتبط

اشتراک گذاری این پست از طریق:

- محتوای مبتنی بر SEO و توزیع روابط عمومی. امروز تقویت شوید.

- پلاتوبلاک چین. Web3 Metaverse Intelligence. دانش تقویت شده دسترسی به اینجا.

- منبع: https://semiwiki.com/eda/324651-the-state-of-fpga-functional-verification/

- 1

- 10

- 2018

- 2022

- a

- درباره ما

- شتاب دهنده ها

- اضافه

- پایبند بودن

- اتخاذ

- AI

- در میان

- مقدار

- و

- برنامه های کاربردی

- روش

- رویکردها

- برنامه های

- اسم

- اتوماتیک

- میانگین

- بودن

- سود

- بهتر

- میان

- بیلیون

- اشکال

- اشکالات

- ظرفیت

- دسته

- دسته بندی

- علت

- ایجاد می شود

- علل

- CDC

- شانس

- بررسی

- به وضوح

- ساعت

- رمز

- ترکیب

- کامل

- پیچیده

- پیچیدگی

- پوشش

- ایجاد

- بحرانی

- داده ها

- طرح

- طرح

- دستگاه

- دستگاه ها

- DID

- متمایز

- دامنه

- حوزه

- کاهش یافته است

- تلاش

- تلاش

- جاسازی شده

- مهندس

- مورد تأیید

- به خصوص

- حتی

- هر

- گران

- شکست

- سقوط

- امکانات

- رشته

- نام خانوادگی

- متمرکز شده است

- به دنبال

- رسمی

- یافت

- fpga

- از جانب

- تابعی

- گیتس

- گروه

- گروه ها

- شدن

- در حال رشد

- رشد کرد

- دستورالعمل ها

- سخت افزار

- نگه داشتن

- HTML

- HTTPS

- in

- شامل

- افزایش

- افزایش

- افزایش

- اینتل

- رابط

- معرفی

- IP

- IT

- جهش

- زبان ها

- بزرگتر

- بزرگترین

- رهبری

- رهبری

- کتابخانه ها

- کتابخانه

- محدود شده

- ذکر شده

- کم

- ساخته

- مدیریت

- بازار

- حداکثر عرض

- معنی

- متدولوژی ها

- روش

- میلیون ها نفر

- بیش

- اکثر

- محبوبترین

- نیاز

- شبکه

- جدید

- عدد

- ONE

- باز کن

- سفارش

- به طور کلی

- خود

- مقاله

- شرکت کنندگان

- گذشته

- مسیر

- افلاطون

- هوش داده افلاطون

- PlatoData

- به علاوه

- محبوب

- پست

- پردازنده

- پردازنده ها

- تولید

- پیشرفت

- پروژه

- پروژه ها

- ویژگی

- پروتکل

- نمونه اولیه

- پــایتــون

- به سرعت

- تصادفی

- اخیر

- تازه

- آزاد

- ربط

- گزارش

- نیاز

- تحقیق

- گروه تحقیقاتی

- تنومند

- ریشه

- دور

- در حال اجرا

- ایمنی

- تیم امنیت لاتاری

- بخش

- حساس

- چند

- باید

- نشان

- نشان می دهد

- زیمنس

- سیلیکون

- پس از

- قابل اندازه

- اندازه

- So

- نرم افزار

- سرعت

- صرف

- استانداردهای

- آغاز شده

- دولت

- ثابت

- مهاجرت تحصیلی

- تعجب آور

- سیستم های

- گرفتن

- وظایف

- تیم

- تکنیک

- آزمون

- La

- دولت

- شان

- سوم

- سه

- زمان

- زمان

- عناوین

- به

- امروز

- هم

- ابزار

- بالا

- طرف

- انواع

- استفاده کنید

- فروشندگان

- تایید

- تایید

- تایید

- از طريق

- حجم

- که

- سفید

- کتاب سفید

- ویلسون

- سال

- زفیرنت