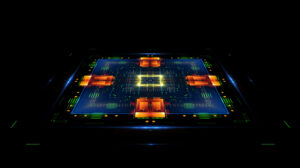

در عملکرد دستگاه های CPU مدرن، 80% تا 90% از مصرف انرژی و تاخیرهای زمان بندی ناشی از حرکت داده ها بین CPU و حافظه خارج از تراشه است. برای کاهش این نگرانی عملکرد، طراحان در حال اضافه کردن حافظه روی تراشه اضافی به CPU خود هستند. به طور سنتی، SRAM پرکاربردترین نوع حافظه CPU روی تراشه بوده است. متاسفانه SRAM در حال حاضر به حجم صدها مگابایت محدود شده است. این محدودیت حافظه روی تراشه ممکن است برای برنامه های کاربردی پیشرو کافی نباشد.

برنامههای CPU آینده، مانند برنامهنویسی مدل زبان هوش مصنوعی و پردازش تصویر برای ویدیوهای 8K UHD، به پهنای باند دسترسی به حافظه ورودی/خروجی در محدوده 10 ترابایت بر ثانیه نیاز دارند. برای برآورده کردن این نیازهای پهنای باند، حافظه CPU روی تراشه باید بزرگتر از 1 ترابایت باشد. یک جایگزین SRAM ممکن است برای برآورده کردن این نیازهای حافظه روی تراشه آینده مورد نیاز باشد. یکی از راه حل های ممکن برای این مشکل استفاده از حافظه با دسترسی تصادفی مقاومتی (ReRAM) است. [1,2,3،XNUMX،XNUMX]

دستگاه ReRAM یک سلول حافظه غیر فرار است که حاوی مواد ممریستور است. این مواد به عنوان عایق دی الکتریک عمل می کنند. هنگامی که یک ولتاژ به اندازه کافی بالا اعمال می شود یک مسیر هدایت تشکیل می شود. مواد حافظه معمولی که به عنوان ممریستور استفاده می شوند عبارتند از HfO2، تا2O5و TiO2. [4] وضعیت مقاومت سلول حافظه را می توان با استفاده از مدارهای الکترونیکی برای تعیین اینکه آیا سلول حافظه برنامه ریزی شده یا پاک شده است، خواند، بنابراین وضعیت بیت حافظه را شناسایی کرد. سلول های حافظه ReRAM را می توان به صورت عمودی مانند معماری 3D-NAND برای افزایش تراکم ذخیره سازی روی هم قرار داد.

در این مقاله، ساخت مجازی SEMulator3D برای مسیریابی فرآیند و تجسم معماری های بالقوه 3D ReRAM استفاده خواهد شد. ما مقاومت سلول را به عنوان تابعی از شکل سلول حافظه، همراه با عملکرد Id-Vg ترانزیستور کانال تعبیه شده در یک دستگاه ReRAM برآورد خواهیم کرد.

یک مدل ReRAM سه بعدی در شکل 3 نشان داده شده است. این دستگاه دارای 1 لایه خطوط کلمه (WL) با ستون هایی است که در یک آرایه با فاصله شش ضلعی قرار گرفته اند. خطوط کلمات با لایه های متناوب رسانای فلزی و دی الکتریک اکسید تشکیل شده اند. ستون ها از طریق WL حک می شوند و سپس یک لایه نازک از مواد حافظه بر روی دیواره های جانبی ستون ها قرار می گیرد. مواد حافظه از پایین و بالای ستون ها برداشته می شود و فقط مواد روی دیواره های ستون باقی می ماند. سپس ستون ها با فلز نسوز و تنگستن پر می شوند.

در زیر لایههای آرایه، کنتاکتها و اتصال فلزی به منبع، تخلیه و گیتهای ترانزیستورهای اثر میدانی گیت (GAA FET) وجود دارد. تخلیه ترانزیستور به ستون آرایه حافظه متصل می شود و با مدار WL ترکیب می شود تا عملکرد هر سلول حافظه را ارائه دهد.

سلول حافظه از دو الکترود فلزی تشکیل شده است: خط کلمه هادی فلزی و یک الکترود فلزی نسوز (شکل 2). در طول شبیه سازی فرآیند مجازی این دستگاه، از متغیرهای فرآیند برای تنظیم و تنظیم مجدد ممریستور استفاده می کنیم. اعمال ولتاژ عمدی مسیرهای رسانای میکروسکوپی به نام رشته های رسانا را ایجاد می کند. هنگامی که سیگنال های الکتریکی با قطبیت های مختلف اعمال می شود، یون های باردار داخل ممریستور حرکت می کنند تا رشته رسانا را تشکیل دهند (تنظیم) یا حل کنند (تنظیم مجدد).

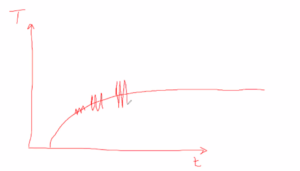

مقاومت رشته رسانا در ولتاژهای برنامه مختلف متفاوت است. حالت مقاومت کم در محدوده 10k اهم (تنظیم) و حالت مقاومت بالا در محدوده 1M اهم (تنظیم مجدد) است. [5] ما یک مدل مجازی برای نشان دادن مقاومت های سوئیچینگ یک دستگاه ReRAM سه بعدی ایجاد کردیم که نتایج در شکل 3 نشان داده شده است. حالت مقاومتی بالای ممریستور تقریباً 3 برابر مقاومت بالاتر از حالت مقاومت پایین است.

سپس یک طراحی مجازی آزمایشات (DOE) برای درک بهتر همبستگی بین نسبت مقاومت سلول حافظه و اندازه و شکل سلول حافظه اجرا شد. متغیرهای آزمایش عبارت بودند از CD ستون، ضخامت WL و ضخامت ممریستور. تجزیه و تحلیل نتایج DOE نشان می دهد که CD ستون و ضخامت ممریستور بیشترین پاسخ را نشان می دهد. شکل 4 نمودار کانتوری نسبت مقاومت سلول حافظه را در مقابل این دو متغیر نشان می دهد. یک تغییر 3 برابری در مقاومت سلول حافظه برای مقادیر بالای شعاع ستون و ضخامت ممریستور وجود داشت. تفاوت در شکل سلول حافظه در محدوده مورد مطالعه بر توانایی خواندن حالات حافظه ممریستور تأثیر نمی گذارد، اما می تواند بر توانایی تشخیص حالت های برنامه در یک دستگاه چند بیتی در هر سلول تأثیر بگذارد.

ممریستور را می توان با استفاده از جریان <0.10 uA و ولتاژ <0.5V برنامه ریزی کرد. این تنظیمات ولتاژ و جریان به ممریستورها (حافظه ReRAM) اجازه می دهد تا به راحتی به عنوان حافظه روی تراشه در دستگاه های منطقی پیشرفته ادغام شوند. شبیهسازی دستگاه SEMulator3D قبلاً نشان داده بود که یک ترانزیستور زیر آرایهای GAA FET باید بتواند ولتاژ و جریان مورد نیاز توسط حالت تنظیم و تنظیم مجدد یک سلول حافظه ممریستور را هدایت کند. [6]

دو مشکل عمده دستگاه های CPU مدرن مصرف انرژی و زمان تاخیر ناشی از حرکت داده ها بین CPU و حافظه خارج از تراشه است. افزایش اندازه حافظه روی تراشه ممکن است این مشکلات را حل کند. در این مطالعه، ما از SEMulator3D برای بررسی ادغام یک جایگزین SRAM (ReRAM) برای CPU برای حافظه روی تراشه استفاده کردهایم. ما از یک مدل مجازی برای درک بهتر مراحل فرآیند و مشکلات طرحبندی بالقوه سلولهای ممریستور استفاده کردیم. ما همچنین مطالعاتی را برای بررسی وضعیت تنظیم و تنظیم مجدد ممریستور و تأثیر ابعاد دستگاه (شکل و اندازه سلول حافظه) بر مقاومت خط کلمه انجام دادیم. ما تاکید کردیم که حافظه داخلی ReRAM را می توان با منطق پیشرفته با استفاده از خروجی الکتریکی ترانزیستور GAA pFET برای تنظیم و تنظیم مجدد سلول های ممریستور با منطق پیشرفته ادغام کرد. این نتایج تأیید میکند که حافظه دسترسی تصادفی مقاومتی (ReRAM) یک جایگزین امیدوارکننده برای حافظه SRAM روی برد برای کاربردهای منطقی با پهنای باند بالا در آینده است.

منابع

- لانزا، ماریو (2014). مروری بر سوئیچینگ مقاومتی در دی الکتریک های باکیفیت بالا: دیدگاهی در مقیاس نانو با استفاده از میکروسکوپ نیروی اتمی رسانا. مواد، جلد. 7، شماره 3، ص 2155-2182، doi:10.3390/ma7032155.

- ن. صدقی، و همکاران، "نقش دوپینگ نیتروژن در ALD Ta2O5 و تاثیر آن بر سوئیچینگ سلول چندسطحی در RRAM"، مارس 2017، نامه های فیزیک کاربردی، DOI:10.1063/1.4978033

- Y. Bai, et al, “Study of Multi-level Characteristics for 3D Vertical Resistive Switching Memory” گزارش های علمی جلد 4، شماره مقاله: 5780 (2014)

- Chen, YC, Sarkar, S., Gibbs, JG, Huang, Y., Lee, JC, Lin, CC, & Lin, CH (2022). "حافظه مقاومتی دو منظوره مارپیچ شکل نانو برای کاربرد آرایه میله های متقاطع کم توان."، ACS Applied Engineering Materials، 1(1)، 252-257.

- Y. Wu, et al, “Nanometer-Scale HfOx RRAM”, IEEE Electron Device Letters, Volume: 34, Issue: 8, August 2013), doi:10.1109/LED.2013.2265404

- V. Sreenivasulu، و همکاران، "تحلیل مدار و بهینه سازی FET نانوسیم GAA به سمت سوئیچینگ کم توان و بالا"، 11 نوامبر 2021، علوم کامپیوتر، doi:10.1007/s12633-022-01777-6.

برت لو

برت لو مدیر فرآیند نیمه هادی و تیم یکپارچه سازی در Coventor، یک شرکت تحقیقاتی لام است. او بیش از 35 سال در توسعه فناوری نیمه هادی کار کرده است. او کار خود را در فیلیپس Semiconductors آغاز کرد، جایی که در زمینه تولید و توسعه فرآیند به عنوان مهندس فرآیند در زمینههای فوتولیتوگرافی، اچ خشک و فرآیند مرطوب مشغول به کار شد. او سپس هشت سال را در Zilog گذراند و روی توسعه فرآیند واحد کار کرد. بعداً برت به Micron Technology پیوست و در آنجا در توسعه و ادغام فرآیند DRAM و 3D NAND کار کرد. در Coventor، تمرکز او بر حمایت از مشتریان این شرکت در مدلسازی فرآیند نیمهرسانای سهبعدی و الزامات توسعه فناوری است.

- محتوای مبتنی بر SEO و توزیع روابط عمومی. امروز تقویت شوید.

- PlatoData.Network Vertical Generative Ai. به خودت قدرت بده دسترسی به اینجا.

- PlatoAiStream. هوش وب 3 دانش تقویت شده دسترسی به اینجا.

- PlatoESG. کربن ، CleanTech، انرژی، محیط، خورشیدی، مدیریت پسماند دسترسی به اینجا.

- PlatoHealth. هوش بیوتکنولوژی و آزمایشات بالینی. دسترسی به اینجا.

- منبع: https://semiengineering.com/developing-reram-as-next-generation-on-chip-memory-for-machine-learning-image-processing-and-other-advanced-cpu-applications/

- : دارد

- :است

- :نه

- :جایی که

- 1

- 10

- 100

- 10K

- 11

- 16

- 1M

- 2013

- 2014

- 2017

- 2021

- 2022

- ٪۱۰۰

- 3d

- 400

- 7

- 75

- 8

- 8k

- a

- توانایی

- قادر

- دسترسی

- در میان

- عمل

- اضافه کردن

- اضافی

- پیشرفته

- اثر

- AI

- AL

- معرفی

- همه پست ها

- کم کردن

- اجازه دادن

- در امتداد

- همچنین

- جایگزین

- an

- تحلیل

- و

- کاربرد

- برنامه های کاربردی

- اعمال می شود

- تقریبا

- معماری

- هستند

- مناطق

- صف

- مقاله

- AS

- At

- اتمی

- اوت

- b

- پهنای باند

- BE

- بوده

- آغاز شد

- بهتر

- میان

- بیت

- سیاه پوست

- پایین

- قهوهای

- بسته

- اما

- by

- نام

- CAN

- کاریابی

- ایجاد می شود

- CD

- سلول

- سلول ها

- مرکز

- تغییر دادن

- کانال

- مشخصات

- متهم

- ترکیب

- شرکت

- شرکت

- مقایسه

- کامپیوتر

- علم کامپیوتر

- نگرانی

- هادی

- تکرار

- متصل

- تشکیل شده است

- مصرف

- اطلاعات تماس

- شامل

- ارتباط

- میتوانست

- پردازنده

- ایجاد

- ایجاد شده

- صلیب

- جاری

- در حال حاضر

- مشتریان

- تاریک

- داده ها

- تاخیر

- تاخیر

- نشان دادن

- نشان

- چگالی

- سپرده

- طرح

- طراحان

- مشخص کردن

- توسعه

- در حال توسعه

- پروژه

- دستگاه

- دستگاه ها

- تفاوت

- تفاوت

- مختلف

- ابعاد

- تشخیص دادن

- نمایش داده

- صفحه نمایش

- DOE

- اب کشیدن از

- رسم

- راندن

- خشک

- در طی

- E&T

- هر

- به آسانی

- لبه

- اثر

- هشت

- الکترونیکی

- جاسازی شده

- انرژی

- مصرف انرژی

- مهندس

- مهندسی

- تخمین زدن

- اتر (ETH)

- معاینه کردن

- اجرا شده

- تجربه

- آزمایش

- FET

- رشته

- شکل

- پر شده

- تمرکز

- برای

- استحکام

- فرم

- تشکیل

- اشکال

- یافت

- از جانب

- تابع

- آینده

- دروازه

- گیتس

- نسل

- گراف

- بیشتر

- سبز

- آیا

- he

- زیاد

- بالاتر

- برجسته

- خود را

- HTTPS

- huang

- صدها نفر

- ID

- شناسایی

- IEEE

- if

- تصویر

- in

- شامل

- افزایش

- افزایش

- نشان دادن

- فرد

- نفوذ

- داخل

- ادغام

- یکپارچه

- ادغام

- به

- بررسی

- موضوع

- ITS

- پیوست

- فرار

- زبان

- بعد

- لایه

- لایه

- طرح

- برجسته

- یادگیری

- ترک

- انسوی کشتی که از باد در پناه است

- ترک کرد

- پسندیدن

- محدود شده

- ابشار

- منطق

- کم

- دستگاه

- فراگیری ماشین

- عمده

- مدیر

- تولید

- مارس

- ماریو

- ماده

- مصالح

- حداکثر عرض

- ممکن است..

- دیدار

- حافظه

- فلز

- میکرون

- مدل

- مدل سازی

- مدرن

- بیش

- اکثر

- حرکت

- جنبش

- نیاز

- ضروری

- بعد

- نوامبر

- عدد

- of

- OHM

- on

- ONE

- فقط

- عمل

- بهینه سازی

- or

- دیگر

- تولید

- مسیر

- راه ها

- برای

- کارایی

- فیلیپس

- فیزیک

- ستون

- ستون ها

- رنگ صورتی

- قرار داده شده

- افلاطون

- هوش داده افلاطون

- PlatoData

- نقطه

- نقطه مشاهده

- ممکن

- پست ها

- پتانسیل

- قدرت

- قبلا

- مشکل

- مشکلات

- روند

- در حال پردازش

- برنامه

- برنامهریزی شده

- برنامه نويسي

- امید بخش

- ارائه

- تصادفی

- محدوده

- نسبت

- خواندن

- قرمز

- حذف شده

- گزارش ها

- نیاز

- ضروری

- مورد نیاز

- تحقیق

- مقاومت

- پاسخ

- نتایج

- این فایل نقد می نویسید:

- راست

- نقش

- s

- علم

- علمی

- بخش

- نیمه هادی

- نیمه هادی ها

- تنظیم

- تنظیمات

- شکل

- باید

- نشان داده شده

- طرف

- سیگنال

- قابل توجه

- شبیه سازی

- اندازه

- راه حل

- حل

- منبع

- صرف

- انباشته

- دولت

- ایالات

- مراحل

- ذخیره سازی

- مورد مطالعه قرار

- مطالعات

- مهاجرت تحصیلی

- چنین

- حمایت از

- تیم

- پیشرفته

- پیشرفت تکنولوژی

- نسبت به

- که

- La

- نمودار

- منبع

- دولت

- شان

- سپس

- آنجا.

- اینها

- این

- از طریق

- بدین ترتیب

- زمان

- بار

- زمان

- به

- بالا

- طرف

- به طور سنتی

- دو

- نوع

- نوعی

- زیر

- فهمیدن

- متاسفانه

- واحد

- استفاده کنید

- استفاده

- با استفاده از

- ارزشها

- مختلف

- در مقابل

- عمودی

- عمودی

- تصویری

- چشم انداز

- مجازی

- تجسم

- ولتاژ

- حجم

- vs

- بود

- we

- وب سایت

- بود

- چه زمانی

- در حین

- سفید

- به طور گسترده ای

- اراده

- با

- مشغول به کار

- کارگر

- خواهد بود

- wu

- سال

- زفیرنت