Disaineritel on RISC-V lahenduste eristamiseks palju võimalusi. Üks tee käivitub erinevate RISC-V põhikohanduste ja laienduste juurde vastavalt spetsifikatsioonile. Teine keskendub IP-plokkide valimisele ja kokkupanemisele terviklikus süsteemis kiibil (SoC) ühe või mitme RISC-V tuuma ümber. Tekkimas on kolmas: RISC-V tuumade ja muude IP-plokkide ühendamine lihtsa siinistruktuuri asemel võrgu-kiibi (NoC) abil. Ja see pole ainult tipptasemel – RISC-V tuumade sidumine NoC-dega vastab paljudele SoC-disaini väljakutsetele, kus andmed peavad mis tahes töökoormuse korral tõhusalt liikuma, kasutades mis tahes kiibisiseseid protokolle.

Jõudlustasemed muutuvad täiustatud ühendusskeemidega

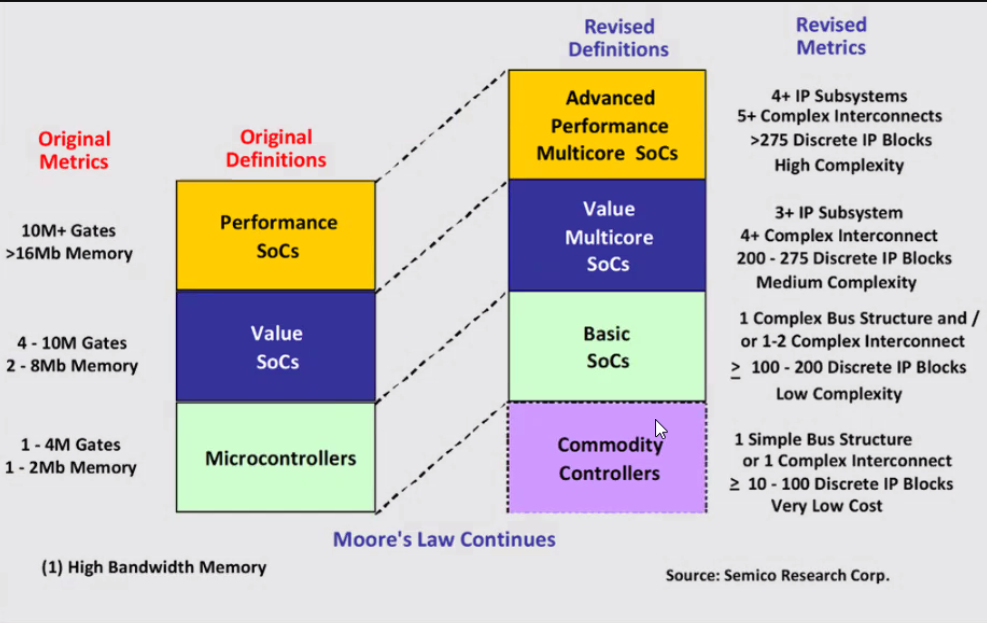

Lihtsalt väravate, tuumade ja välisseadmete plokkide loendamine ei kirjelda enam SoC-disaini jõudluspotentsiaali. Ühendusskeemid määratlevad nüüd Semico Researchi andmetel SoC jõudlustasandite vahelised jooned ja avatud on uus tasand, kus ühendused muutuvad lihtsatest siinistruktuuridest keerukamate skeemide vastu.

Semico uuendatud definitsioon tunnistab kolme töös olevat jõudu: mitmetuumaliste disainilahenduste levik, keeruliseks peetava disaini kõrgem latt ja sellele järgnev ähmane piir "mikrokontrolleri" ja "SoC" vahel. Semico uusimas vaates kaob arusaam, et värav loeb mõõdikuna, kuna üks kaasaegne protsessorituum võib palju väravaid endaga kaasa tõmmata. Keerukus muutub vastastikuste ühenduste funktsiooniks, mis varieerub sõltuvalt alamsüsteemidest ja erinevatest IP-plokkidest.

SoC jõudlustasemed, pildi lubas Semico Research Corp.

Seal, kus sobib lihtne siin, tõenäoliselt ühe protsessorituuma ja madala töötsükliga välisseadmetega osa, mis ei konkureeri pidevalt siini eest, näeb Semico kaubakontrolleri taset. Kõik, mis on üle selle, muutub SoC-ks, arvatavasti vähemalt mõne välisseadmega, mis võitleb kiibi ribalaiuse ja protsessori tuuma(de) tähelepanu eest. Kõrgematel SoC tasanditel on mitu tuuma ja mitu IP-allsüsteemi, millest igaühel on häälestatud ühendustehnoloogia.

NoC-d võtavad vastu rohkem protokolle ja alamsüsteeme

RISC-V on neid jõudlustasemeid kiiresti üles tõstnud, kuna ilmuvad võimsamad tuumad, mille rakendatavus on Semico skaala alumises otsas. RISC-V disaineritel võib aga olla vähem kogemusi kõrgemate tasandite keeruliste ühendusskeemide osas. "TileLink võib olla esimene mõte RISC-V ühendamiseks, kuid seda võib olla keeruline kasutada keerukamate stsenaariumide korral," ütleb Arteri lahenduste ja äriarenduse asepresident Frank Schirrmeister.

NoC ülivõime on selle võime ühendada alamsüsteeme erinevate protokollide abil ja SoC-disainerid kasutavad tõenäoliselt mitut isegi mõõduka keerukusega protokolli. AXI ühtlustab mänguruumi lihtsate IP-plokiühenduste jaoks. Kaastöötlusplokkidega mitmetuumalised lahendused nõuavad vahemälu sidusust, mis annab aluse CHI-protokollile. I/O-mälu jagamine aitas kujundada kiirema CXL-ühenduse. "Kui on aeg arvutusi ja transporti koos erinevate alamsüsteemide ja protokollidega optimeerida, on NoC parem lahendus," jätkab Schirrmeister.

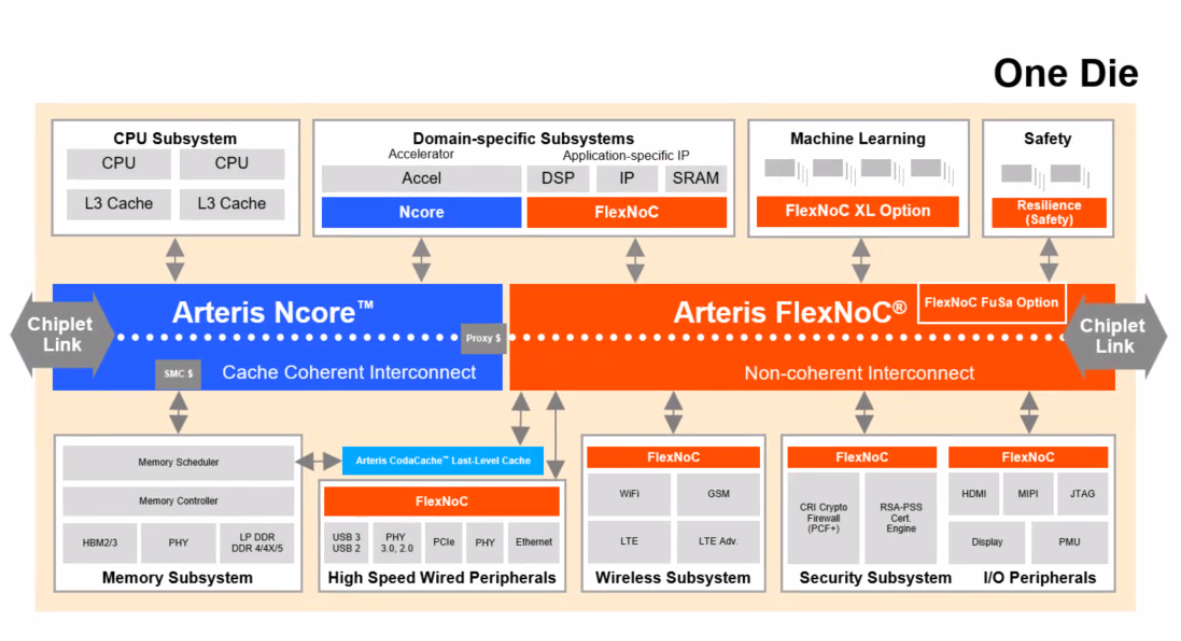

Kuidas võib RISC-V tuumade sidumine NoC-dega välja näha? Arteri klient Tenstorrent annab pilguheit võimalustele. Nende hiljutine fookus on korduvkasutatava kiibi loomisel, mis ühendab endas RISC-V tuumad, masinõppe kiirenduse IP ja standardsed välisseadmed, mida leidub paljudes AI-rakendustes. Mastaabiliselt võiks ühe stantsiga teostus välja näha nagu järgmine diagramm, kasutades Arteris Ncore vahemälu koherentset ühendust ja mitut Arteris FlexNoC mittekoherentse ühenduse segmenti.

pilt viisakalt Arteris

Nutikas mälukontroller (SMC) pakub suure jõudlusega serveritasemel mäluühendust mälumahukates rakendustes. Nimetu "kiibi link" võib olla UCIe, suhteliselt uus spetsifikatsioon, mis on optimeeritud kiibistiku tihedamaks integreerimiseks. Kui ilmnevad uued alamsüsteemi vastastikused ühendused, on NoC osa kohandamine paremini juhitav kui kogu kiibi hõlmava struktuuri ülesriputamine.

RISC-V tuumade sidumine NoC-dega vähendab riski ja turuletuleku aega

Kui see diagramm tundub keeruline ja see on tõsi, võib-olla pole enamik RISC-V rakendusi praegu nii keerulised, mõelge sellele: kiibid suurendavad integratsiooni juba palju kõrgemale. Tänane täiustatud RISC-V mitmetuumaline osa on järgmise aasta väärtus SoC, kuna innovatsioon kiireneb.

Arteris Ncore ja Arteris FlexNoC arendustööriistad väljastavad juurutamiseks RTL-i, pakkudes mitmeid eeliseid. Füüsilise NoC hindamine on EDA töövoos lihtne. NoC parameetrite reguleerimine, nagu konveieri etappide arv, on samuti mõne hiireklõpsu kaugusel EDA tööriistades. Eespool mainitud muudatused alamsüsteemi protokolli lisamiseks on samuti hõlpsasti teostatavad. "Kõige tipptasemel saavad kasutajad kohe juurdepääsu meie NoC-teadmistele, " ütleb Schirrmeister. "Madalas otsas on meie tööriistu lihtne kasutada esmakordse edu saavutamiseks ja need pakuvad kasvuteed ambitsioonikamate tulevaste keerukate ühendustega projektide jaoks."

RISC-V tuumade sidumine NoC-dega vähendab riski, et veel üks IP-plokk siseneb kujundusse ja käivitab kiibil ühenduse ümberkujundamise lainetuse. See vähendab ka keerukate SoC-disainilahenduste turuletuleku aega võrreldes isetehtavate ühendusstruktuuridega. Me ei ole siin arutanud muid NoC-de eeliseid, nagu ribalaius ja toitehaldus, kuid RISC-V disainilahenduste NoC-de juhtum on tugev, kui arvestada mitmekesist protokollikombinatsiooni.

Külastage Arteri veebisaiti NoC-de kohta lisateabe saamiseks ja muud tooted.

Jaga seda postitust:

- SEO-põhise sisu ja PR-levi. Võimenduge juba täna.

- PlatoData.Network Vertikaalne generatiivne Ai. Jõustage ennast. Juurdepääs siia.

- PlatoAiStream. Web3 luure. Täiustatud teadmised. Juurdepääs siia.

- PlatoESG. Süsinik, CleanTech, Energia, Keskkond päikeseenergia, Jäätmekäitluse. Juurdepääs siia.

- PlatoTervis. Biotehnoloogia ja kliiniliste uuringute luureandmed. Juurdepääs siia.

- Allikas: https://semiwiki.com/ip/arteris/336086-pairing-risc-v-cores-with-nocs-ties-soc-protocols-together/

- :on

- :on

- :mitte

- : kus

- $ UP

- a

- võime

- üle

- kiirendus

- juurdepääs

- saavutatud

- Vastavalt

- üle

- lisades

- kohandused

- edasijõudnud

- eelised

- AI

- juba

- Ka

- edasipüüdlik

- an

- ja

- Teine

- vastuseid

- mistahes

- midagi

- ilmuma

- rakendused

- OLEME

- ümber

- AS

- At

- tähelepanu

- ära

- Bandwidth

- baar

- BE

- muutub

- Kasu

- Parem

- vahel

- Blokeerima

- Plokid

- buss

- äri

- ettevõtluse arendamine

- kuid

- CAN

- juhul

- väljakutseid

- muutma

- muutuv

- kiip

- kombineerimine

- kaup

- võrreldes

- täitma

- keeruline

- keerukus

- Arvutama

- Võta meiega ühendust

- ühendus

- Side

- Arvestama

- kaaluda

- arvestades

- pidev

- pidevalt

- kontroller

- tuum

- Corp

- võiks

- loendamine

- loomine

- klient

- andmed

- määratlema

- määratlus

- Nõudlus

- Disain

- disainerid

- disainilahendused

- & Tarkvaraarendus

- arendusvahendeid

- erinev

- raske

- arutatud

- mitu

- do

- sõidu

- iga

- lihtne

- serv

- tõhusalt

- tekkima

- smirgel

- lõpp

- Sisse

- Kogu

- Isegi

- kogemus

- teadmised

- laiendused

- kiiremini

- vähe

- väli

- võitlemine

- esimene

- voog

- Keskenduma

- keskendub

- Järel

- eest

- relvajõud

- avastatud

- avameelne

- Alates

- funktsioon

- tulevik

- kasu

- Gates

- andmine

- Pilk

- antud

- Kasv

- Olema

- aitas

- siin

- Suur

- suur jõudlus

- rohkem

- aga

- HTTPS

- pilt

- Vahetu

- täitmine

- in

- info

- Innovatsioon

- selle asemel

- integratsioon

- omavahel ühendav

- omavahel seotud

- sisse

- IP

- IT

- ITS

- lihtsalt

- hiljemalt

- käivitab

- kõige vähem

- vähem

- nagu

- Tõenäoliselt

- joon

- liinid

- enam

- Vaata

- näeb välja

- välimus

- Madal

- vähendada

- juhtimine

- palju

- max laiuse

- mai..

- võib olla

- Mälu

- mainitud

- meetriline

- segu

- mõõduka

- Kaasaegne

- Muudatused

- rohkem

- kõige

- kolis

- palju

- mitmekordne

- peab

- Uus

- järgmine

- ei

- Mõiste

- nüüd

- number

- of

- on

- ONE

- avatud

- optimeeritud

- or

- Muu

- meie

- väljund

- tempo

- sidumine

- parameeter

- osa

- tee

- kohta

- jõudlus

- perifeerne

- välisseadmed

- füüsiline

- valima

- Huvitavat

- torujuhe

- Platon

- Platoni andmete intelligentsus

- PlatoData

- mängima

- mängimine

- võimalused

- post

- potentsiaal

- võim

- võimas

- Protsessor

- Toodet

- projektid

- protokoll

- protokollid

- anda

- annab

- pakkudes

- kiiresti

- kergesti

- hiljuti

- tunnistab

- ümber kujundada

- vähendab

- suhteliselt

- teadustöö

- korduvkasutatav

- õige

- Ripple

- Tõusma

- Oht

- jooks

- s

- ütleb

- Skaala

- stsenaariumid

- skeemid

- Osa

- nähtud

- näeb

- segmendid

- valides

- mitu

- kuju

- jagamine

- lihtne

- alates

- ühekordne

- nutikas

- lahendus

- Lahendused

- mõned

- keeruline

- täpsustus

- etappidel

- standard

- lihtne

- tugev

- struktuur

- struktuuride

- järgnev

- edu

- selline

- üliriigiks

- Tehnoloogia

- kui

- et

- .

- oma

- Need

- Kolmas

- see

- arvasin

- kolm

- rida

- Suhted

- tihedam

- aeg

- et

- tänane

- kokku

- töövahendid

- transportida

- käivitamine

- NIMETAMATA

- ajakohastatud

- kasutama

- Kasutajad

- kasutamine

- väärtus

- eri

- varieeruv

- kaudu

- vaade

- vp

- we

- veebisait

- M

- Mis on

- millal

- will

- koos

- Töö

- töövoog

- sephyrnet