Varem ma blogisin IC ja ASIC funktsionaalne kontroll, nii et täna on aeg lõpetada see FPGA funktsionaalse kontrolli olekuga. Wilson Research Group on alates 2018. aastast koostanud FPGA aruannet iga kahe aasta tagant, seega on see kolmas kord, kui nad keskenduvad sellele disainisegmendile. 5.8 miljardi dollari suurune FPGA turg on märkimisväärne ja prognooside kohaselt kasvab see 8.1. aastaks 2025 miljardi dollarini. FPGA-d said alguse 1984. aastal piiratud väravavõimsusega ja on nüüdseks kasvanud, hõlmates miljoneid väravaid, protsessoreid ja standardiseeritud andmeprotokolle.

Väikesemahulised rakendused saavad kasu FPGA-seadmete NRE-st ja insenerid saavad kiiresti oma disainilahendusi prototüüpida, kontrollides ja kinnitades neid kiiresti. FPGA-d sisaldavad nüüd protsessoreid, näiteks: Xilinx Zynq UltraSCALE, Intel Stratix, Microchip SmartFusion. Funktsionaalse kontrolli uuringus osalenud 980 osaleja hulgast on populaarseimad FPGA ja programmeeritavad SoC FPGA disainistiilid.

Kuna FPGA-de suurus on viimasel ajal suurenenud, on vigadeta tootmise võimalus langenud vaid 17% -ni, mis on veelgi hullem kui 30% IC- ja ASIC-projektidest õige esimese räni jaoks. On selge, et vajame keerukate FPGA-süsteemide paremat funktsionaalset kontrolli.

Tootmises leitud veatüübid jagunevad mitmesse kategooriasse:

- 53% – loogiline või funktsionaalne

- 31% – püsivara

- 29% – Kell

- 28% – ajastus, tee on liiga aeglane

- 21% – ajastus, tee liiga kiire

- 18% – segasignaali liides

- 9% – turvafunktsioon

- 8% – turvafunktsioon

Kui vaadata suurimat rikete, loogika või funktsionaalsuse, kategooriat, on viis algpõhjust.

FGPA projektid ei jõudnud enamasti õigeaegselt lõpule, mis on taas tingitud süsteemide suuremast suurusest, loogika keerukusest ja isegi kasutatavatest kontrollimeetoditest.

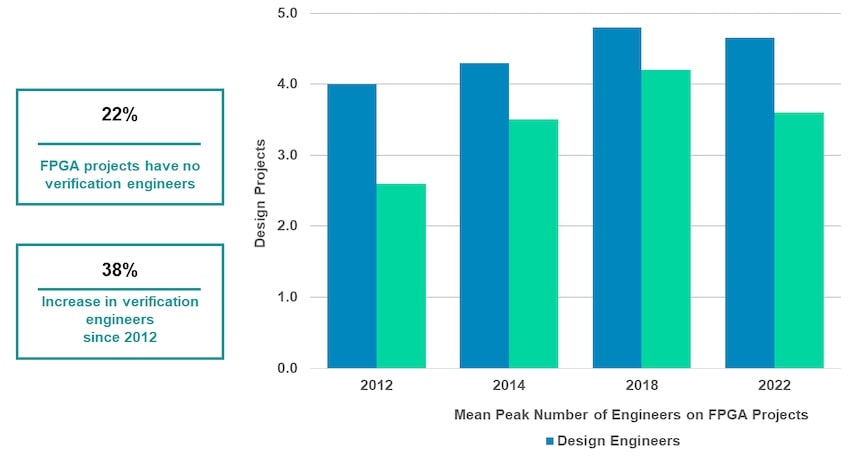

FPGA-meeskonna inseneridel võivad olla erinevad ametinimetused, nagu projekteerimisinsener või kontrolliinsener, kuid 22% projektidest puudusid kontrollimisinsenerid – see tähendab, et projekteerimisinsenerid täitsid topeltülesandeid ja kontrollisid oma IP-d. Viimase 10 aasta jooksul on FPGA projektiga seotud kontrolliinseneride arv kasvanud 38%, nii et see on edasiminek veavaba tootmise suunas.

FPGA projektide kontrolliinsenerid kulutasid suurema osa ajast silumisülesannetele 47% ulatuses:

- 47% – silumine

- 19% – Testi loomine ja simulatsiooni käivitamine

- 17% – Testbenchi arendus

- 11% – Testide planeerimine

- 6% – muu

Manustatud protsessorite arv on aja jooksul pidevalt kasvanud, nii et 65% FPGA konstruktsioonidest on praegu üks või mitu protsessorituuma, mis suurendab riistvara ja tarkvara liideste vahelise kontrollimise mahtu; ja kiibisiseste võrkude haldamine.

Üha populaarsem RISC-V protsessor on manustatud 22% FPGA-desse ja AI kiirendeid kasutatakse 23% projektides. FPGA-des kasutatakse 3–4 keskmist kella domeenide arvu ja nende kontrollimiseks on vaja väravataseme ajastussimulatsioone ning kinnitamiseks kasutada staatilisi kelladomeeni ristumisvahendeid (CDC).

Tundlike andmete hoidmiseks lisatakse 49% FPGA-projektidest turvafunktsioone, lisaks järgib 42% FPGA-projektidest ohutuskriitilisi standardeid või juhiseid. Oleme SemiWikis sageli bloginud ISO 26262 ja DO-254 standarditele. Funktsionaalse ohutuse (FuSa) projekteerimise jõupingutused võtavad 25–50% kogu projekti ajast.

Kolm parimat kinnituskeelt on VHDL, SystemVerilog ja Verilog; aga märka ka hiljutisi hüppeid Pythoni ja C/C++ keeltes.

Kõige populaarsemad FPGA metoodikad ja testbenchi baasjuhtumiteegid on: Accellera UVM, OSVVM ja UVVM. Pythonil põhinev cocotb 2022. aastaks lisati isegi uue kategooriana.

Väitekeelte eesotsas on SystemVerilog Assertions (SVA) 45%, millele järgneb Accellera Open Verification Library (OVL) 13% ja PSL 11%. FPGA-disainilahendused võivad kombineerida VHDL-i RTL-disaini jaoks koos SVA-ga väidete jaoks.

Ametlik kinnisvarakontroll FPGA projektide hulgas kasvab, eriti kuna EDA müüjad on kasutusele võtnud automaatsemad ametlikud rakendused.

Simulatsioonipõhised kontrollimeetodid viimase 10 aasta jooksul näitavad pidevat kasutuselevõttu, mis on loetletud asjakohasuse järjekorras: koodi katvus, funktsionaalne katvus, väited, piiratud juhuslikkus.

kokkuvõte

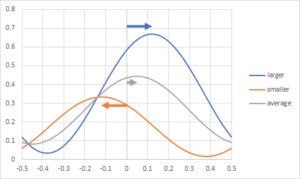

FPGA projektide madal 17% veavaba number 2022. aastal, mis jõudis tootmisse, oli minu jaoks kõige üllatavam number, kuna vaev seadme tagasikutsumise või ümberprogrammeerimise valdkonnas on kulukas ja selle parandamine aeganõudev. Tugevam funktsionaalse kontrollimise lähenemisviis peaks viima vähemate vigade põgenemiseni tootmisse ja uuringus osalejate jagamine kahte rühma näitab kasu.

Lugege täielikku 18-leheküljeline valge paber siin.

Seotud blogid

Jaga seda postitust:

- SEO-põhise sisu ja PR-levi. Võimenduge juba täna.

- Platoblockchain. Web3 metaversiooni intelligentsus. Täiustatud teadmised. Juurdepääs siia.

- Allikas: https://semiwiki.com/eda/324651-the-state-of-fpga-functional-verification/

- 1

- 10

- 2018

- 2022

- a

- MEIST

- kiirendid

- lisatud

- kinni pidama

- Vastuvõtmine

- AI

- hulgas

- summa

- ja

- rakendused

- lähenemine

- lähenemisviisid

- apps

- ASIC

- Automaatne

- keskmine

- on

- kasu

- Parem

- vahel

- Miljard

- Bug

- vead

- Võimsus

- kategooriad

- Kategooria

- Põhjus

- põhjustatud

- põhjuste

- CDC

- võimalus

- kontroll

- selgelt

- kell

- kood

- ühendama

- täitma

- keeruline

- keerukus

- katmine

- loomine

- kriitiline

- andmed

- Disain

- disainilahendused

- seade

- seadmed

- DID

- eristatav

- domeen

- Domeenid

- langes

- jõupingutusi

- jõupingutusi

- varjatud

- insener

- Inseneride

- eriti

- Isegi

- Iga

- kallis

- ebaedu

- Langema

- FUNKTSIOONID

- väli

- esimene

- keskendunud

- Järgneb

- formaalne

- avastatud

- FPGA

- Alates

- funktsionaalne

- Gates

- Grupp

- Grupi omad

- Kasvama

- Kasvavad

- kasvanud

- suunised

- riistvara

- hoidma

- HTML

- HTTPS

- in

- sisaldama

- Suurendama

- kasvanud

- kasvav

- Intel

- liidesed

- sisse

- IP

- IT

- hüppab

- Keeled

- suurem

- suurim

- viima

- Led

- raamatukogud

- Raamatukogu

- piiratud

- Loetletud

- Madal

- tehtud

- juhtiv

- Turg

- max laiuse

- tähendus

- metoodikad

- meetodid

- miljonid

- rohkem

- kõige

- Populaarseim

- Vajadus

- võrgustikud

- Uus

- number

- ONE

- avatud

- et

- üldine

- enda

- Paber

- osalejad

- minevik

- tee

- Platon

- Platoni andmete intelligentsus

- PlatoData

- pluss

- populaarne

- post

- Protsessor

- töötlejad

- Produktsioon

- Edu

- projekt

- projektid

- kinnisvara

- protokollid

- prototüüp

- Python

- kiiresti

- juhuslik

- hiljuti

- hiljuti

- vabastama

- asjakohasus

- aru

- nõudma

- teadustöö

- uurimisrühm

- jõuline

- juur

- ümber

- jooksmine

- ohutus

- turvalisus

- segment

- tundlik

- mitu

- peaks

- näitama

- Näitused

- Siemens

- Räni

- alates

- suur

- SUURUS

- So

- tarkvara

- kiirus

- kasutatud

- standardite

- alustatud

- riik

- stabiilne

- Uuring

- üllatav

- süsteemid

- Võtma

- ülesanded

- meeskond

- tehnikat

- test

- .

- Riik

- oma

- Kolmas

- kolm

- aeg

- ajastamine

- pealkirjad

- et

- täna

- liiga

- töövahendid

- ülemine

- suunas

- liigid

- kasutama

- müüjad

- Kontrollimine

- kinnitatud

- kontrollimine

- kaudu

- maht

- mis

- valge

- valge paber

- Wilson

- aastat

- sephyrnet