En la reciente Cumbre RISC-V, la última sesión fue un panel sobre chiplets llamado Chiplets en el ecosistema RISC-V. Fue moderado por Calista Redmond, directora ejecutiva de RISC-V International. Los panelistas fueron:

- Laurent Moll, director de operaciones de Arteris

- Aniket Saha, vicepresidenta de gestión de productos de Tenstorrent

- Dale Greenley, vicepresidente de ingeniería de Ventana Microsystems

- Rob Aitken, arquitecto distinguido de Synopsys

Esta es una combinación de temas un poco extraña para mí. Obviamente, se puede colocar un procesador RISC-V en un chiplet, pero los desafíos no son realmente diferentes a los de cualquier otro procesador. Pero RISC-V está de moda, al igual que los chiplets, y empresas como Ventana los están combinando.

Déjame darte un poco de información sobre las empresas para ponerlas en contexto:

- Como probablemente sepa, Arteris fabrica redes en chip (NoC). Es una empresa neutral entre los proveedores de chiplets (y proveedores de IP).

- Tenstorrent está diseñando una cartera de chips RISC-V multinúcleo de muy alto rendimiento

- Ventana tiene IP RISC-V pero también la entrega como chiplets

- Synopsys es obviamente una empresa de EDA, pero anunciaron núcleos RISC-V anteriormente en la cumbre.

]

La discusión real

La primera pregunta de Calista fue una pregunta sobre cuál era el valor de los chiplets.

Dale dijo que no había nada específico sobre RISC-V para chiplets, pero el mercado decide cuándo se hacen grandes cosas monolíticas o chiplets. Depende de lo que el cliente le pague por hacer. "Ofrecemos tanto IP como chiplets, hay espacio para ambos".

Aniket dijo que "hacer chiplets no es barato, pero hacer chiplets y RISC-V es flexible y se pueden crear nuevos productos rápidamente".

Laurent optó por los costes de producción. Es muy importante mantener NRE bajo control, ya que no hay mucha gente que esté construyendo 100 millones de piezas. Por lo tanto, hay más proveedores involucrados y una cadena de suministro complicada. Un SoC es complejo pero los chiplets son peores.

Rob señaló heterogeneidad, como agregar chiplets para RF y analógico, tener un acelerador opcional, etc. Esto potencialmente abre nuevos mercados.

Calista continuó preguntando dónde nos encontramos en el sector automotriz.

Aniket señaló que la industria automotriz es muy conservadora y ahora son agresivas con respecto a las plataformas que pueden escalar desde automóviles de gama baja hasta automóviles de gama alta. Con los chiplets, nadie ha considerado realmente la seguridad funcional.

Rob pasó al sector aeroespacial (no del todo automotriz) y analizó cómo suele haber un volumen físico fijo definido hace décadas. Es difícil encajar las cosas.

Laurent: Las empresas automotrices son los mejores compradores de catálogos y los chiplets les permiten aprovechar lo mejor en inteligencia artificial, radar, información y entretenimiento, etc.

¿Cómo se ejecuta el software?

Rob: si haces el sistema pequeño, está bien. Pero la compra por catálogo de automóviles lo hace más difícil.

Aniket: Relacionó una afirmación “si lo agregas no lo usaremos”. Las pilas de software automotriz admitirán RISC-V en 5 años, lo cual es rápido. A Arm le tomó 15 años llegar allí.

P: ¿Qué necesitamos para la conectividad?

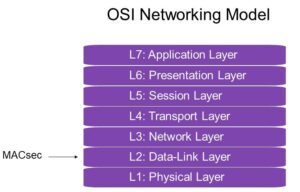

Laurent: Es muy complejo, especialmente cuando la gente compra chipsets. Los PHY de diferentes proveedores pueden ser interoperables. Todo el mundo está interesado en la UCIe. La gente quiere estándares que hagan que los chiplets se ajusten mejor.

Aniket se quejó de que no existen flujos de diseño estándar para chiplet. Una gran falta de estándares.

Rob cree que podemos crear un flujo estándar, pero con diferentes chiplets no queremos N flujos de diseño diferentes.

P: ¿Cómo ves las cosas dentro de 3 a 5 años?

Rob: estaremos más lejos con diferentes

“La compra por catálogo tal vez dependa de los fabricantes de equipos originales (OEM) de automóviles. Requerirá mucho esfuerzo de la industria. Cualquier material heterogéneo llevará más tiempo.

Aniket dijo que los chiplets estarán primero en el centro de datos y luego en el automóvil. Pero la primera ola será de un solo proveedor.

Resumen

Esta es una combinación de cosas que dijeron los participantes y mis propias opiniones.

Creo que por el momento, los diseños RISC-V basados en chiplets serán un esfuerzo de una sola empresa (excepto, quizás, para la memoria de alto ancho de banda (HBM). Es demasiado complejo construir diseños con múltiples chiplets de diferentes empresas, intercaladores. , y la red para conectarlos a todos, habitualmente conocida como RDL.

Los diseños serán 2.5D, no 3D verdadero (donde los troqueles se apilan uno encima del otro y se comunican con vías de silicio o TSV) en el futuro previsible.

La automoción tiene su propio conjunto de desafíos, en particular garantizar que los diseños basados en chiplets sean confiables en un entorno con mucha vibración. Esto requerirá pruebas exhaustivas. Otra cuestión es garantizar la seguridad funcional en un entorno con múltiples troqueles.

UCIe es prometedor y en cierta medida se basa en PCIe. Las empresas de PCIe garantizaron la confiabilidad mediante plugfests. No veo cómo se puede garantizar económicamente la interoperabilidad UCIe en chiplets mediante un mecanismo similar.

Finalmente, además de los desafíos técnicos, existen desafíos comerciales si queremos llegar al nirvana de poder comprar chips disponibles en el mercado y ensamblarlos en sistemas a un costo razonable. El mayor desafío es quién pagará y mantendrá el inventario de chiplets. Si todos los chiplets tienen que fabricarse bajo demanda, se perderán muchas de las ventajas de un tiempo de ciclo rápido.

Pero los chiplets RISC-V ciertamente están llegando rápidamente en forma de diseños de múltiples matrices en intercaladores 2.5D construidos por una sola empresa.

Lea también

Los NoC brindan a los arquitectos flexibilidad en el diseño del sistema RISC-V

Emparejar núcleos RISC-V con NoC une los protocolos SoC

Actualización #60DAC de Arteris

Comparte esta publicación a través de:

- Distribución de relaciones públicas y contenido potenciado por SEO. Consiga amplificado hoy.

- PlatoData.Network Vertical Generativo Ai. Empodérate. Accede Aquí.

- PlatoAiStream. Inteligencia Web3. Conocimiento amplificado. Accede Aquí.

- PlatoESG. Carbón, tecnología limpia, Energía, Ambiente, Solar, Gestión de residuos. Accede Aquí.

- PlatoSalud. Inteligencia en Biotecnología y Ensayos Clínicos. Accede Aquí.

- Fuente: https://semiwiki.com/ip/arteris/338888-risc-v-and-chiplets-a-panel-discussion/

- :posee

- :es

- :no

- :dónde

- $ UP

- 100 m

- 15 años

- 15%

- 167

- 200

- 300

- 3d

- a

- Poder

- Nuestra Empresa

- acelerador

- real

- add

- la adición de

- adición

- ventajas

- Aeroespacial

- agresivo

- .

- AI

- Todos

- a lo largo de

- también

- entre

- an

- y

- anunció

- Otra

- cualquier

- arquitectos

- somos

- ARM

- en torno a

- AS

- contacta

- pidiendo

- At

- automotor

- fondo

- basado

- BE

- "Ser"

- MEJOR

- mejores

- Big

- Mayor

- Poco

- ambas

- build

- Construir la

- construido

- pero

- by

- , que son

- PUEDEN

- carros

- catalogar

- ceo

- ciertamente

- cadena

- Reto

- retos

- barato

- Color

- combinación

- combinar

- cómo

- viniendo

- completo

- Comunicarse

- Empresas

- compañía

- integraciones

- Complicado

- Contacto

- Conectividad

- Conservador

- considerado

- contexto

- control

- arrullo

- Cost

- Precio

- cliente

- Cycle

- Datacenter

- décadas

- se define

- entrega

- Dependiente

- depende

- Diseño

- diseño

- diseños

- El

- una experiencia diferente

- discutido

- discusión

- Distinguido

- do

- "Hacer"

- No

- cada una

- Más temprano

- esfuerzo

- final

- Ingeniería

- garantizar

- asegurado

- asegurando que

- Entorno

- especialmente

- todos

- Excepto

- en los detalles

- RÁPIDO

- en fin

- Nombre

- cómodo

- fijas

- Flexibilidad

- flexible

- de tus señales

- Flujos

- previsible

- formulario

- Desde

- funcional

- promover

- futuras

- obtener

- Donar

- Difícil

- más fuerte

- Tienen

- es

- Alta

- Alto rendimiento

- mantener

- HOT

- Cómo

- HTTPS

- i

- if

- importante

- in

- energético

- Internacional

- Interoperabilidad

- interoperable

- dentro

- inventario

- involucra

- IP

- IT

- SUS

- jpg

- Keen

- Guardar

- Saber

- conocido

- Falta

- Apellido

- dejar

- como

- por más tiempo

- perdido

- Lote

- Baja

- para lograr

- HACE

- Management

- fabricado

- muchos

- muchas personas

- Mercado

- Industrias

- max-ancho

- Puede..

- Quizas

- me

- mecanismo

- Monolítico

- más,

- múltiples

- my

- ¿ Necesita ayuda

- del sistema,

- Neutro

- Nuevo

- no

- nada

- ahora

- of

- on

- On-Demand

- ONE

- abre

- Opiniones

- or

- Otro

- salir

- EL DESARROLLADOR

- panel

- panel de discusión

- Participantes

- particular

- partes

- Pagar

- Personas

- quizás

- los libros físicos

- Plataformas

- Platón

- Inteligencia de datos de Platón

- PlatónDatos

- portafolio

- Publicación

- la posibilidad

- probablemente

- Procesador

- Producto

- gestión de producto

- Producción

- Productos

- prometedor

- protocolos

- proporcionar

- comprar

- poner

- pregunta

- exactamente

- radar

- Leer

- realmente

- mejor

- reciente

- relacionado

- fiabilidad

- confianza

- exigir

- Conferencia

- Ejecutar

- Safety

- Said

- Escala

- ver

- Sesión

- set

- Bolsas Shopping

- Compras

- similares

- desde

- soltero

- chica

- So

- Software

- algo

- soluciones y

- apilado

- Stacks

- estándar

- estándares de salud

- Posicionamiento

- Summit

- suministro

- cadena de suministro

- SOPORTE

- te

- Todas las funciones a su disposición

- ¡Prepárate!

- hablar

- Técnico

- Pruebas

- esa

- La

- Les

- luego

- Ahí.

- ellos

- cosas

- pensar

- piensa

- así

- A través de esta formación, el personal docente y administrativo de escuelas y universidades estará preparado para manejar los recursos disponibles que derivan de la diversidad cultural de sus estudiantes. Además, un mejor y mayor entendimiento sobre estas diferencias y similitudes culturales permitirá alcanzar los objetivos de inclusión previstos.

- Corbatas

- equipo

- a

- demasiado

- se

- parte superior

- Temas

- verdadero

- superior

- bajo

- Actualizar

- utilizan el

- generalmente

- propuesta de

- vendedor

- vendedores

- muy

- vía

- volumen

- vp

- quieres

- fue

- Trenzado

- we

- fuimos

- tuvieron

- ¿

- cuando

- que

- QUIENES

- seguirá

- peor

- años

- Usted

- zephyrnet