El grabado con plasma es quizás el proceso más esencial en la fabricación de semiconductores, y posiblemente la más compleja de todas las operaciones de fabricación después de la fotolitografía. Casi la mitad de todos los pasos fabulosos se basan en un plasma, un gas ionizado energético, para hacer su trabajo.

A pesar de que las celdas de memoria y los transistores se reducen cada vez más, los ingenieros continúan brindando procesos de grabado confiables.

“Para crear chips de manera sostenible con precisión a nivel de nanoescala y la estructura de costos adecuada, los fabricantes de equipos de fabricación de obleas deben ampliar los límites de la física del plasma, la ingeniería de materiales y la ciencia de datos para brindar las soluciones de equipos necesarias”, dijo Thomas Bondur, vicepresidente corporativo de Marketing de Etch Product Group en Investigación de lam. En ninguna parte es esto más evidente que en el grabado con plasma, que funciona mano a mano con la litografía para crear características exactas y repetibles en las obleas.

Este informe examina los pasos clave del grabado en 3D NAND, DRAM, FET de nanoláminas e interconexiones, con una visión de futuro de los dispositivos 2D y el procesamiento de back-end de bajo presupuesto. La industria también está buscando químicos de grabado más sostenibles para reducir el COXNUMX equivalente.2 emisiones de sus fábricas.

Para muchos fabricantes de herramientas, el modelado de procesos juega un papel fundamental en el desarrollo del proceso de grabado. El objetivo es acortar el tiempo de comercialización al mismo tiempo que se reducen los costos de obleas y máscaras.

“La optimización del proceso de grabado en algunos de los pasos más complicados puede tardar un año o más en completarse”, dijo Barrett Finch, director sénior de marketing de Lam Research. "Recientemente completamos un trabajo de simulación de procesos en tres semanas que se esperaba que tomara tres meses utilizando pruebas y desarrollo típicos basados en silicio".

Esto puede ascender a cientos de miles, o incluso millones de dólares, solo por los costos de máscaras y obleas para un fabricante de dispositivos.

Conceptos básicos de grabado

El proceso de grabado funciona de la mano con la litografía. El grabado generalmente está precedido por la deposición de una película (por epitaxia, deposición química o física de vapor, etc.). Típicamente, un CVD la película está recubierta de fotorresistencia y luego expuesto a través de un patrón retículo (máscara) usando litografía óptica (248nm o 193nm UV, 13.5nm EUV). Resistir el desarrollo revela entonces el patrón. En una sola cámara de grabado de plasma de oblea, normalmente los productos químicos de grabado y los iones bombardean y eliminan la película de CVD donde falta la fotoprotección (en la resistencia de tono positivo). Después del grabado, elimine los residuos mediante cenizas resistentes, limpieza química húmeda y/o grabado húmedo.

Los procesos de grabado con plasma se pueden agrupar aproximadamente como grabados dieléctricos, de silicio o de conductores. Los dieléctricos como el dióxido de silicio y el nitruro de silicio se graban mejor con gases fluorados, mientras que las capas de silicio y metal reaccionan mejor con la química del cloro. Hay esencialmente tres modos de grabado en seco: grabado con iones reactivos, grabado con plasma y grabado por pulverización catódica (haz de iones). Los procesos de grabado tienen que ver con las complejas interacciones entre los reactivos químicos, el plasma y los materiales de las obleas. Cuando se aplica polarización de RF a un gas reactivo, los electrones y los iones cargados positivamente bombardean la oblea para eliminar físicamente (grabar) el material mientras que las especies químicas y los radicales libres reaccionan con el material expuesto para formar subproductos volátiles. El grabado puede ser isotrópico (reaccionando igualmente vertical y horizontalmente), anisotrópico (solo vertical) o en algún punto intermedio.

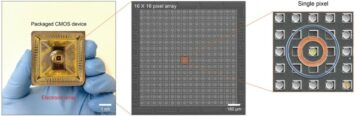

Fig. 1: La transición de finFET a GAA impulsa requisitos críticos de grabado selectivo isotrópico. Fuente: Investigación Lam

Las métricas que más preocupan a los ingenieros de grabado son la tasa de grabado, el control del perfil, la uniformidad (en toda la oblea) y la selectividad del grabado, porque afectan el rendimiento y la productividad. La selectividad de grabado es simplemente la proporción de eliminación del material que desea grabar en relación con su capa inferior, por ejemplo, SiO.2 sobre silicio. Durante el grabado, también es ventajoso no eliminar demasiado fotoprotector. Pero cuando ese es el caso, a menudo el patrón se transfiere a una máscara dura (dióxido de silicio, nitruro de silicio, SiOC, TiN) antes de transferirse a la película subyacente.

Las especificaciones de selectividad varían desde 2:1 hasta 1,000:1 (grabado altamente selectivo). Con cada nuevo nodo, estas especificaciones se vuelven más estrictas. “Con el EUV de alta NA comenzando a reemplazar el EUV regular dentro de los próximos cuatro años, el enfoque es mucho más bajo, por lo que ya no se puede exponer fotorresistente grueso, y por grueso me refiero a 30 nanómetros”, dijo Philippe Bézard, ingeniero de I + D de grabado seco en imec. “Pero aún necesita modelar el mismo grosor de película a continuación. Así que ahora está pidiendo una selectividad mucho mayor en el sentido de que en lugar de 2:1 tenemos que llegar a más de 10:1, que es una mejora repentina de selectividad de 4X a 5X”.

Desde la prueba de concepto (POC) hasta la fabricación de alto volumen (HVM)

Bézard describe tres fases del desarrollo del proceso de grabado:

- Determinar qué grabador, gases, capas auxiliares, etc., se necesitan para realizar el grabado;

- Demostrar rendimiento en la eliminación total de la película dentro de las especificaciones con uniformidad de proceso en una oblea, y

- Determinar cómo se puede repetir el proceso en miles de obleas en HVM con alto rendimiento y poca deriva.

Por lo general, los ingenieros expertos en grabado e integración se encargan de las dos primeras fases de desarrollo. La tercera fase podría volver a utilizar la experiencia en ingeniería, pero el aprendizaje automático podría ayudar.

“El aprendizaje automático y el análisis de datos en general solo son útiles en la tercera fase”, dijo. “Es muy poderoso porque tiene acceso a una tonelada de datos y puede dar sentido a un millón de cosas pequeñas y simples que interactúan. Entonces, para un cerebro humano tratar de resolver esto es muy difícil, pero es más manejable para un programa de computadora. Pero en los casos en los que tiene una nueva aplicación, un nuevo material grabado o una nueva integración, no muestra ninguna mejora con respecto a los humanos”.

El uso de ML también se relaciona con el costo de fabricación porque se usan miles de obleas en la fase tres, al menos un orden de magnitud mayor que las que se usan en las fases uno y dos.

Barrett Finch, director sénior del grupo de productos Etch en Lam Research, describe la búsqueda de nuevos procesos como tomar una prueba de concepto de un diseño y flujo de proceso nominal y desarrollar uno o más dispositivos de trabajo en una oblea. Este POC luego se transfiere a un equipo de desarrollo de productos en la fábrica para ampliar el proceso y mejorar el rendimiento.

“La cantidad de trabajo requerida para transformar una prueba de concepto nominal en un producto rentable y viable a menudo se subestima, y esto crea una gran brecha en la rentabilidad”, dijo Finch. “El modelado de la ventana de proceso busca cerrar esta brecha al introducir una variación fabulosa en las primeras etapas de la búsqueda de caminos de I+D”. Sugiere que los DOE virtuales y el análisis basado en Monte Carlo a través de una serie de parámetros de proceso prueban un POC simulando la variabilidad esperada.

“El modelado de ventana de proceso puede responder a la pregunta: '¿Qué CD o nivel de variabilidad debo mantener para alcanzar el rendimiento y rendimiento mínimos del dispositivo?' Hemos completado pruebas de ventana de proceso virtual con más de 1 millón de obleas virtuales en unos pocos días, lo que sería imposible de lograr en la vida real”, dijo.

Múltiples parámetros afectan la tasa de grabado, el perfil y la selectividad. Una clave es la temperatura. “Nuestros clientes ven el impacto de los efectos térmicos en el procesamiento de grabado mientras controlan las tasas de grabado, las selectividades y los perfiles grabados. Todos estos parámetros pueden afectar tanto el rendimiento del dispositivo como la productividad de la fábrica”, dijo Benjamin Vincent, gerente sénior de ingeniería de integración y procesos de semiconductores en Lam Research. Sostiene que la simulación puede ser especialmente útil cuando un paso del proceso tiene varias configuraciones posibles (el espacio del proceso es grande) o cuando los resultados posteriores del paso son muy impredecibles.

“El proceso de grabado se basa en la temperatura de la superficie de la oblea, que depende de varios flujos de calor, incluida la conducción térmica, las energías de impacto de iones, las reacciones superficiales y los flujos de calor radiativo del plasma”, dijo Alex Guermouche, gerente de marketing de productos de Esgee Technologies, una Compañía de Investigación Lam. “Como resultado, los modelos de plasma deben incorporar todas estas características físicas para representar con precisión los cambios de temperatura en la superficie de la oblea. El software de simulación de procesos puede modelar una variedad de atributos de grabado, lo que nos permite obtener un mejor resultado de grabado más rápido y acelerar la capacidad del cliente para aumentar la producción u optimizar el rendimiento”.

Momento preciso del proceso de grabado

Con geometrías más ajustadas y películas más delgadas, existe la necesidad de equilibrar la tasa de grabado con un gran control sobre otros parámetros operativos.

“Con reglas de diseño cada vez más reducidas, muchos procesos de grabado se están moviendo hacia pasos de proceso de grabado con plasma muy rápidos que requieren un control muy preciso de todas las entradas de la reacción: potencia, presión, química y temperatura”, dijo Finch, señalando que también hay una tendencia hacia el plasma optimizado. comportamiento pulsante para generar una relación ion-neutro particular, luego barrer los subproductos. "El modelado avanzado de tales condiciones será fundamental para permitir una mayor escala de dispositivos".

Los fabricantes de sistemas de grabado han estado utilizando software de modelado durante algún tiempo para acelerar el desarrollo del siguiente nodo o aumentar los rendimientos. Esto no es una sorpresa, dada la gran complejidad del proceso y todas sus variables.

“Simplemente no hay suficiente tiempo o suficientes obleas para ejecutar todos los experimentos de procesos posibles al desarrollar tecnologías de próximo nodo”, dijo Finch. “La cantidad de combinaciones de configuración de equipos de grabado puede llegar a millones, o incluso miles de millones, y el desarrollo de obleas de fuerza bruta utilizando todas las posibilidades del proceso es simplemente imposible”.

Por supuesto, todos los buenos modelos se verifican en chips reales. “Un modelo preciso debe ser predictivo y debe resolver el problema específico que un usuario quiere resolver”, dijo Finch. “Cada vez que se recomienda un cambio de proceso o diseño en base al trabajo de simulación, los datos reales de la fábrica deben reflejar los resultados de la recomendación. En nuestro caso, hemos podido predecir con precisión el efecto de los cambios en el proceso utilizando resultados basados en modelos y resolver rápidamente problemas difíciles de desarrollo de tecnología y procesos”.

Los proveedores de herramientas también están trabajando en procesos de grabado avanzados para integrar más estrechamente las líneas y transformar lo que alguna vez fue un proceso de nivel de dos máscaras (dos pasos de litografía) en uno para la simplificación del proceso y la reducción de costos.

“En lugar de adaptar el hardware existente para hacer que la navaja suiza esté aún más equipada, las empresas están introduciendo tecnologías que son específicas de la aplicación, como nuevos sistemas para abordar problemas de punta a punta”, dijo Bézard. El objetivo es acercar dos líneas enfrentadas, lo que actualmente implica un paso de patrón de líneas seguido de una máscara de corte. “Lo que Applied Materials y otros están introduciendo es una forma de grabar directamente en dirección horizontal”. Dichos procesos también pueden ensancharse a través de agujeros.

Pasos de grabado para FET de nanoláminas

Los pasos de grabado más críticos en nanohoja los flujos del proceso incluyen el ataque químico de la puerta ficticia, el ataque químico del pilar anisotrópico, el ataque químico del espaciador isotrópico y el paso de liberación del canal. [1] El grabado del perfil a través de capas alternas de silicio y SiGe es anisotrópico y utiliza química fluorada. El grabado del espaciador interno (indentación) y el paso de liberación del canal están optimizados para eliminar SiGe con una pérdida de silicio extremadamente baja.

El paso de liberación del canal es crítico. “El lanzamiento de la nanolámina exige una selectividad extremadamente alta”, dijo Bézard. “La mayoría de las nanoláminas son de silicio, luego de silicio-germanio y silicio. Tiene capas alternas y necesita eliminar una sin modificar la otra en absoluto”. Algunas publicaciones han discutido la realización de un grabado SiGe de varios pasos para reducir la tensión en la estructura inducida por un solo paso de grabado.

Lo siguiente en el proceso es la formación de contactos autoalineados. “Aquí, lo que estamos tratando de hacer es básicamente grabar dióxido de silicio y no tocar ni rebajar el nitruro de silicio. Las especificaciones actuales son, digamos, 3nm de rebaje, pero la gente pide cero pérdidas”, dijo Bézard. “En este caso ni siquiera estamos usando la palabra selectividad. Solo hablamos sobre el recreo, y cero recreo en eso”.

3D NAND

3D NAND flash, la cantidad de capas continúa creciendo y requiere la adopción de múltiples niveles apilados en el futuro, lo que eventualmente creará cadenas verticales de dispositivos apilados. “Además, existe un gran impulso para escalar el paso de línea de palabra o el paso vertical/Z de las capas a medida que crece el número de capas para continuar aumentando la densidad de bits”, dijo Robert Clark, miembro sénior del personal técnico y director de tecnología en TEL. “Desde la perspectiva del proceso, los procesos de grabado y deposición necesitarán una mejora constante para adaptarse a las relaciones de aspecto cada vez más altas en dimensiones críticas cada vez más pequeñas que requiere el escalado continuo”.

Clark describió los cambios futuros. “Mirando hacia los nodos avanzados de dispositivos de trampa de carga con múltiples niveles, se requerirá la ingeniería de las pilas de puertas para lograr longitudes de puerta más cortas, más niveles por celda y una eficiencia de programación mejorada, potencialmente a través de la adopción de materiales de alta k. Es probable que también se requieran canales de mayor conductividad para reemplazar los canales de poli-Si en el futuro”, dijo.

Uno de los grabados más críticos en 3D NAND implica el grabado profundo de orificios de aproximadamente 100 nm a través de pilas de óxido-nitruro multicapa (más de 200 capas), que pueden tener una profundidad de hasta 10 µm. Bézard de Imec dijo que este paso de grabado es particularmente costoso.

“Tenemos un fenómeno físico que ocurre, llamado efecto de carga diferencial”, dijo. “En el plasma tenemos electrones, iones y especies neutras para simplificar mucho. Los electrones se mueven en todas las direcciones, pero los iones se aceleran perpendicularmente a la superficie. Entonces tienes una carga positiva en el fondo del agujero y cargas negativas en la parte superior, y obtienes un campo eléctrico que intenta repeler los iones entrantes”.

Como resultado, se necesitan altos niveles de potencia para grabar completamente la zanja. “Estamos tratando de mantener de 30 a 50 gigavatios de potencia sin arco eléctrico, por lo que el mandril debe estar extremadamente bien pulido y bien fabricado”, dijo.

Los grabados profundos también inducen tensiones que deben minimizarse, especialmente porque la fabricación NAND de varios niveles requiere posteriormente adelgazamiento de la oblea, alineación precisa y unión híbrida al siguiente nivel.

Otros procesos

No todos los fabricantes de chips producen chips de vanguardia que requieren litografía EUV. Muchas fábricas están ampliando sus procesos de grabado y litografía de 193 nm.

"Tenemos un material SOC de alta temperatura que comenzamos a presentar recientemente, que amplía su capacidad de creación de patrones y puede soportar temperaturas más altas, ya sea que se use como capa base para una capa o máscara de CVD", dijo Brian Wilbur, director de diversificación de productos semiconductores en Ciencia cervecera.

beol para las líneas de metal más estrechas se espera que experimenten una transición dramática de los esquemas de integración de damasquinado dual a la deposición sustractiva y grabado de interconexión que no sea cobre. Aquí, dos metales, el rutenio y el molibdeno, han sido los más desarrollados. Sin embargo, es más probable que el molibdeno se oxide durante el grabado, lo que lo hace más compatible con los esquemas de damasquinado dual. El rutenio es un metal noble por lo que no tiene los mismos problemas de corrosión, pero es más costoso.

Las estructuras de los dispositivos también se están volviendo intolerantes con errores de colocación de bordes. Se necesitarán nuevos esquemas para la autoalineación de capa a capa y entre vías y líneas, según Clark de TEL. "Es probable que las primeras implementaciones sean para cosas como líneas de palabras enterradas en DRAM y las capas de metal MOL de paso pequeño para la lógica donde se necesita una mayor estabilidad térmica, así como una menor resistividad o metales sin revestimiento".

Desarrollos de última generación

A largo plazo, la industria idealmente hará la transición a procesos de back-end de menor presupuesto térmico (más cerca de 300 °C que de 400 °C) para integrar dispositivos en capas de interconexión de back-end.

“La industria tiene una necesidad real de comenzar a construir dispositivos en más capas”, dijo Clark de TEL. “Eso significa que necesitamos memoria y dispositivos lógicos construidos dentro de los presupuestos térmicos de BEOL en BEOL”.

Hasta ahora, los dispositivos fabricados con óxidos semiconductores parecen prometedores, tanto para integrar dispositivos de memoria en un flujo BEOL lógico como para construir matrices CMOS sobre la matriz de memoria en DRAM.

Otro cambio sustancial implica la integración de materiales 2D, que las casas de investigación y los principales fabricantes de chips ya están comenzando a probar. Se están considerando procesos de grabado para materiales como el disulfuro de tungsteno o el disulfuro de molibdeno. Las películas consisten en una monocapa de material, por lo que desarrollar procesos de fabricación para integrarlas es extremadamente desafiante.

Sostenibilidad

Los fabricantes de chips y los proveedores de materiales buscan químicas alternativas para reducir las emisiones de carbono. En el grabado, los principales culpables son los gases fluorados con un alto potencial de calentamiento global.

“Una de las razones por las que se tiene PFOS (ácido sulfónico de perfluorooctano), que es problemático, es porque la molécula es muy estable”, dijo Bézard de imec. “La luz o las reacciones químicas en la atmósfera no son suficientes para descomponerla”.

Dijo que varias mezclas de gases alternativos con mayor contenido de oxígeno se disocian más fácilmente y tienen un GWP más bajo. “Sin embargo, cualquier candidato tiene que ofrecer un desempeño tan bueno o incluso superior para comenzar”.

Pero la sustentabilidad no es particularmente un desafío de grabado o deposición. Es un desafío industrial holístico desde la litografía hasta el empaque, donde el impacto de un nuevo material influye en todo el procesamiento del dispositivo.

Referencia

1. K. Derbyshire, "Qué hay de diferente en los transistores de próxima generación", Ingeniería de Semiconductores, 20 de octubre de 2022.

Historias relacionadas

Se lanza grabado altamente selectivo para chips de próxima generación

La fabricación de estructuras 3D requerirá un control a nivel atómico de lo que se elimina y lo que permanece en una oblea.

- Distribución de relaciones públicas y contenido potenciado por SEO. Consiga amplificado hoy.

- PlatoAiStream. Inteligencia de datos Web3. Conocimiento amplificado. Accede Aquí.

- Acuñando el futuro con Adryenn Ashley. Accede Aquí.

- Compra y Vende Acciones en Empresas PRE-IPO con PREIPO®. Accede Aquí.

- Fuente: https://semiengineering.com/etch-processes-push-toward-higher-selectivity-cost-control/

- :posee

- :es

- :no

- :dónde

- $ UP

- 000

- 1

- 10

- 13

- 20

- 2022

- 2D

- Materiales 2D

- 30

- 3d

- 50

- a

- capacidad

- Poder

- Acerca

- acelerar

- acelerado

- de la máquina

- acomodar

- lograr

- Conforme

- preciso

- precisamente

- a través de

- real

- dirección

- Adopción

- avanzado

- ventajoso

- afectar

- de nuevo

- objetivo

- alex

- Todos

- Permitir

- ya haya utilizado

- también

- alternativa

- cantidad

- an

- análisis

- y

- Otra

- https://www.youtube.com/watch?v=xB-eutXNUMXJtA&feature=youtu.be

- cualquier

- Aparecer

- Aplicación

- aplicación específica

- aplicada

- somos

- Ejército

- Formación

- AS

- aspecto

- ayudar

- At

- Atmósfera

- atributos

- lejos

- Back-end

- Balance

- basado

- Básicamente

- BE

- Manga

- porque

- cada vez

- esto

- antes

- Comienzo

- "Ser"

- a continuación

- Benjamin

- MEJOR

- mejores

- entre

- parcialidad

- Big

- miles de millones

- Poco

- ambas

- Fondo

- límites

- Cerebro

- Descanso

- Brian

- la fuerza bruta

- presupuesto

- Presupuestos

- Construir la

- construido

- pero

- by

- , que son

- PUEDEN

- candidato

- carbono

- las emisiones de carbono

- servicios sociales

- case

- cases

- CD

- Células

- Reto

- desafiante

- Cámara

- el cambio

- Cambios

- Channel

- canales

- CHARGE

- cargado

- cargos

- cargando

- químico

- productos químicos

- química

- Papas fritas

- Limpieza

- Cerrar

- de cerca

- más cerca

- combinaciones

- Empresas

- compañía

- compatible

- completar

- Completado

- integraciones

- complejidad

- computadora

- concepto

- condiciones

- conductividad

- conductor

- considerado

- constante

- contactos

- contenido

- continue

- continuado

- continúa

- control

- Cobre

- Sector empresarial

- corrosión

- Cost

- y reducción del coste

- Precio

- podría

- curso

- Para crear

- crea

- Creamos

- crítico

- Current

- En la actualidad

- Clientes

- Corte

- datos

- análisis de los datos

- Ciencia de los datos

- Días

- profundo

- entregamos

- densidad

- depende

- descrito

- Diseño

- desarrollado

- el desarrollo

- Desarrollo

- dispositivo

- Dispositivos

- una experiencia diferente

- difícil

- dimensiones

- dirección

- directamente

- Director

- discutido

- diversificación

- do

- sí

- dólares

- DE INSCRIPCIÓN

- verdadero

- el lado de la transmisión

- secas

- durante

- cada una

- Temprano en la

- pasan fácilmente

- efecto

- los efectos

- eficiencia

- ya sea

- Los

- electrones

- emisiones

- permitiendo

- ingeniero

- Ingeniería

- certificados

- suficientes

- igualmente

- equipo

- equipado

- Equivalente a

- especialmente

- esencial

- esencialmente

- etc.

- Incluso

- finalmente

- Cada

- exigente

- Examina

- ejecutar

- existente

- esperado

- costoso

- experimentos

- Experiencia

- expuesto

- extensión

- extremadamente

- tener problemas con

- muchos

- RÁPIDO

- más rápida

- Caracteristicas

- pocos

- campo

- Figura

- Film

- films

- Nombre

- Flash

- de tus señales

- Flujos

- Focus

- seguido

- siguiendo

- FORCE

- formulario

- formación

- adelante

- Digital XNUMXk

- Gratuito

- en

- completamente

- promover

- futuras

- brecha

- GAS

- General

- generar

- obtener

- dado

- Buscar

- el calentamiento global

- objetivo

- candidato

- maravillosa

- Grupo procesos

- Crecer

- crece

- A Mitad

- encargarse de

- Difícil

- Materiales

- Tienen

- he

- serviciales

- esta página

- Alta

- Alto Rendimiento

- más alto

- altamente

- Agujero

- Agujeros

- holístico

- Horizontal

- casas

- Cómo

- Sin embargo

- HTTPS

- humana

- Humanos

- Cientos

- Híbrido

- i

- Impacto

- imposible

- mejorar

- mejorado

- es la mejora continua

- in

- incluir

- Incluye

- Entrante

- incorporar

- creciente

- energético

- entradas

- ejemplo

- integrar

- Integración

- integración

- interactuando

- interacciones

- interconecta

- dentro

- Presentamos

- cuestiones

- IT

- SUS

- jpg

- solo

- Clave

- Lam

- large

- mayores

- .

- ponedoras

- Disposición

- líder

- aprendizaje

- menos

- Nivel

- Vida

- como

- que otros

- línea

- líneas

- LITO

- pequeño

- lógica

- por más tiempo

- Mira

- de

- Lote

- Baja

- máquina

- máquina de aprendizaje

- hecho

- Inicio

- mantener

- para lograr

- Makers

- Realizar

- gerente

- fabricado

- Fabricante

- Fabricación

- muchos

- Mercado

- Marketing

- Director de Marketing

- máscara

- materiales

- materiales

- max-ancho

- Puede..

- personalizado

- significa

- miembro

- Salud Cerebral

- metal

- Metales

- Métrica

- podría

- millones

- millones

- mínimo

- que falta

- modelo

- modelado

- modelos

- los modos

- MOL

- molécula

- meses

- más,

- MEJOR DE TU

- movimiento

- emocionante

- mucho más

- múltiples

- hace casi

- ¿ Necesita ayuda

- negativas

- Neutro

- Nuevo

- Next

- no

- Noble

- nodo

- nodos

- ahora

- número

- octubre

- of

- a menudo

- on

- una vez

- ONE

- , solamente

- funcionamiento

- Operaciones

- optimización

- Optimización

- optimizado

- or

- solicite

- Otro

- Otros

- nuestros

- salir

- Más de

- Oxígeno

- embalaje

- parámetros

- particular

- particularmente

- Patrón de Costura

- Personas

- realizar

- actuación

- realizar

- quizás

- la perspectiva

- fase

- un fenómeno mundial

- Philippe

- los libros físicos

- Físicamente

- Física

- Pillar

- Paso

- esencial

- Plasma

- Platón

- Inteligencia de datos de Platón

- PlatónDatos

- juega

- PoC

- positivo

- POSIBILIDADES

- posible

- posiblemente

- posible

- la posibilidad

- industria

- poderoso

- necesidad

- Precisión

- predecir

- presidente

- presión

- Problema

- problemas

- en costes

- tratamiento

- producir

- Producto

- desarrollo de productos

- Producción

- productividad

- Productos

- Mi Perfil

- Perfiles

- rentabilidad

- Programa

- Programación

- prometedor

- prueba

- prueba de concepto

- publicaciones

- Push

- pregunta

- con rapidez

- I + D

- Rampa

- distancia

- Rate

- Tarifas

- proporción

- en comunicarse

- Reaccionar

- reacción

- reacciones

- real

- vida real

- razón

- recientemente

- Recomendación

- recomendado

- reducir

- la reducción de

- reducción

- reflejar

- regular

- ,

- confianza

- confiar

- eliminación

- remove

- Remoto

- la eliminación de

- repetible

- repetido

- reemplazar

- reporte

- exigir

- Requisitos

- Requisitos

- requiere

- la investigación

- resultado

- Resultados

- Revela

- Derecho

- ROBERT

- Función

- rollos

- aproximadamente

- reglas

- Ejecutar

- Said

- mismo

- dices

- Escala

- la ampliación

- esquemas

- Ciencia:

- Busca

- visto

- selectivo

- semiconductor

- mayor

- sentido

- pólipo

- Varios

- Turno

- tienes

- Silicio

- sencillos

- simplificar

- simplemente

- simulación

- soltero

- experto

- chica

- So

- Software

- Soluciones

- RESOLVER

- algo

- en alguna parte

- Fuente

- Espacio

- soluciones y

- Especificaciones

- especificaciones

- velocidad

- Estabilidad

- estable

- apilado

- Stacks

- Staff

- etapas

- comienzo

- fundó

- paso

- pasos

- Sin embargo

- estrés

- estructura

- Después

- sustancial

- tal

- repentino

- suficiente

- Sugiere

- proveedores

- Superficie

- sorpresa

- Sostenibilidad

- sostenible,

- Sweep

- suizo

- Todas las funciones a su disposición

- ¡Prepárate!

- toma

- escuchar

- afectados

- equipo

- Técnico

- Tecnologías

- Tecnología

- Desarrollo tecnológico

- término

- test

- Pruebas

- pruebas

- que

- esa

- El

- El futuro de las

- su

- Les

- luego

- Ahí.

- térmico

- Estas

- ellos

- cosas

- Código

- así

- a fondo

- miles

- Tres

- A través de esta formación, el personal docente y administrativo de escuelas y universidades estará preparado para manejar los recursos disponibles que derivan de la diversidad cultural de sus estudiantes. Además, un mejor y mayor entendimiento sobre estas diferencias y similitudes culturales permitirá alcanzar los objetivos de inclusión previstos.

- nivel

- más apretado

- equipo

- sincronización

- a

- juntos

- tonelada

- TONO

- demasiado

- parte superior

- contacto

- hacia

- transferido

- Transformar

- transición

- Tendencia

- try

- dos

- principiante

- típicamente

- subyacente

- imprevisible

- a

- hacia arriba

- us

- utilizan el

- usado

- Usuario

- usando

- utilizar

- verificadas

- vertical

- verticalmente

- muy

- vía

- y

- Vice Presidenta

- Vicente

- Virtual

- volátiles

- quieres

- quiere

- fue

- Camino..

- we

- Semanas

- WELL

- ¿

- cuando

- sean

- que

- mientras

- todo

- porque

- seguirá

- dentro de

- sin

- Palabra

- Actividades:

- trabajando

- funciona

- se

- año

- años

- Rendimiento

- flexible

- los rendimientos

- Usted

- zephyrnet

- cero