El estrés térmico es un problema bien conocido en el envasado avanzado, junto con los desafíos del estrés mecánico. Ambos se ven exacerbados por la integración heterogénea, que a menudo requiere mezclar materiales con coeficientes de expansión térmica (CTE) incompatibles.

Los efectos ya están apareciendo y es probable que solo empeoren a medida que las densidades de los paquetes aumenten más allá de los 1,000 golpes por chip.

“Combinas metales que tienen un CTE relativamente alto, luego tienes polímeros que tienen una rigidez CTE aún mayor y luego tienes dieléctricos que tienen un CTE extremadamente bajo. Una vez que pones todo junto, el estrés es inevitable”, dijo Mario González, director científico y gerente de I + D para modelado y caracterización mecánica y térmica en imec.

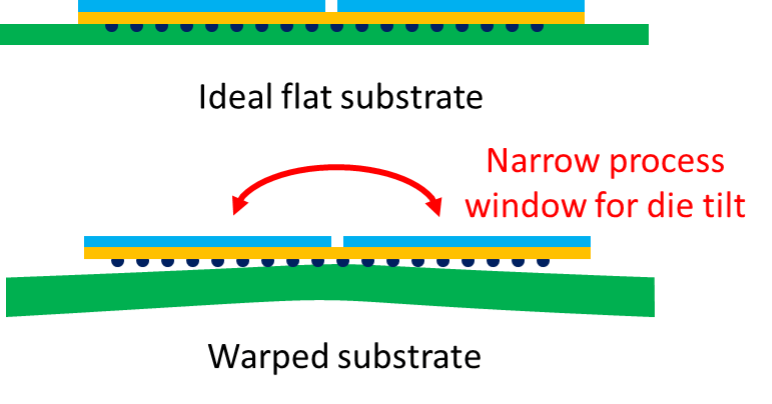

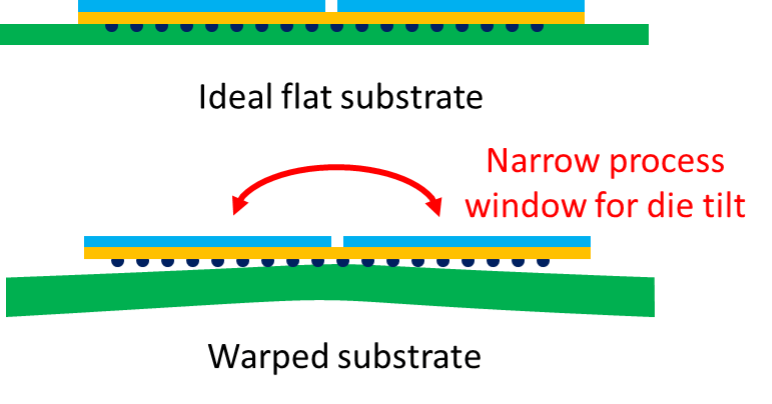

Tal tensión a menudo da como resultado una deformación significativa o la inclinación del dado, lo que a su vez conduce a condiciones que disminuyen la confiabilidad. “Estás tratando con diferentes tecnologías de sustrato con varias capas”, dijo Chip Greely, vicepresidente de ingeniería de Industrias Promex. “Los diferentes espesores de núcleo en los sustratos, en particular, comienzan a crear muchos de los problemas mecánicos clásicos, incluida la deformación, que se ha convertido en un punto crítico para algunos de los jugadores más grandes. Estamos pidiendo a muchos de nuestros clientes que tienen un módulo de varios chips de integración heterogénea de sistema en paquete que proporcionen los datos de muaré de sombra de sus sustratos para que podamos ver la forma en que su deformación cambia con la temperatura de reflujo e idealmente encontrar su punto de reflexión.”

Esta cepa tiene varios efectos negativos, experimentados en muchas escalas dimensionales, según Gilad Barak, vicepresidente de nuevas tecnologías avanzadas de Nova. “A menudo, la flexión y torsión de las características a nivel de nanoestructura es el resultado del estrés incorporado que se ha creado, como se encuentra en algunas DRAM y nanohojas lógicas de front-end”, dijo. “Otro ejemplo se relaciona con áreas a escala micrométrica donde la tensión inducida impide la fabricación de estructuras de semiconductores de alta gama, como es típico en las 'zonas de exclusión' alrededor de las vías de silicio (TSV). Finalmente, los impactos a gran escala de la tensión inducida pueden hacer que la oblea se arquee, lo que complica significativamente el manejo y la fabricación de la oblea, lo que corre el riesgo de fracturar la propia oblea. El arqueamiento de la oblea se ve particularmente durante la deposición de capas dieléctricas gruesas, como es común durante la fabricación de dispositivos 3D NAND”.

La buena noticia es que la industria es muy consciente de estos y otros problemas asociados. La mala noticia es que aún le faltan soluciones, aunque actualmente se están explorando muchos enfoques.

“Existen varias metodologías para reducir la deformación, pero ninguna de ellas es completamente exitosa, y siempre vienen con compensaciones”, dijo Frank Chen, director de aplicaciones y administración de productos en Bruker Nano Superficies y Metrología. “Los problemas no están aislados en una selección limitada de aplicaciones. Cada vez que coloque un troquel en otro sustrato, tendrá estos problemas”.

Todo esto significa que la inspección y la metrología deben seguir desempeñando papeles críticos. Otros problemas, como los puntos calientes, también pueden exacerbarse cuando se combinan múltiples chips en paquetes heterogéneos.

“Durante la prueba, varios chips se calentarán en diferentes momentos y temperaturas, creando posibles puntos calientes que deben enfriarse adecuadamente”, dijo Andrei Berar, director senior de Test Business Development en Amkor. “Además de crear controladores térmicos activos específicos, que coincidan con el área de diferentes chips, existen esfuerzos significativos para desarrollar controladores térmicos adaptativos que puedan 'anticipar' los puntos calientes en función de los vectores proporcionados por el programa de prueba”.

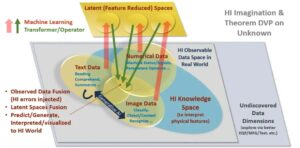

Estas combinaciones también están dando lugar a un uso cada vez mayor de la metrología híbrida, que combina diferentes técnicas para llegar a la raíz de los problemas con mayor rapidez.

Diseño, inspección, soluciones de prueba.

De hecho, la interacción clásica entre el diseño, la inspección y la tensión termomecánica se ha vuelto más compleja con miles de conexiones cada vez más pequeñas y frágiles.

Un resultado es un énfasis renovado en el cambio a la izquierda, con la esperanza de "diseñar" los problemas de CTE y los consiguientes efectos en cascada que pueden provocar sobrecalentamiento y estrés mecánico. Y para aumentar las posibilidades de prevenir, además de encontrar defectos críticos, se necesitan tanto la simulación como la inspección, según Andras Vass-Varnai, ejecutivo de desarrollo de cartera del segmento de Industria de Electrónica y Semiconductores de Software de Siemens Digital Industries.

“La cosimulación térmica y estructural utilizando dinámica de flujo computacional (CFD), modelado de elementos finitos (FEA), etc., en la etapa inicial de diseño del paquete ayuda a comprender el rendimiento esperado del ensamblaje y también permite una buena base para ' Optimización impulsada por IA, ya que muchas de las opciones de diseño se pueden parametrizar”, explicó Vass-Varnai. “Una vez que se construye el primer prototipo, las pruebas de transitorios térmicos pueden ayudar a mapear el rendimiento térmico del componente. Si hay una discrepancia entre el comportamiento térmico esperado y el real, los datos de prueba se pueden usar para 'calibrar' las propiedades del material del gemelo digital del paquete y actualizar las bibliotecas de materiales para una mayor precisión inicial de los próximos diseños”.

Encontrar la mejor manera de probar matrices de impacto y diseñar para la prueba es un desafío cada vez mayor. “¿Qué pasa si hay una señal que sube y baja?” preguntó Rob Aitken, un Sinopsis compañero. “Eso crea un problema de prueba, porque ahora tienes una señal que no va a ninguna parte y otra señal que viene de la nada, y tienes que averiguar cómo vas a probar esas cosas. ¿Los sondeas? Pero en ese caso, hay dimensiones físicas que debe mantener, y luego corre el riesgo de sufrir daños mecánicos. ¿O encuentra algún tipo de estructura similar a JTAG? Pero eso luego reduce la eficiencia de estos puntos de conexión. Estamos en la gran fase de experimentación en la que todos dicen: 'Tal vez esto funcione, tal vez eso funcione'. En este momento, no necesariamente querría apostar por lo que es 'eso'”.

Hay opciones de prueba indirectas y directas para la investigación de defectos, según JCET. Por ejemplo, CSAM (tomografía acústica de barrido computarizado) y rayos X 3D son indirectos, mientras que el análisis transversal mecánico es una herramienta para la prueba directa. JCET también cuenta con equipos avanzados de caracterización térmica para caracterizar los problemas de material/estructura resultantes de defectos mecánicos.

La inspección óptica es, como siempre, el enfoque más rápido para la inspección en línea, pero la mejor práctica es un enfoque híbrido. “El mejor método para detectar cortocircuitos/aperturas y defectos marginales sería SPI (inspección de pasta de soldadura) a AOI (inspección óptica automatizada) de reflujo previo a AOI de reflujo posterior a rayos X en línea”, aconsejó Timothy Skunes, vicepresidente de investigación. y desarrollo en Nordson Test & Inspection's ciberóptica cartera.

Además, otras modalidades pueden ser útiles, especialmente en nodos avanzados. Por ejemplo, un enfoque reciente para caracterizar la deformación en dispositivos semiconductores es la espectroscopia Raman (RS). "RS es muy aplicable para las mediciones en la estructura, ofrece mediciones rápidas del orden de segundos y pequeños tamaños de punto de unas pocas micras para permitir mediciones detalladas", dijo Barak de Nova. "La dificultad de medir directamente la tensión en las estructuras antes de la introducción de la espectroscopia Raman como herramientas de metrología en línea en la fábrica llevó a realizar pruebas en etapas mucho más avanzadas del proceso de fabricación".

En última instancia, para una inspección minuciosa, no hay atajos. Los cálculos de presupuesto pueden requerir métricas comparativas, como el costo inicial de un nuevo instrumento frente al costo continuo de RMA excesivos. Y hay una cosa más a considerar: cómo asegurarse de que puede confiar en sus datos.

“¿Va a desechar lo que probablemente era un buen material para asegurarse de no tener ningún material problemático en lo que pasa al usuario final? ¿Quién va a asumir el costo de eso? advirtió Mike McIntyre, director de gestión de productos de software en Sobre la innovación, quien recomienda una base de datos estadística para una evaluación comparativa precisa al realizar una clasificación automatizada de defectos.

Warpage

Uno de los peores resultados del estrés es la deformación. Puede ser sorprendente que la deformación sea difícil de detectar, pero el efecto no siempre es tan obvio como parece. La deformación provoca ligeras diferencias en la coplanaridad entre el chip y el sustrato, lo que provoca que algunos microprotuberancias no se conecten lo suficiente con las almohadillas de abajo, una falla denominada no húmeda.

“Considere un procesador avanzado de 50 a 60 mm, como ejemplo”, dijo Chen. “Debido a su gran tamaño, es un desafío procesarlo sin deformaciones. No obstante, si la herramienta de fijación de matriz se ajusta en el centro de su ventana de proceso, puede pasar la inspección y fabricarse con altos rendimientos. El problema es que la tolerancia puede ser muy estrecha. Tan pronto como tenga un poco de inclinación del dado encima de la deformación, tendrá problemas no húmedos”.

Peor aún, si esto está ocurriendo en pasos de relieve en el rango de 50 µm (tamaño de relieve de ̴35 µm), imagine los problemas a medida que las dimensiones del relieve se reducen aún más. Ya es una preocupación para la industria automotriz, ya que avanza hacia su próxima generación en 2023 o 2024. La transición crítica será alrededor del nodo de 28 nm, dijo Chen.

Fig. 1 Las herramientas de fijación de troquel tienen una ventana de proceso muy estrecha para la inclinación del troquel cuando hay deformación. Fuente: Bruker

no mojado

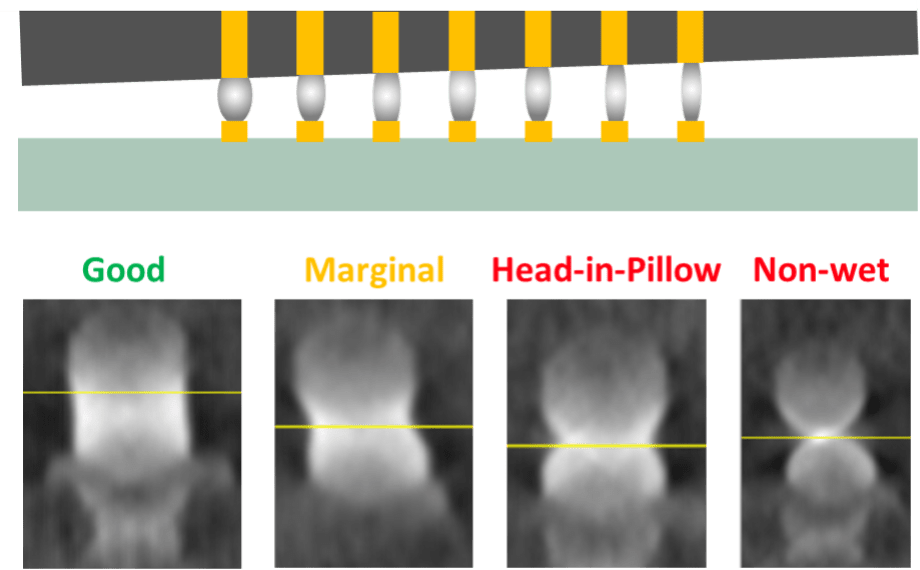

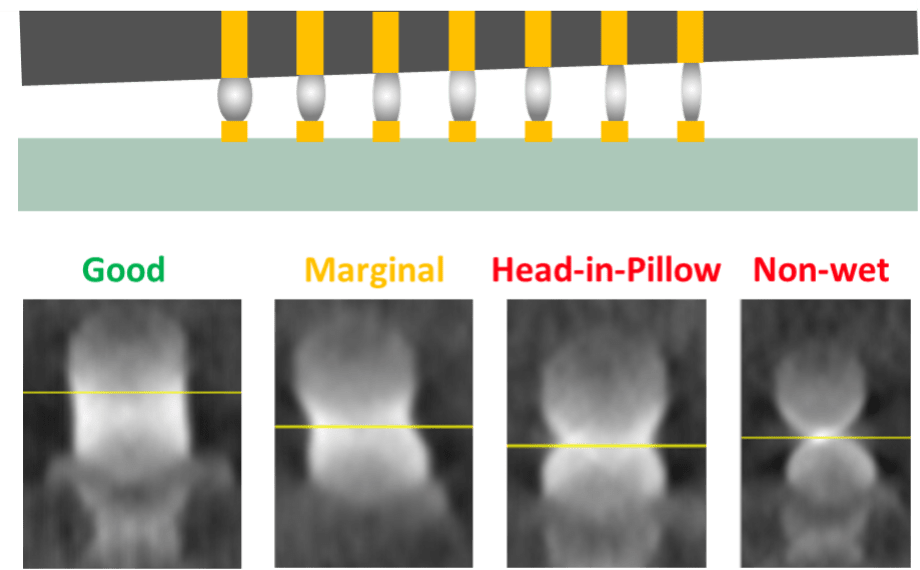

"No húmedo" es un término amplio que cubre varios problemas que pueden ocurrir con los golpes de soldadura, la mayoría de los cuales son frustrantemente sutiles. Debido a que la soldadura suele estar en estado líquido, el proceso de aplicación se denomina "humectación". Los enlaces tenues se denominan "no húmedos", y se están convirtiendo en un desafío mayor en los nodos más pequeños con conexiones más delgadas.

Los no húmedos a menudo escapan a los procesos de selección típicos, solo para aparecer más tarde como chips devueltos (RMA). Las causas fundamentales pueden ser térmicas, mecánicas o una combinación, como los ciclos térmicos en un automóvil que también circula por un terreno accidentado. El efecto acumulativo puede proporcionar suficiente tensión termomecánica para romper el contacto.

Hay apodos adicionales que describen tipos específicos de problemas. En lugar de la forma suave y columnar de una buena conexión, en un defecto de "cabeza en almohada", una bola parece hundirse en la otra, como una cabeza en una almohada.

“Todavía está haciendo contacto, por lo que la prueba eléctrica puede ser buena, pero se puede ver que es muy frágil”, dijo Chen, señalando la radiografía de una cabeza en la almohada. “Tan pronto como tenga algún estrés térmico o estrés mecánico, podría romperse por completo. Incluso si es un contacto no húmedo, la conexión delgada conduce a un rendimiento subóptimo de alta resistencia y probablemente no durará mucho. Un no húmedo abierto no funcionará en absoluto. En un escenario típico con la inclinación del troquel, hay una transición visible de protuberancias bien formadas a no mojadas”.

El problema crítico son los defectos latentes: conexiones que son lo suficientemente funcionales para pasar la prueba eléctrica pero fallan en el campo.

Fig. 2 Transición gradual de buenos baches a no húmedos en presencia de inclinación del troquel. Fuente: Bruker

“Es un gran problema en este momento con muchos tipos de dispositivos debido a los efectos del estrés térmico”, dijo Chen. “Un cliente tenía un producto que pasó la prueba electrónica y fue enviado. Desafortunadamente, tenían muchos RMA debido a fallas no húmedas que se desarrollaron después”.

Algunas empresas están abordando esto a través de inspecciones manuales dolorosamente tediosas. Desafortunadamente, cualquier examen humano está sujeto a la fatiga del operador, especialmente cuando los examinadores intentan detectar errores sutiles durante un turno de varias horas.

En el lado positivo, ahora existen enfoques automatizados para la inspección, como herramientas de rayos X que se pueden usar en línea. “Hay un gran impulso hacia la inspección totalmente automatizada y de alta velocidad para lograr <100 dppb, especialmente para la industria automotriz”, dijo Chen.

Se vuelve más complicado a partir de ahí. “En particular, la soldadura, la culpable de muchos no húmedos, también está sujeta a la electromigración”, dijo Tom Marinis, miembro principal del personal técnico de laboratorio de Draper. “Si la densidad de corriente en una conexión entre un chip y el sustrato es demasiado alta para una soldadura en particular durante un período de tiempo, debido a que la temperatura de fusión de la soldadura puede ser relativamente baja en comparación con la temperatura de funcionamiento del dispositivo, puede obtener migración de los átomos y en realidad forman vacíos y eventualmente abren una conexión”.

Marinis advirtió que las herramientas comerciales de modelado a nivel de dispositivo-PCB no son lo suficientemente maduras como para alertar constantemente sobre posibles problemas de electromigración, por lo que es importante realizar una prueba de envejecimiento acelerado.

Conclusión

En última instancia, la detección de problemas de confiabilidad a partir de defectos latentes requerirá una metrología de muestreo más alta que sea sensible al cambio de matriz, la rotación, la altura, la inclinación y otros parámetros. También requerirá una mayor confianza en el modelado multifísico para tratar de anticipar y resolver problemas potenciales antes de la producción. Y a medida que las industrias automotriz y de semiconductores continúan entremezclándose, hay mucho más en juego que solo las RMA.

“El costo de las fallas crece exponencialmente a medida que los defectos latentes pasan de los dispositivos a los módulos y luego a los automóviles que podrían poner en peligro la vida de las personas”, dijo Chen. Esta es la razón por la que los fabricantes de chips están creando soluciones holísticas que combinan diseño, inspección y pruebas para detectar mejor las fallas latentes.

- Distribución de relaciones públicas y contenido potenciado por SEO. Consiga amplificado hoy.

- Platoblockchain. Inteligencia del Metaverso Web3. Conocimiento amplificado. Accede Aquí.

- Fuente: https://semiengineering.com/bump-reliability-is-challenged-by-latent-defects/

- 000

- 1

- 2023

- 2024

- 3d

- a

- acelerado

- Conforme

- la exactitud

- preciso

- Lograr

- lector activo

- adición

- Adicionales

- direccionamiento

- avanzado

- Aging

- Alertar

- Todos

- permite

- ya haya utilizado

- Aunque

- hacerlo

- análisis

- y

- Otra

- anticiparse a

- aplicable

- aplicaciones

- La aplicación de

- enfoque

- enfoques

- Reservada

- áreas

- en torno a

- Asamblea

- evaluación

- asociado

- adjuntar

- Confirmación de Viaje

- automotor

- industria del automóvil

- Malo

- pelota

- basado

- base

- Tenga

- porque

- a las que has recomendado

- cada vez

- antes

- detrás de

- "Ser"

- a continuación

- MEJOR

- Bet

- mejores

- entre

- Más allá de

- Big

- más grande

- Poco

- Descanso

- general

- presupuesto

- construido

- incorporado

- desarrollo de negocios

- , que son

- Puede conseguir

- de

- carros

- case

- lucha

- Causar

- causas

- causando

- Reubicación

- CFD

- Reto

- Desafiado

- retos

- desafiante

- posibilidades

- Cambios

- caracterizar

- chen

- chip

- Papas fritas

- opciones

- clásico

- clasificación

- combinación

- combinaciones

- combinar

- combinado

- combinar

- cómo

- completo

- Algunos

- Empresas

- en comparación con

- completamente

- integraciones

- Complicado

- componente

- Protocolo de Tratamiento

- condiciones

- Conectarse

- conexión

- Conexiones

- Considerar

- contacte

- continue

- Core

- esquinas

- Cost

- podría

- cubierta

- Para crear

- creado

- crea

- Creamos

- crítico

- Current

- En la actualidad

- cliente

- Clientes

- corte

- datos

- Base de datos

- tratar

- densidad

- describir

- Diseño

- diseños

- detallado

- desarrollar

- desarrollado

- Desarrollo

- dispositivo

- Dispositivos

- El

- diferencias

- una experiencia diferente

- Dificultad

- digital

- gemelo digital

- dimensiones

- de reservas

- directamente

- Director

- "Hacer"

- No

- DE INSCRIPCIÓN

- pañero

- conductor

- doblado

- durante

- dinámica

- Temprano en la

- efecto

- los efectos

- eficiencia

- esfuerzos

- Electrónica

- énfasis

- Ingeniería

- suficientes

- garantizar

- equipo

- Errores

- especialmente

- etc.

- Éter (ETH)

- Incluso

- finalmente

- todo

- ejemplo

- ejecutivos

- expansión

- esperado

- experimentado

- explicado

- explorado

- exponencialmente

- extremadamente

- FALLO

- Fracaso

- más rápido

- fatiga

- Caracteristicas

- Compañero

- pocos

- campo

- Higo

- Figura

- Finalmente

- Encuentre

- la búsqueda de

- Nombre

- de tus señales

- formulario

- encontrado

- en

- frustrantemente

- funcional

- promover

- generación de AHSS

- obtener

- Va

- va

- candidato

- gradual

- Creciendo

- crece

- Manejo

- Difícil

- cabeza

- altura

- ayuda

- ayuda

- Alta

- más alto

- altamente

- holístico

- Con optimismo

- HOT

- Cómo

- Como Hacer

- HTTPS

- humana

- Híbrido

- Impactos

- importante

- in

- Incluye

- aumente

- creciente

- industrias

- energético

- inicial

- instrumento

- integración

- Introducción

- investigación

- aislado

- cuestiones

- IT

- sí mismo

- Tipo

- laboratorio

- large

- Gran escala

- mayores

- Apellido

- .

- ponedoras

- Lead

- líder

- Prospectos

- LED

- Nivel

- bibliotecas

- que otros

- enlaces

- Líquido

- Vidas

- Largo

- Lote

- Baja

- mantener

- para lograr

- Realizar

- Management

- gerente

- manual

- fabricado

- muchos

- mapa

- Mario

- pareo

- materiales

- materiales

- un estudiante adulto

- max-ancho

- significa

- medidas

- medición

- mecánico

- miembro

- Metales

- Método

- metodologías

- Métrica

- Metrología

- podría

- migración

- mezclándose

- modelado

- módulo

- Módulos

- más,

- MEJOR DE TU

- se mueve

- múltiples

- nano

- necesariamente

- negativas

- sin embargo

- Nuevo

- Nuevas tecnologías

- noticias

- Next

- nodo

- nodos

- obvio

- que ofrece

- ONE

- en marcha

- habiertos

- funcionamiento

- operador

- optimización

- Opciones

- solicite

- Otro

- paquete

- paquetes

- embalaje

- Dolor

- parámetros

- particular

- particularmente

- pasado

- de las personas

- realizar

- actuación

- período

- fase

- los libros físicos

- lanzamientos

- Platón

- Inteligencia de datos de Platón

- PlatónDatos

- Jugar

- players

- punto

- puntos

- polímeros

- portafolio

- positivo

- posible

- posible

- presencia

- presidente

- la prevención

- Director de la escuela

- Anterior

- probablemente

- sonda

- Problema

- problemas

- en costes

- Procesador

- Producto

- gestión de producto

- Producción

- Programa

- prueba

- correctamente

- propiedades

- prototipo

- proporcionar

- previsto

- poner

- I + D

- distancia

- rápido

- real

- reciente

- de CFP.

- reducir

- reduce

- reflexión

- relativamente

- fiabilidad

- dependencia

- renovado

- exigir

- requiere

- la investigación

- la investigación y el desarrollo

- resultado

- resultante

- Resultados

- Riesgo

- riesgos

- También soy miembro del cuerpo docente de World Extreme Medicine (WEM) y embajadora europea de igualdad para The Transformational Travel Council (TTC). En mi tiempo libre, soy una incansable aventurera, escaladora, patrona de día, buceadora y defensora de la igualdad de género en el deporte y la aventura. En XNUMX, fundé Almas Libres, una ONG nacida para involucrar, educar y empoderar a mujeres y niñas a través del deporte urbano, la cultura y la tecnología.

- raíz

- Ejecutar

- Said

- dice

- escamas

- exploración

- guión

- proyección

- segundos

- parece

- segmento

- selección

- semiconductor

- mayor

- sensible

- Varios

- Shadow

- Forma

- Turno

- CAMBIANDO

- transportado

- En Corto

- Mostrar

- Signal

- importante

- significativamente

- simulación

- Tamaño

- tamaños

- chica

- menores

- So

- Software

- Soluciones

- algo

- Pronto

- Fuente

- soluciones y

- Espectroscopia

- Spot

- Staff

- Etapa

- etapas

- stake

- comienzo

- Estado

- estadístico

- Sin embargo

- estrés

- estructural

- estructura

- sujeto

- exitosos

- tal

- sorprendente

- Técnico

- técnicas

- Tecnologías

- test

- Pruebas

- El

- El Área

- su

- Ahí.

- térmico

- cosa

- cosas

- miles

- A través de esta formación, el personal docente y administrativo de escuelas y universidades estará preparado para manejar los recursos disponibles que derivan de la diversidad cultural de sus estudiantes. Además, un mejor y mayor entendimiento sobre estas diferencias y similitudes culturales permitirá alcanzar los objetivos de inclusión previstos.

- Lanzamiento

- equipo

- veces

- a

- juntos

- tolerancia

- demasiado

- del IRS

- parte superior

- hacia

- transición

- Confía en

- GIRO

- tipos

- principiante

- entender

- próximos

- Actualizar

- utilizan el

- Usuario

- diversos

- Vasto

- Vice Presidenta

- visibles

- bien conocido

- ¿

- que

- mientras

- QUIENES

- seguirá

- sin

- Actividades:

- Peor

- se

- de rayos X

- los rendimientos

- tú

- zephyrnet