Investigadores de la Universidad de Lund publicaron un artículo técnico titulado “Memristores de unión de túnel ferroeléctrico para aceleradores de computación en memoria”.

Abstracto:

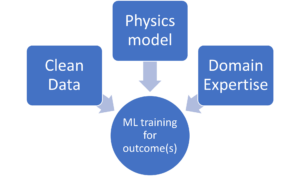

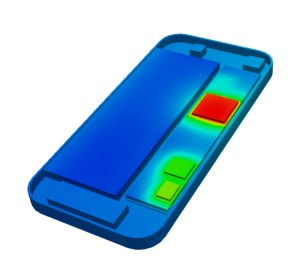

“La computación neuromórfica ha despertado un gran interés a medida que los avances en las aplicaciones de inteligencia artificial (IA) han expuesto limitaciones debido al gran acceso a la memoria, con la arquitectura informática de von Neumann. La computación paralela en memoria proporcionada por la computación neuromórfica tiene el potencial de mejorar significativamente la latencia y el consumo de energía. La clave del hardware de computación neuromórfica analógica son los memristores, que proporcionan niveles de conductancia multiestado no volátiles, alta velocidad de conmutación y eficiencia energética. Los memristores de unión de túnel ferroeléctrico (FTJ) son los principales candidatos para este propósito, pero el impacto de las características particulares de su rendimiento al integrarse en grandes conjuntos de barras transversales, el elemento informático central tanto para la inferencia como para el entrenamiento en redes neuronales profundas, requiere una investigación minuciosa. En este trabajo, un W/Hf x Zr1-x O2/TiN FTJ con 60 estados de conductancia programables, un rango dinámico (DR) de hasta 10, densidad de corriente >3 A m-2 at V leer = 0.3 V y corriente-voltaje altamente no lineal (I-V) características (>1100) se demuestran experimentalmente. Utilizando un macromodelo de circuito, se evalúa el rendimiento a nivel del sistema de una matriz de barras transversales verdadera y se logra una precisión de clasificación del 92 % del conjunto de datos del Instituto Nacional Modificado de Ciencia y Tecnología (MNIST). Finalmente, la baja conductancia en combinación con la alta no linealidad I-V Las características permiten la realización de grandes conjuntos de barras transversales sin selectores para aceleradores de hardware neuromórficos”.

Encuentra los documento técnico aquí. Publicado en diciembre de 2023.

Athle, R. y Borg, M. (2023), Memristores de unión de túnel ferroeléctrico para aceleradores informáticos en memoria. Adv. Intel. Sistema. 2300554. https://doi.org/10.1002/aisy.202300554

Lectura relacionada

Aumento de la eficiencia energética de la IA con computación en memoria

Cómo procesar cargas de trabajo en escala zetta y mantenerse dentro de un presupuesto de energía fijo.

Modelado de computación en memoria con eficiencia biológica

La IA generativa obliga a los fabricantes de chips a utilizar los recursos informáticos de forma más inteligente.

- Distribución de relaciones públicas y contenido potenciado por SEO. Consiga amplificado hoy.

- PlatoData.Network Vertical Generativo Ai. Empodérate. Accede Aquí.

- PlatoAiStream. Inteligencia Web3. Conocimiento amplificado. Accede Aquí.

- PlatoESG. Carbón, tecnología limpia, Energía, Ambiente, Solar, Gestión de residuos. Accede Aquí.

- PlatoSalud. Inteligencia en Biotecnología y Ensayos Clínicos. Accede Aquí.

- Fuente: https://semiengineering.com/ferroelectric-tunnel-junctions-in-crossbar-array-analog-in-memory-compute-accelerators/

- :posee

- :es

- $ UP

- 10

- 1100

- 2023

- 60

- a

- aceleradores

- de la máquina

- la exactitud

- alcanzado

- AI

- y

- aplicaciones

- arquitectura

- somos

- Formación

- artificial

- inteligencia artificial

- Inteligencia Artificial (AI)

- AS

- At

- ambas

- presupuesto

- pero

- by

- candidatos

- características

- clasificación

- Cerrar

- combinación

- Calcular

- informática

- consumo

- Core

- Current

- Diciembre

- profundo

- redes neuronales profundas

- demostrado

- densidad

- digital

- dr

- dos

- lugar de trabajo dinámico

- eficiencia

- elementos

- habilitar

- energía

- eficiencia energética

- evaluado

- expuesto

- Finalmente

- fijas

- Fuerzas

- maravillosa

- Materiales

- Tienen

- pesado

- esta página

- Alta

- altamente

- HTTPS

- identificador

- Impacto

- mejorar

- in

- Innovadora

- integración

- Intelligence

- intereses

- dentro

- investigación

- Clave

- large

- Estado latente

- saltos

- Nivel

- limitaciones

- Baja

- Salud Cerebral

- modificado

- más,

- UR DONATIONS

- telecomunicaciones

- Neural

- redes neuronales

- Nuevo

- objeto

- of

- on

- habiertos

- Papel

- Paralelo

- particular

- actuación

- Platón

- Inteligencia de datos de Platón

- PlatónDatos

- posible

- industria

- Prime

- programable

- previsto

- proporcionando

- publicado

- propósito

- R

- distancia

- realización

- requiere

- investigadores

- Recursos

- Ciencia:

- Ciencia y Tecnología

- visto

- significativamente

- velocidad

- Zonas

- quedarse

- te

- Técnico

- Tecnología

- La

- su

- así

- titulada

- a

- Formación

- verdadero

- túnel

- universidad

- a

- utilizan el

- usando

- de

- fue

- dentro de

- Actividades:

- zephyrnet