Una búsqueda rápida en Google de “CI 2.5D 3D” devuelve 669,000 2.5 resultados, por lo que es un tema popular para la industria de los semiconductores, y hay muchas decisiones que tomar, como si usar un sustrato orgánico o un intercalador de silicio para la interconexión de matrices de semiconductores heterogéneos. Los equipos de diseño que utilizan técnicas 3D y XNUMXD pronto se dan cuenta de que hay muchos formatos de datos a considerar:

- GDS - diseño de chiplet

- LEF/DEF: formato de intercambio de biblioteca, formato de intercambio de diseño

- Excel – mapa de bolas

- Verilog: diseño lógico

- ODB++ - Paquete BGA

- CSV: valor separado por comas

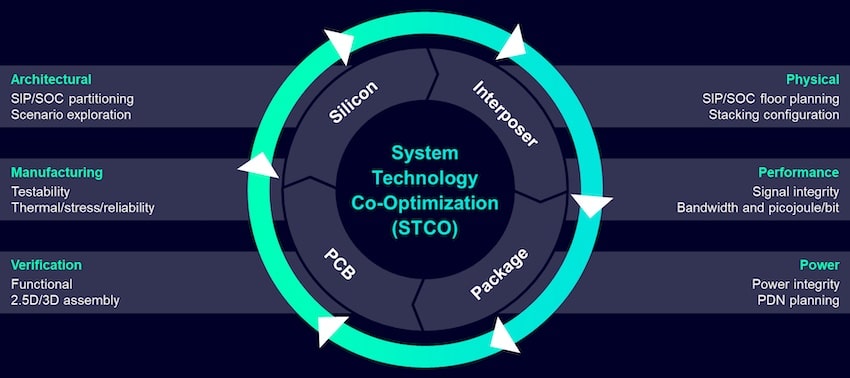

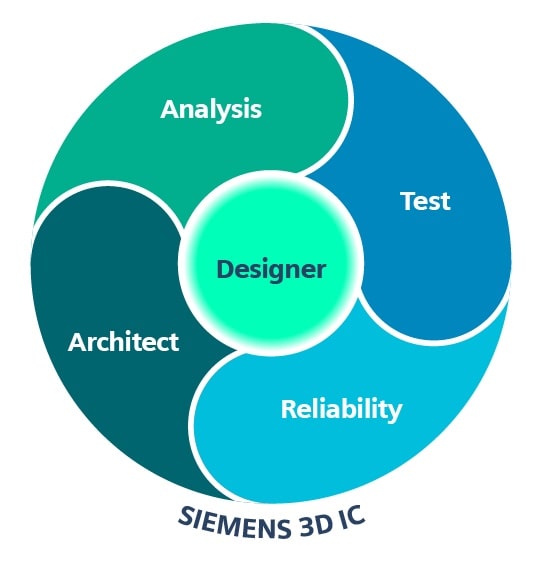

Un libro electrónico de Siemens proporciona una orientación muy necesaria sobre los desafíos de administrar la conectividad en los múltiples formatos de datos. Los datos de origen se importan a su herramienta de administración de conectividad, y luego cada herramienta de implementación recibe los datos correctos para analizar térmica, SI (Integridad de la señal), PI (Integridad de la energía), caída de IR, LVS a nivel del sistema y verificación de ensamblaje.

Para mantener la coherencia, su equipo de diseño debe usar una fuente única de verdad, de modo que cuando se realice un cambio de diseño, se actualice el sistema completo y cada herramienta de implementación tenga los datos de entrada más recientes. El flujo de trabajo de Siemens se mantiene sincronizado a través del enfoque LVS a nivel de sistema.

No existe un formato de archivo estándar entre los equipos de paquete, interposición y placa; sin embargo, al usar ODB ++, puede llevar datos de paquete y PCB a la herramienta de planificación, lo que permite que su equipo se comunique y optimice usando cualquier herramienta EDA. Un diseñador de paquetes puede mover las protuberancias y luego el equipo de silicio puede revisar los cambios usando archivos DEF para aceptarlos.

El sistema más grande en diseños de paquetes puede tener un millón de pines en total, por lo que sus herramientas deben manejar esa capacidad. El rendimiento en un sustrato depende de la ubicación precisa de las vías, los arreglos de vías y las áreas metálicas. Su herramienta de diseño de sustrato o intercalador debe administrar las interfaces correctamente y asegurarse de obtener el kit de diseño de ensamblaje de fundición o OSAT para obtener resultados óptimos.

Desde la herramienta de Siemens, tiene una cabina de planificación para crear gráfica y rápidamente un prototipo virtual del ensamblaje completo del paquete 2.5/3D, también conocido como gemelo digital. Esta metodología hace posible la Co-Optimización de Tecnología de Sistemas (STCO). Hacer concesiones tempranas entre la arquitectura y la tecnología produce los mejores resultados para un nuevo sistema, mediante el uso de análisis predictivo para clasificar todos los diferentes escenarios de diseño. El análisis predictivo valida que los nombres netos sean consistentes entre el troquel, el intercalador y el paquete, evitando así cortos y abiertos.

El sistema LVS garantiza que todos los dominios de diseño estén limpios de DRC y LVS, validando las conexiones en las protuberancias del paquete, el intercalador y la matriz.

Se requiere verificación física durante muchos pasos:

- Muere nivel DRC y LVS

- interpuesto

- Paquete

- Todos los niveles juntos

La herramienta de planificación de Siemens hace todo esto, mientras mantiene el diseño del sistema correcto de principio a fin, eliminando sorpresas tardías. También es necesario realizar una verificación de equivalencia entre la herramienta de planificación y el diseño final.

Usando una metodología de gemelo digital, su equipo ahora puede verificar que el sistema de paquetes sea correcto. Los primeros errores se detectan rápidamente a través de la verificación, como "alfileres hacia arriba, alfileres hacia abajo", a través de una verificación de superposiciones entre el paquete, el silicio y el intercalador. También se verificará la consistencia de las ubicaciones de los baches entre el paquete y los equipos de CI. Las comprobaciones se pueden ejecutar después de cada cambio o actualización, solo para asegurarse de que no haya sorpresas.

Resumen

Los equipos interrelacionados de IC, paquete y placa ahora pueden trabajar juntos utilizando un enfoque de gemelo digital, como lo ofrece Siemens. No muchos proveedores de EDA tienen los años de experiencia en flujos de herramientas para estas tres áreas, además, puede agregar muchas de sus herramientas EDA de punto favoritas. La colaboración y la optimización son posibles para los desafíos de las interconexiones 2.5D/3D.

Lea el artículo completo libro electrónico de 14 páginas de Siemens.

Blogs relacionados

Comparte esta publicación a través de:

- Distribución de relaciones públicas y contenido potenciado por SEO. Consiga amplificado hoy.

- Platoblockchain. Inteligencia del Metaverso Web3. Conocimiento amplificado. Accede Aquí.

- Fuente: https://semiwiki.com/eda/323664-interconnect-choices-for-2-5d-and-3d-ic-designs/

- 000

- 3d

- a

- Aceptar

- preciso

- a través de

- Después

- Todos

- Permitir

- análisis

- el análisis de

- y

- enfoque

- arquitectura

- áreas

- en torno a

- Asamblea

- evitar

- pelota

- MEJOR

- entre

- tablero

- Capacidad

- capturado

- retos

- el cambio

- Cambios

- comprobar

- comprobación

- Cheques

- opciones

- Puente de mando

- colaboración

- Comunicarse

- completar

- Conexiones

- Conectividad

- Considerar

- consistente

- Para crear

- datos

- decisiones

- depende

- Diseño

- Designer

- diseños

- El

- una experiencia diferente

- digital

- gemelo digital

- dominios

- Soltar

- durante

- cada una

- Temprano en la

- eliminando

- garantizar

- asegura

- Cada

- Intercambio

- experience

- Favoritos

- Archive

- archivos

- final

- acabado

- de tus señales

- Flujos

- formato

- Fundición

- Desde

- ser completados

- obtener

- Búsqueda de Google

- encargarse de

- HTTPS

- implementación

- in

- energético

- Las opciones de entrada

- integridad

- las interfaces

- acuerdo

- kit

- mayor

- Tarde

- Disposición

- Nivel

- Biblioteca

- Ubicaciones

- hecho

- para lograr

- HACE

- Realizar

- gestionan

- Management

- administrar

- muchos

- max-ancho

- metal

- Metodología

- millones

- errores

- movimiento

- múltiples

- nombres

- ¿ Necesita ayuda

- red

- Nuevo

- Más Nuevos

- Ofrecido

- ONE

- abre

- óptimo

- optimización

- Optimización

- ecológicos

- paquete

- patas

- planificar

- Platón

- Inteligencia de datos de Platón

- PlatónDatos

- Mucho

- más

- punto

- Popular

- posible

- Publicación

- industria

- Análisis predictivo

- producir

- correctamente

- prototipo

- proporciona un

- Búsqueda

- con rapidez

- darse cuenta de

- recibe

- reciente

- Requisitos

- Resultados

- devoluciones

- una estrategia SEO para aparecer en las búsquedas de Google.

- Ejecutar

- escenarios

- Buscar

- semiconductor

- pantalones cortos

- tienes

- Siemens

- Signal

- Silicio

- soltero

- So

- algo

- Pronto

- Fuente

- estándar

- comienzo

- pasos

- sorpresas

- te

- ¡Prepárate!

- equipo

- equipos

- técnicas

- Tecnología

- La

- su

- térmico

- Tres

- A través de esta formación, el personal docente y administrativo de escuelas y universidades estará preparado para manejar los recursos disponibles que derivan de la diversidad cultural de sus estudiantes. Además, un mejor y mayor entendimiento sobre estas diferencias y similitudes culturales permitirá alcanzar los objetivos de inclusión previstos.

- a

- juntos

- del IRS

- tema

- Total

- Actualizar

- actualizado

- utilizan el

- vendedores

- Verificación

- verificar

- vía

- Virtual

- sean

- mientras

- seguirá

- Actividades:

- trabajar juntos

- flujo de trabajo

- años

- Rendimiento

- tú

- zephyrnet