Στο IEDM 2023, ο Naoto Horiguchi παρουσίασε τα CFET και την ενσωμάτωση Middle of Line. Είχα την ευκαιρία να μιλήσω με τον Naoto για αυτή τη δουλειά και αυτή η συγγραφή βασίζεται στην παρουσίασή του στο IEDM και στη συζήτησή μας στη συνέχεια. Πάντα απολαμβάνω να μιλάω με τον Naoto, είναι ένας από τους ηγέτες στην ανάπτυξη τεχνολογίας λογικής, εξηγεί την τεχνολογία με τρόπο κατανοητό και ανταποκρίνεται και είναι εύκολο να δουλέψεις μαζί του.

Γιατί χρειαζόμαστε CFET

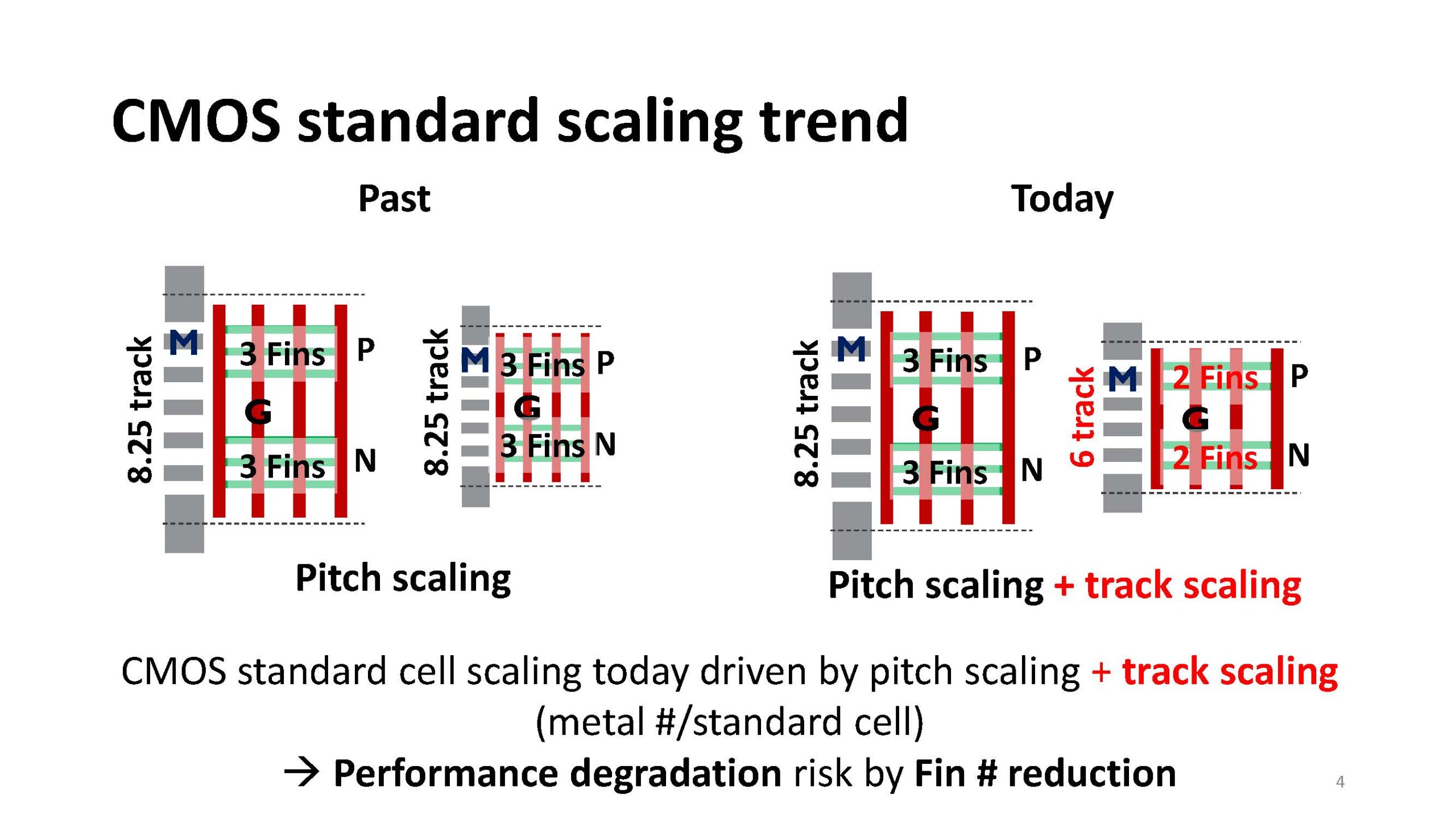

Καθώς η κλιμάκωση CMOS έχει μεταβεί από την καθαρά κλιμάκωση με βάση το βήμα σε κλιμάκωση με βάση τον τόνο και την κλιμάκωση βάσει τροχιάς, η μείωση του πληθυσμού των πτερυγίων έχει καταστεί απαραίτητη, βλέπε σχήμα 1. Κάθε φορά που μειώνετε τον αριθμό των πτερυγίων μειώνεται η απόδοση.

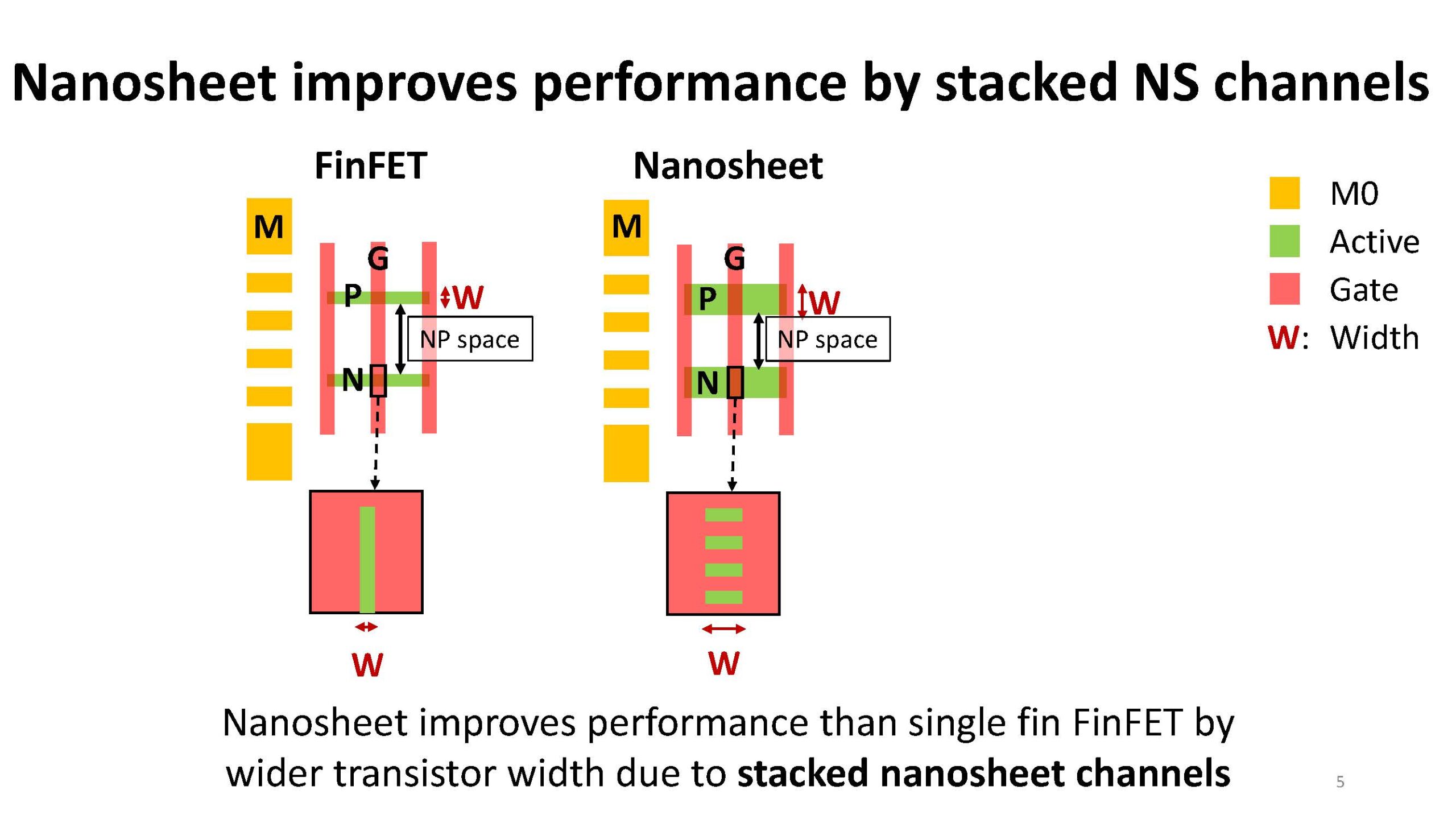

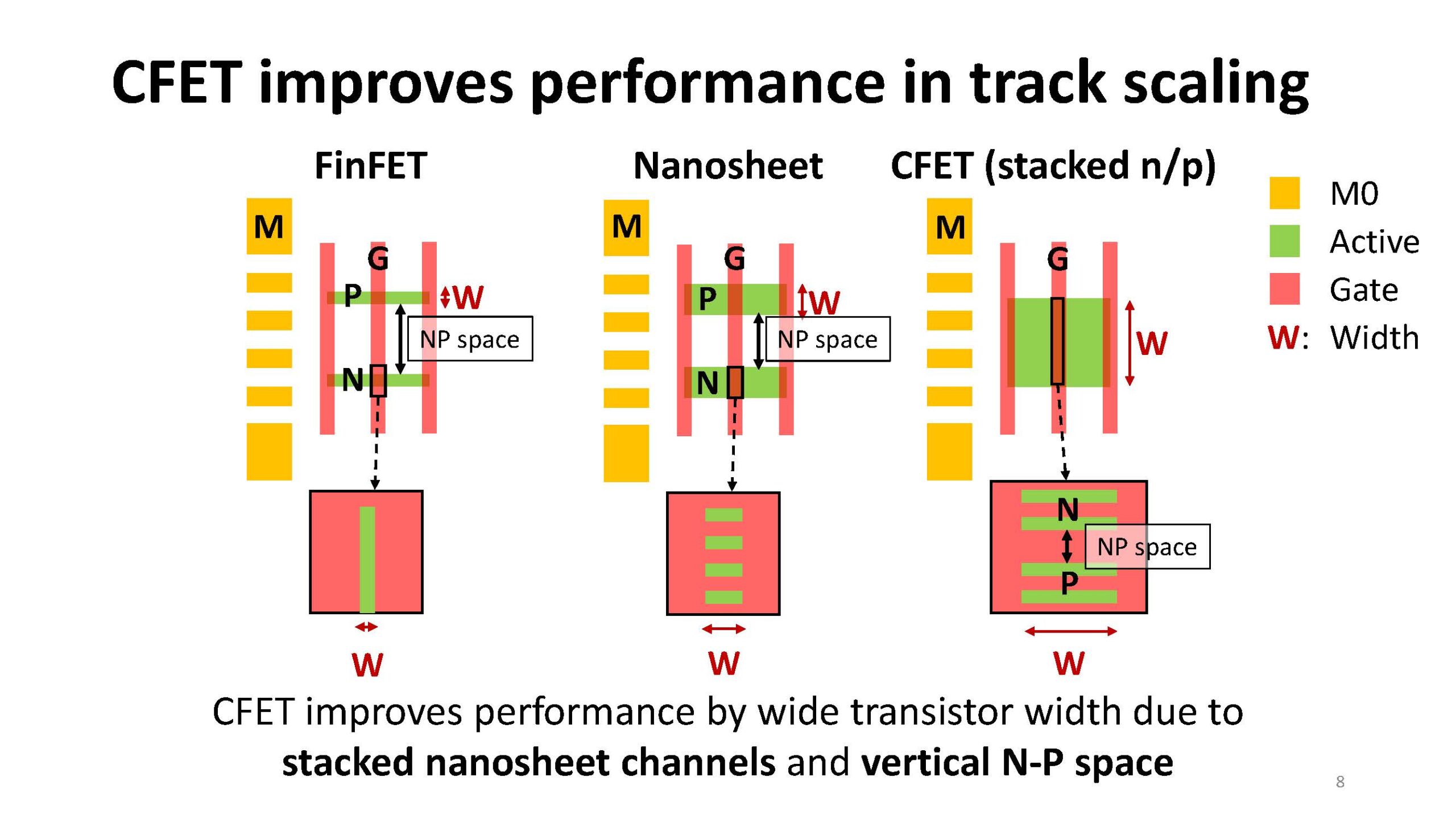

Μετακινώντας από τα FinFEts στο στοιβαγμένο HΗ απόδοση των οριζόντιων νανοφύλλων (HNS) μπορεί να βελτιωθεί/ανακτηθεί με ευρύτερες στοίβες νανοφύλλων και τη στοίβαξη πολλαπλών νανοφύλλων κάθετα, βλέπε σχήμα 2.

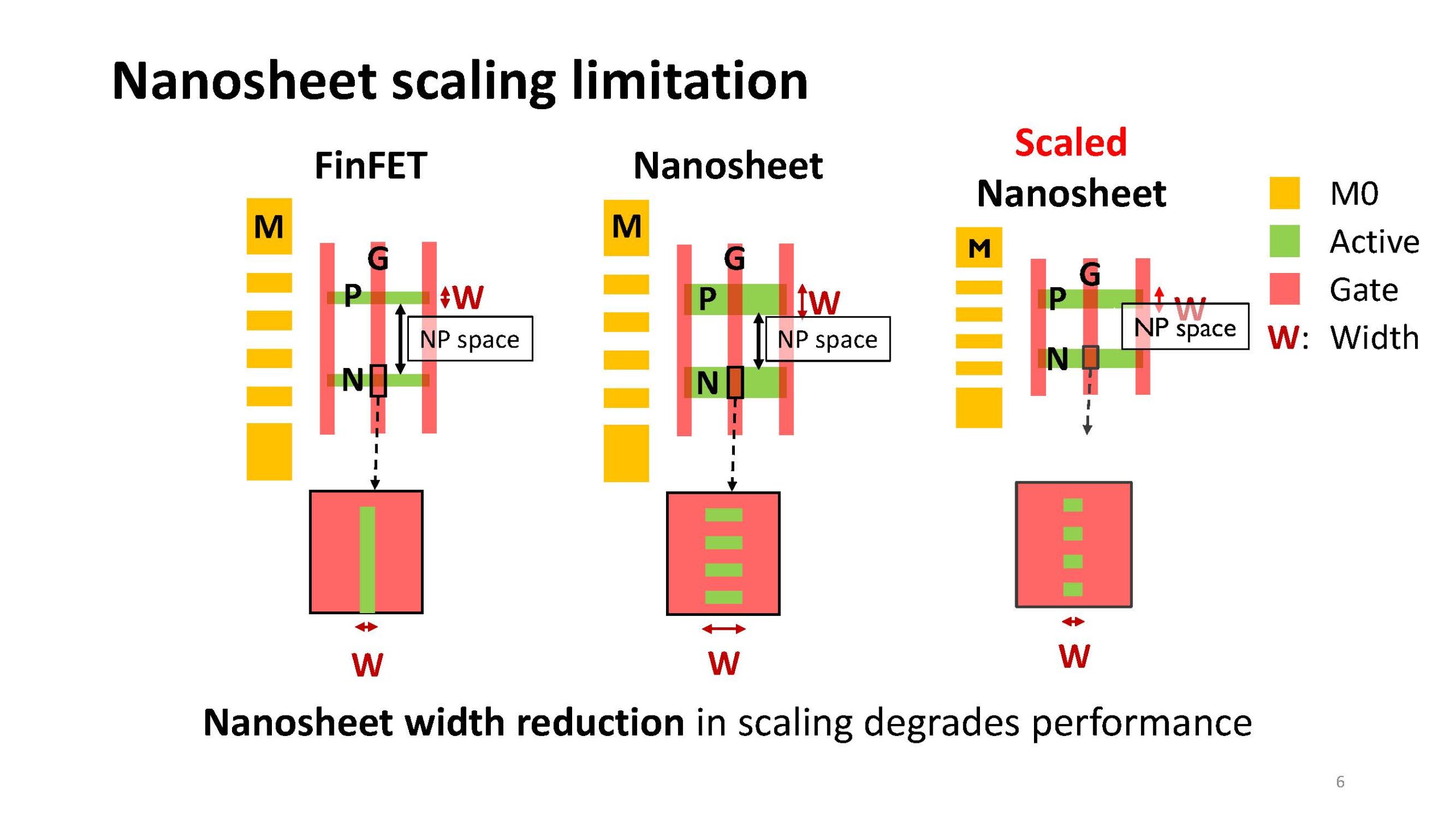

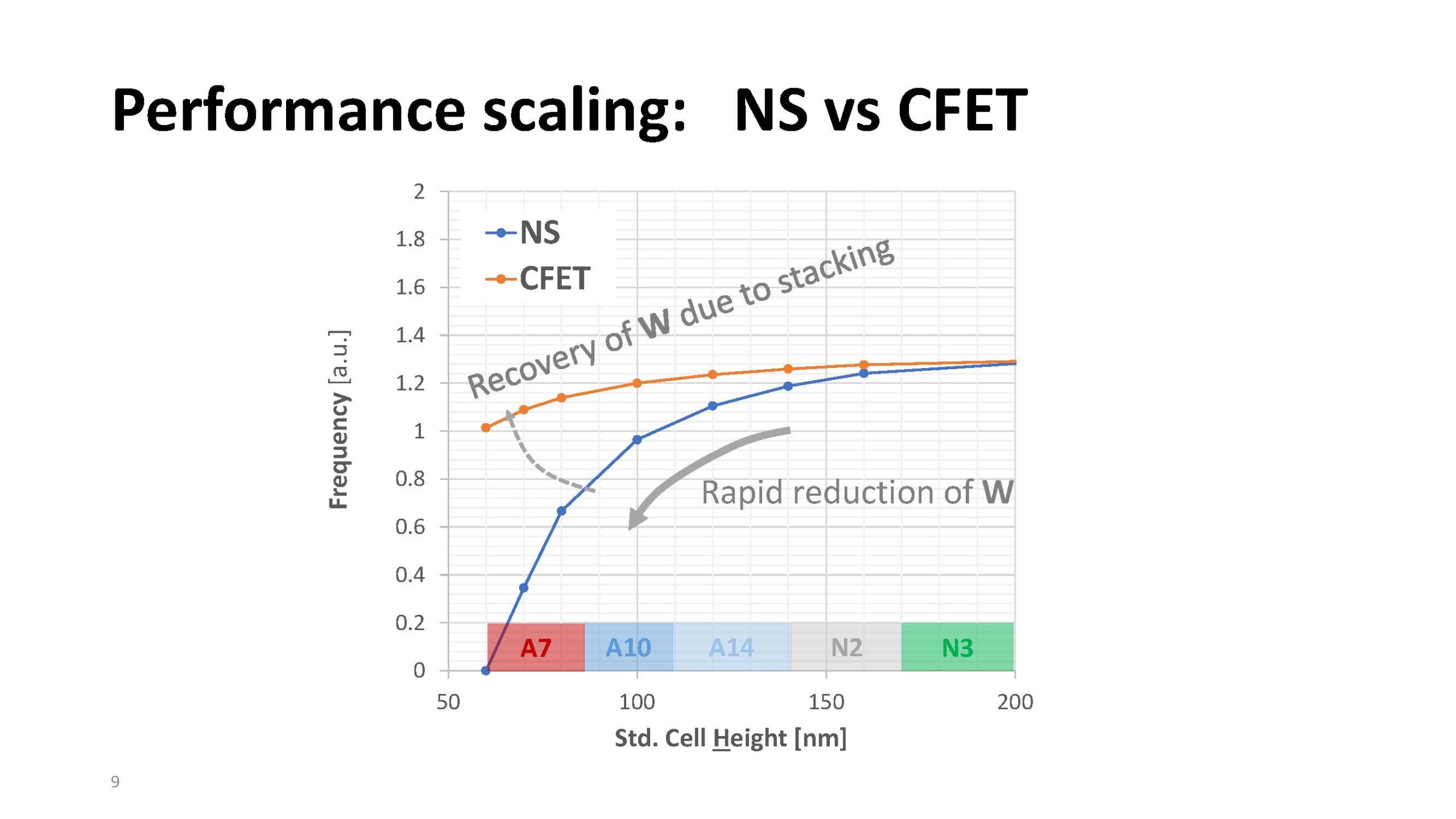

Όμως, όπως είδαμε με τα FinFETs, η κλιμάκωση των νανοφύλλων οδηγεί τελικά σε μειωμένη απόδοση, δείτε το σχήμα 3.

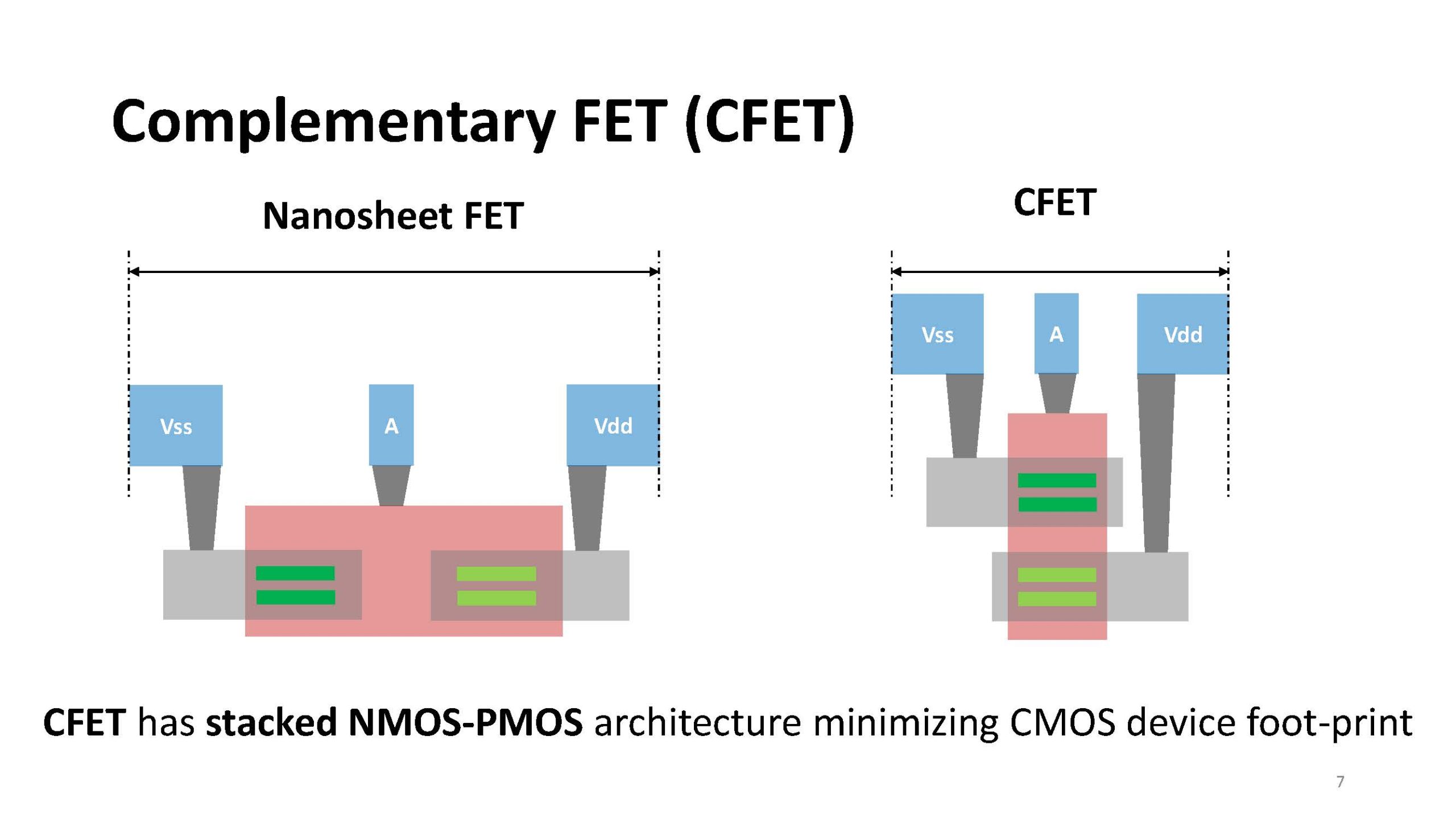

Τα CFET (συμπληρωματικό FET) στοιβάζουν τα nFET και pFET, βλέπε σχήμα 4.

Τα CFET επαναφέρουν για άλλη μια φορά τους περιορισμούς κλιμάκωσης επειδή τα nFET και pFET στοιβάζονται και η απόσταση np μεταξύ των συσκευών γίνεται κάθετη αντί για οριζόντια, αυτό επιτρέπει ευρύτερα φύλλα, βλέπε σχήμα 5.

Το Σχήμα 6 παρουσιάζει μια σύγκριση της απόδοσης HNS και CFET έναντι του ύψους κυψέλης, υπογραμμίζοντας το πλεονέκτημα του CFET.

Μονολιθικό έναντι διαδοχικού CFET

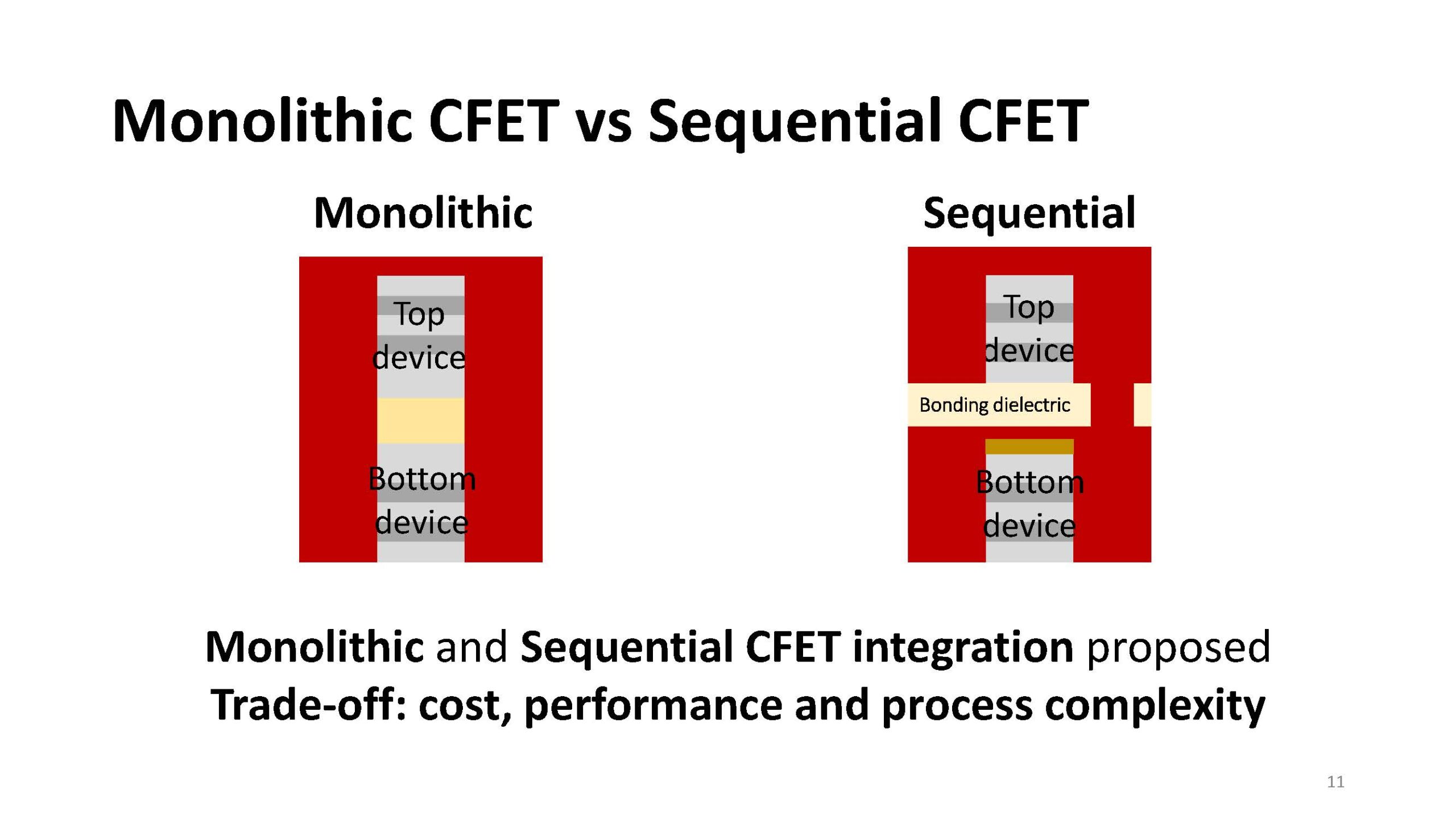

Υπάρχουν δύο θεμελιωδώς διαφορετικές προσεγγίσεις για την κατασκευή CFET. Σε μια μονολιθική ροή τα CFET κατασκευάζονται σε μια γκοφρέτα σε συνεχή ροή διεργασίας. Σε μια διαδοχική ροή, η κάτω συσκευή κατασκευάζεται σε μια γκοφρέτα, στη συνέχεια μια δεύτερη γκοφρέτα συνδέεται με την πρώτη γκοφρέτα και η επάνω συσκευή κατασκευάζεται στη δεύτερη γκοφρέτα.

Σε μια διαδοχική ροή υπάρχει ένα διηλεκτρικό συγκόλλησης μεταξύ των δύο συσκευών, βλέπε σχήμα 7.

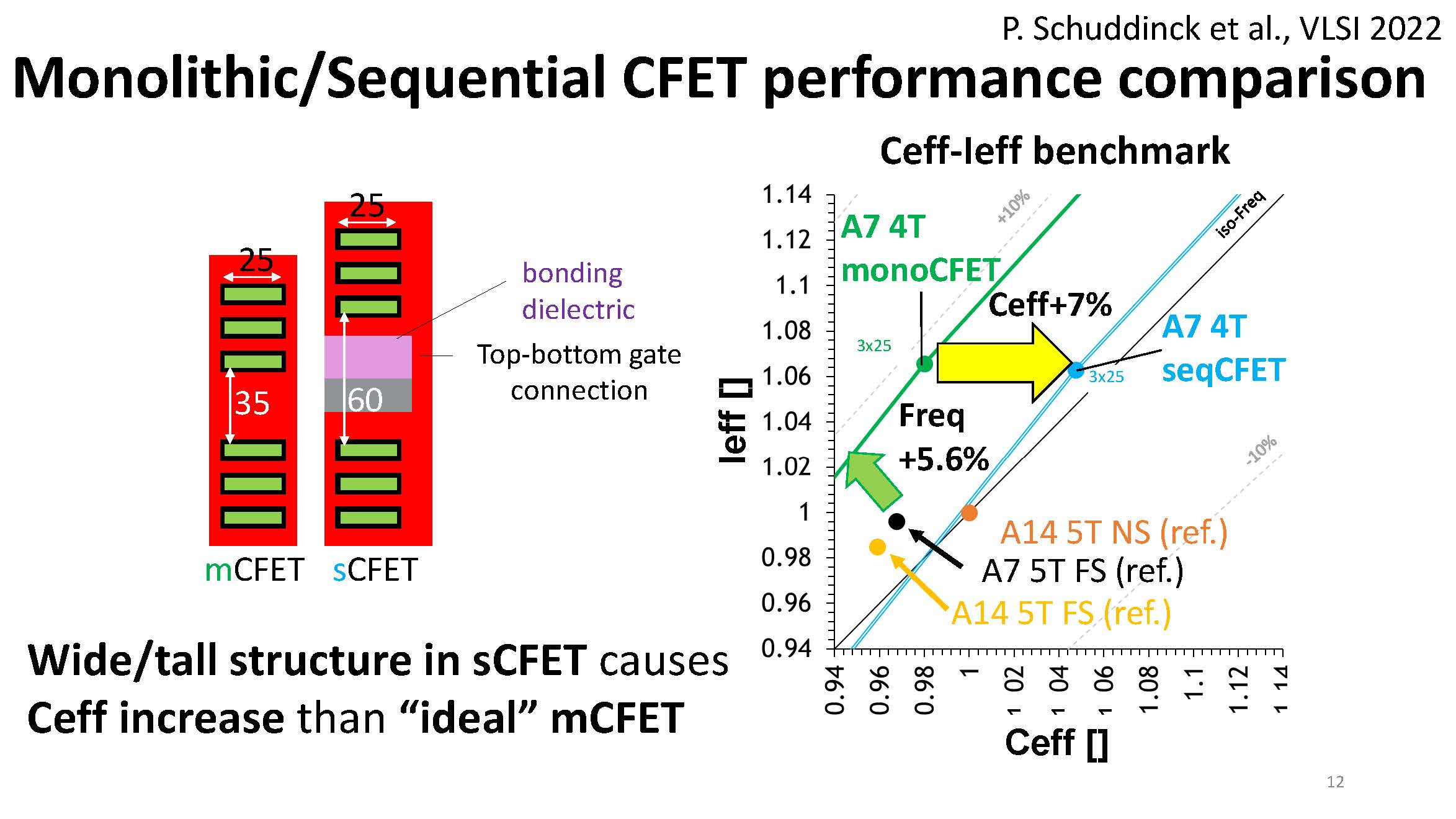

Λόγω του διηλεκτρικού συγκόλλησης, η δομή είναι ψηλότερη και έχει υψηλότερη απόδοση υποβάθμισης της χωρητικότητας, βλέπε σχήμα 8.

Τα διαδοχικά CFET είναι πιο ακριβά στην κατασκευή από τα μονολιθικά CFET και μεταξύ αυτού και της υποβάθμισης της απόδοσης, φαίνεται ότι η βιομηχανία επικεντρώνεται σε μονολιθικά CFET.

Μονολιθική Επεξεργασία CFET

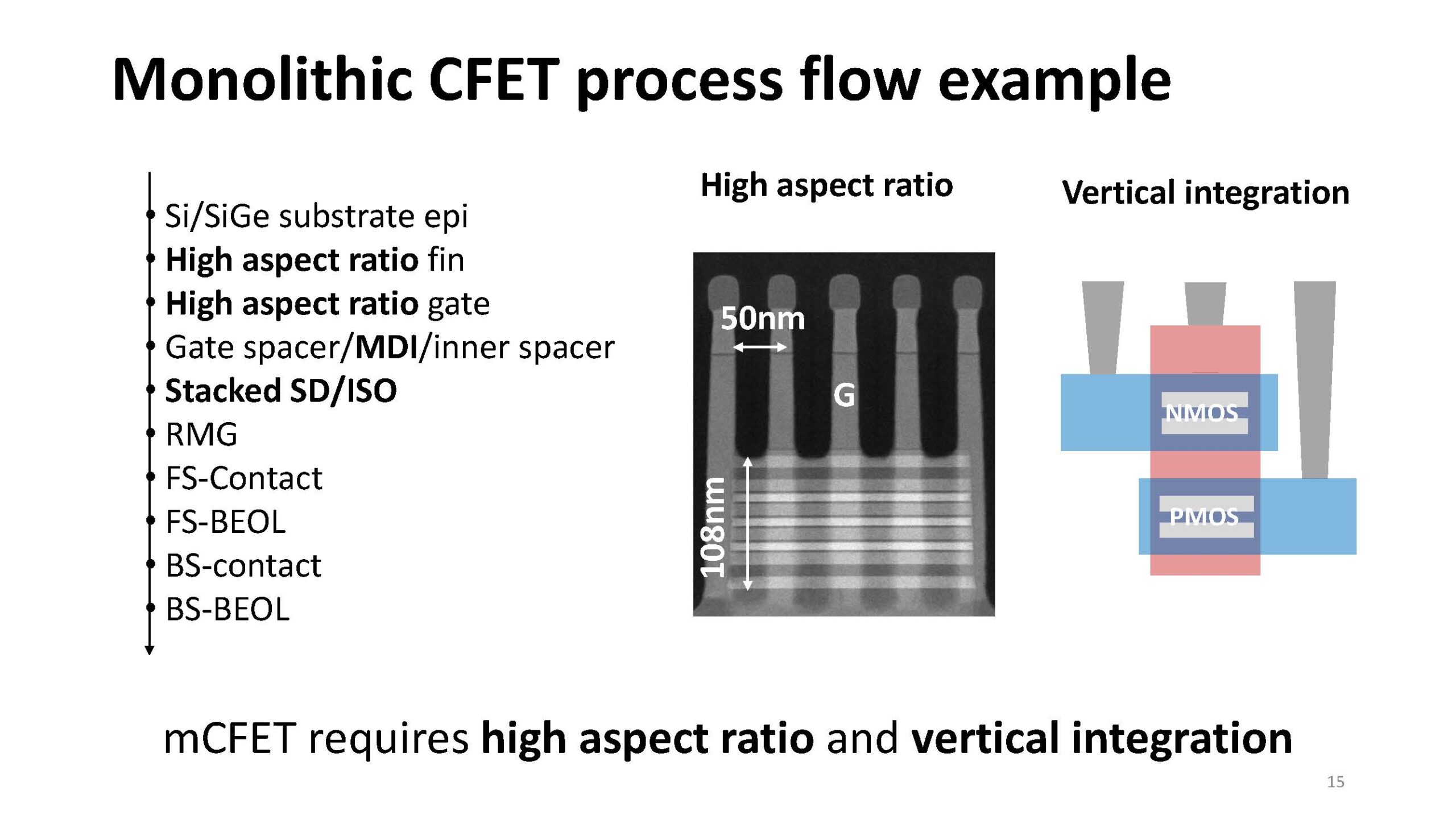

Η μονολιθική διαδικασία CFET απεικονίζεται στο σχήμα 9.

Τα βήματα με έντονους χαρακτήρες είναι ιδιαίτερα απαιτητικά:

- Οι οριζόντιες στοίβες νανοφύλλων (πτερύγια) έχουν ήδη υψηλή αναλογία διαστάσεων, τότε για να κάνετε ένα CFET στοιβάζετε τις στοίβες nFET και pFET τη μία πάνω στην άλλη με ένα σχετικά παχύ στρώμα ενδιάμεσα διπλασιάζοντας το ύψος.

- Ο σχηματισμός πύλης είναι επίσης υψηλός λόγος διαστάσεων όπως περιγράφηκε στο προηγούμενο σημείο.

- Η επιταξιακή πηγή/αποχετεύσεις πρέπει να είναι κάθετα απομονωμένη μεταξύ τους.

- Δεν αναφέρεται ρητά, κατασκευάζεται η κάτω πηγή/αποχέτευση της συσκευής και στη συνέχεια κατασκευάζεται η επάνω πηγή/αποχέτευση της επάνω συσκευής. Η θερμική επεξεργασία της επάνω συσκευής και τα επόμενα βήματα πρέπει να γίνονται σε αρκετά χαμηλές θερμοκρασίες ώστε να μην υποβαθμίζεται η κάτω συσκευή.

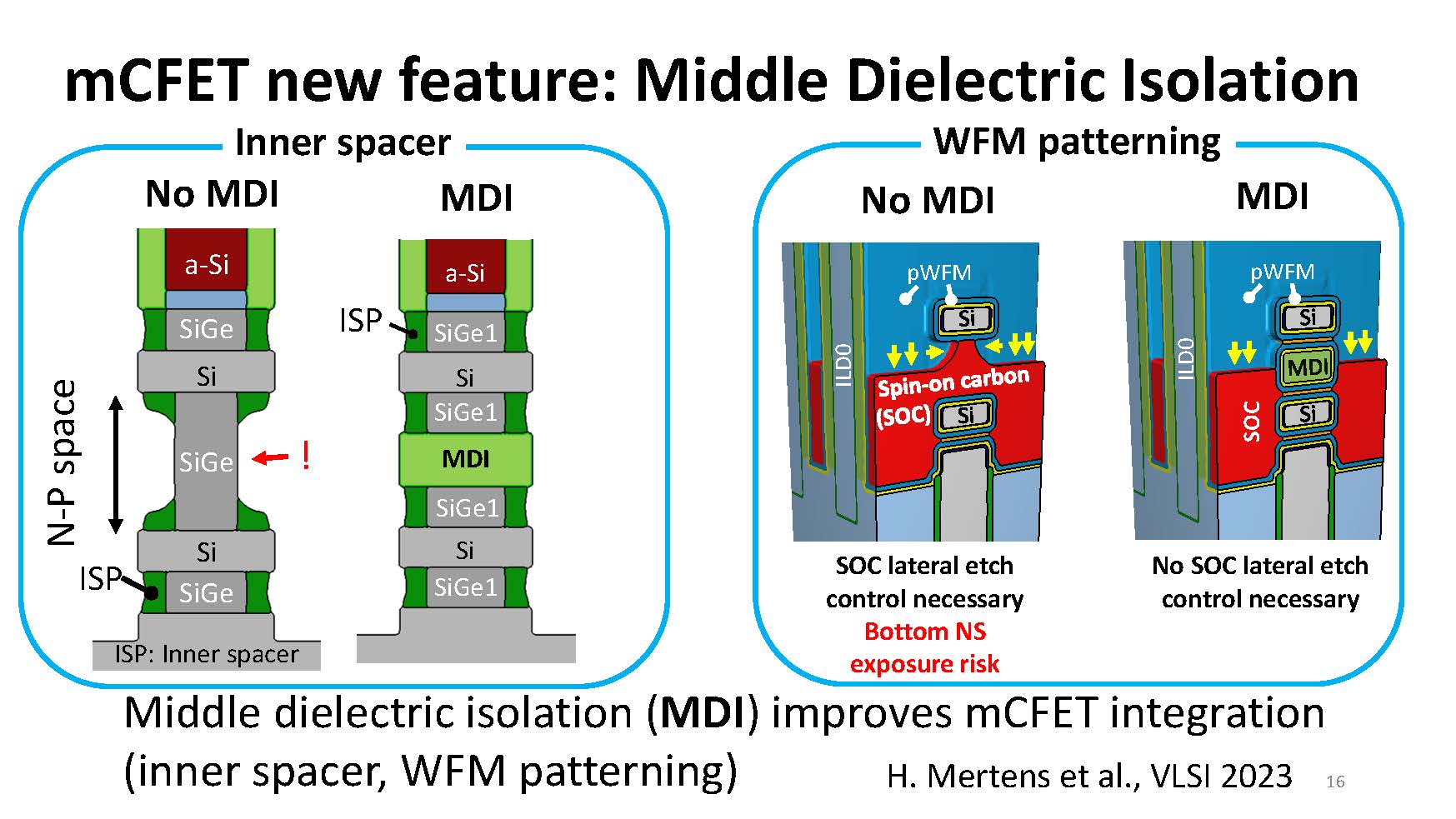

Ένα ιδιαίτερα ενδιαφέρον μέρος αυτής της παρουσίασης ήταν το μέρος της Μέσης Διηλεκτρικής Απομόνωσης (MDI), δεν είχα ξαναδεί αυτό το θέμα. Το MDI αποδεικνύει το μοτίβο εσωτερικού διαχωριστή και υλικού λειτουργίας εργασίας (WFM).

Το Σχήμα 10 απεικονίζει το φαινόμενο MDI στο σχηματισμό εσωτερικού διαχωριστή (αριστερή πλευρά) και μοτίβο WFM (δεξιά πλευρά).

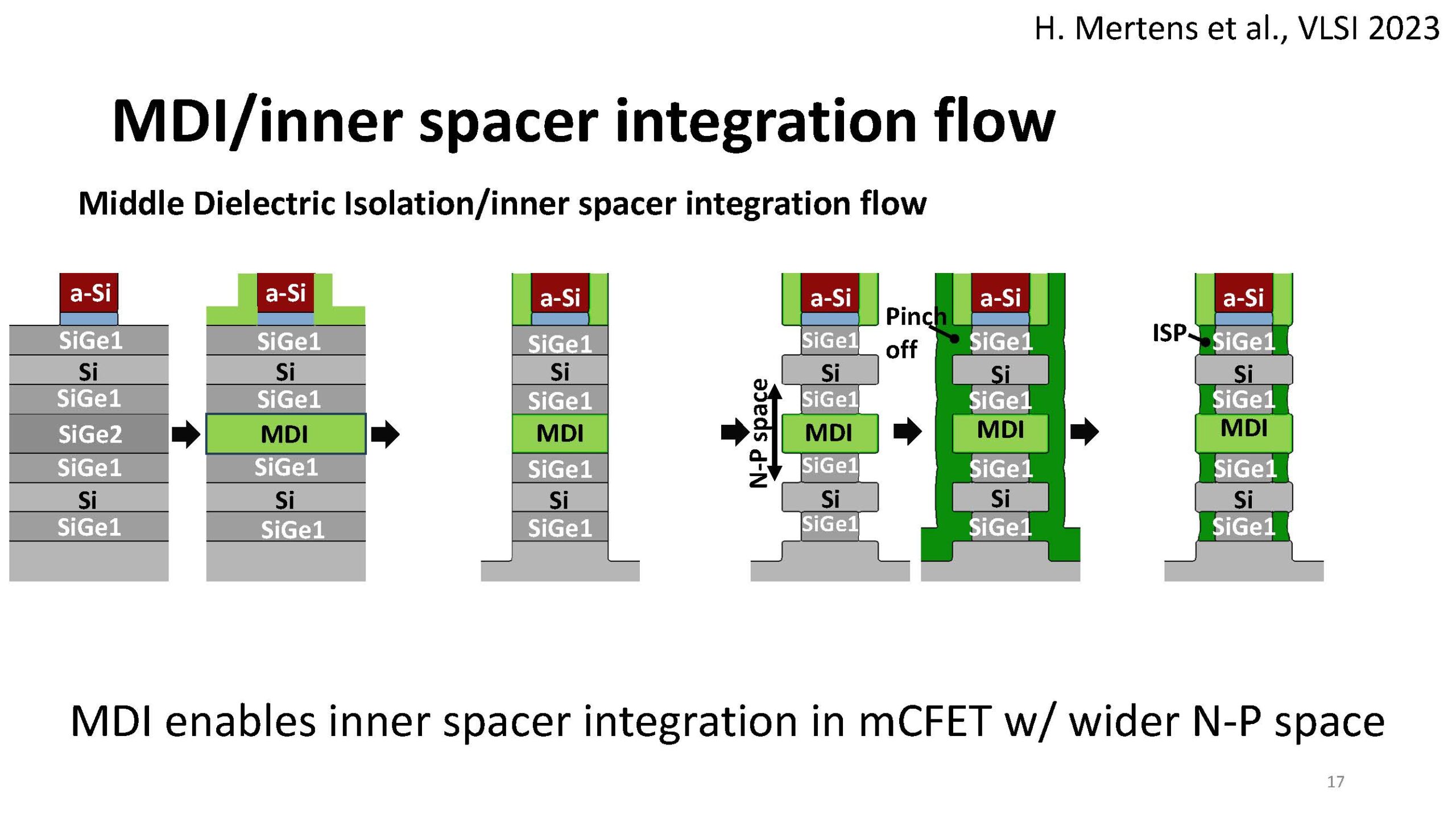

Το Σχήμα 11 απεικονίζει τη ροή ολοκλήρωσης MDI.

Με την ενσωμάτωση του MDI, η κατακόρυφη απόσταση μεταξύ του nFET και του pFET μπορεί να αυξηθεί χωρίς να επηρεαστεί ο σχηματισμός εσωτερικού διαχωριστή.

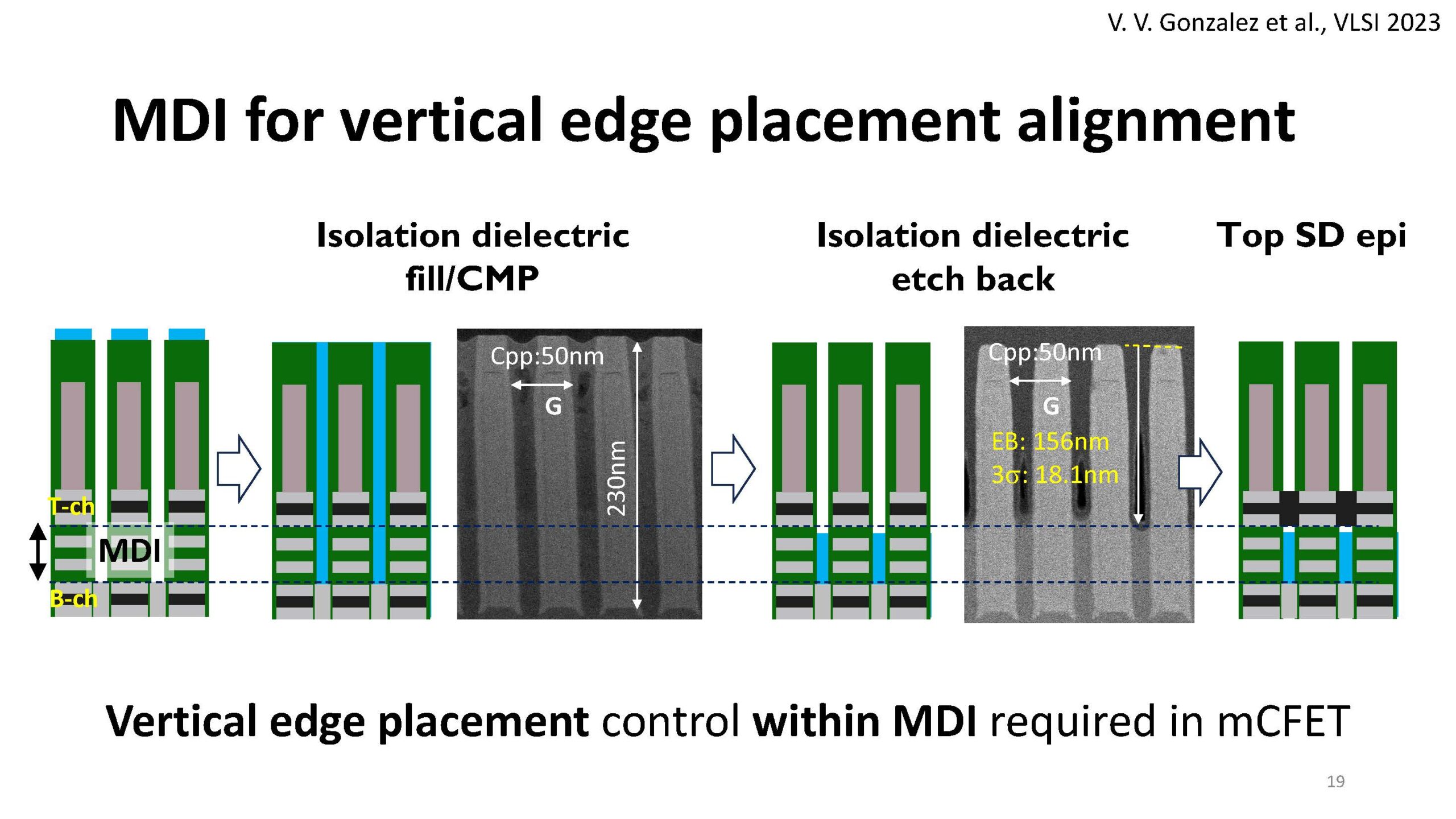

Όπως αναφέρθηκε προηγουμένως, κατασκευάζεται η κάτω πηγή/αποχέτευση της συσκευής και στη συνέχεια κατασκευάζεται η επάνω πηγή/αποχέτευση της συσκευής. Μετά το σχηματισμό της κάτω πηγής/αποχέτευσης, ένα διηλεκτρικό απομόνωσης εναποτίθεται και χαράσσεται πίσω για να εκτεθεί η επάνω συσκευή για επιταξιακό σχηματισμό πηγής/αποχέτευσης. Η ράχη απομόνωσης πρέπει να ελέγχεται με το ύψος MDI, βλέπε σχήμα 12.

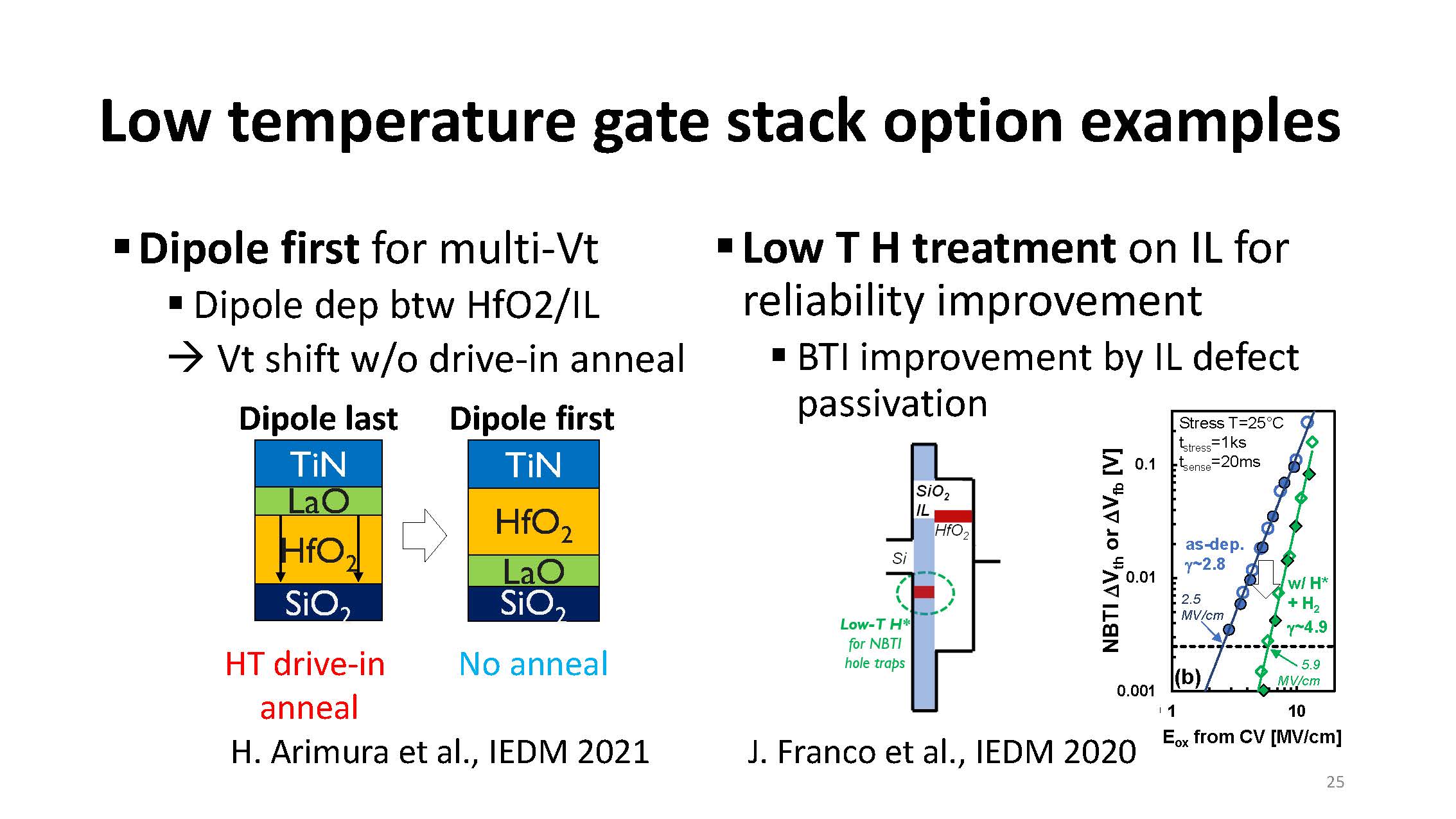

Προκειμένου να ελαχιστοποιηθεί η θερμική υποβάθμιση της απόδοσης της συσκευής, νέες επιλογές WFM με διπολική πρώτη επεξεργασία και δεν απαιτούνται διαδικασίες ανόπτησης και σχηματισμού στρώσεων σε χαμηλή θερμοκρασία, δείτε το σχήμα 13.

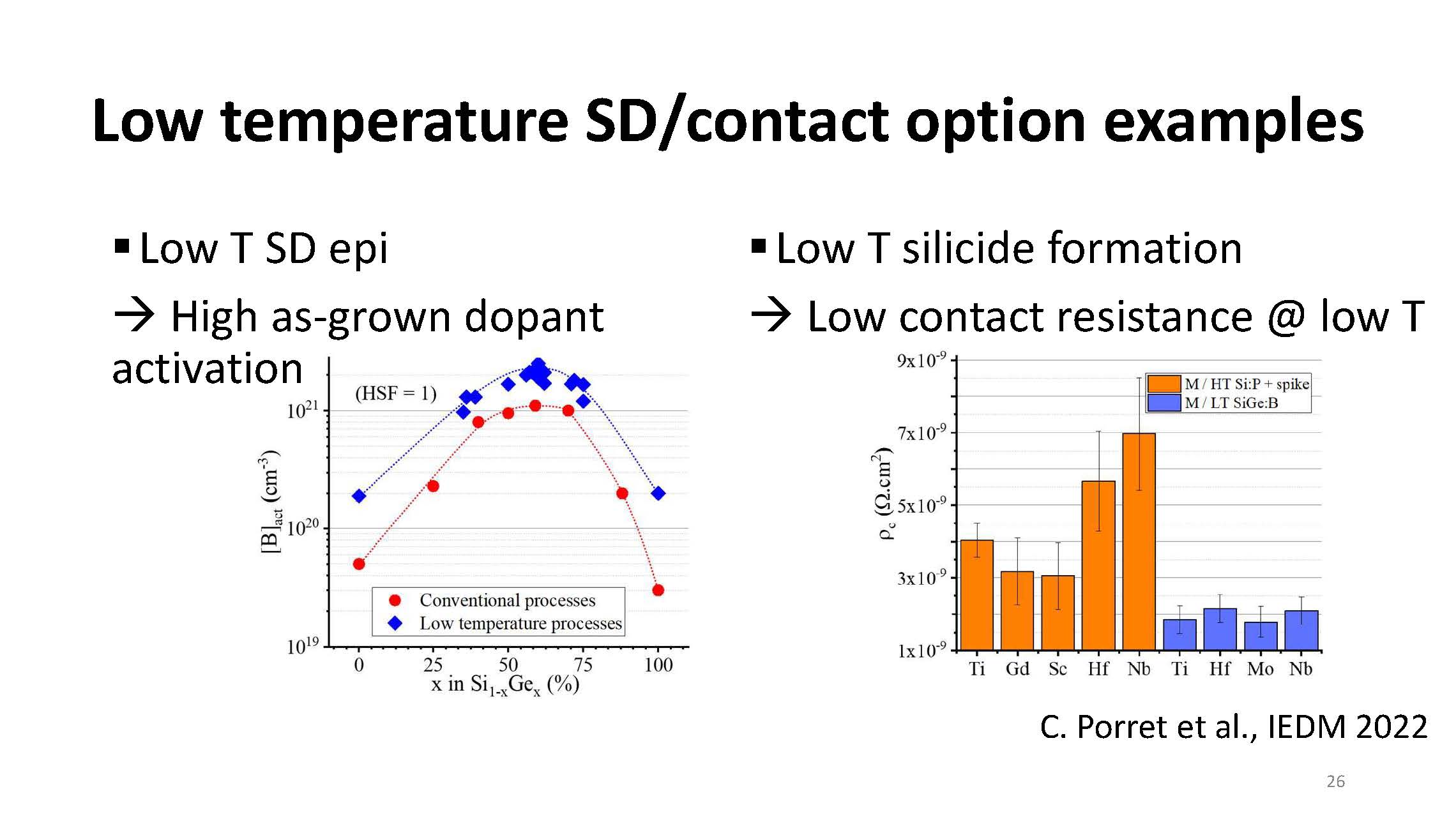

Απαιτούνται επίσης ανάπτυξη πηγής/αποχέτευσης χαμηλής θερμοκρασίας και πυριτίδια χαμηλής θερμοκρασίας για σχηματισμό επαφής, βλέπε σχήμα 14.

Το πυριτικό χαμηλής θερμοκρασίας θα είναι ιδιαίτερα σημαντικό για την άμεση επαφή του πίσω μέρους με την κάτω συσκευή. Η διασύνδεση CFET απαιτεί επαφές με την κάτω και την επάνω συσκευή και με την έλευση της παροχής ρεύματος στο πίσω μέρος, η επάνω συσκευή θα έρχεται σε επαφή από την μπροστινή πλευρική στοίβα διασύνδεσης και η κάτω συσκευή από την πίσω πλευρά. Το μολυβδαίνιο (Mo) και το νιόβιο (Nb) είναι πολλά υποσχόμενα για το pFET και το σκάνδιο (Sc) είναι πολλά υποσχόμενο για το nFET, αν και το Sc είναι δύσκολο να κατατεθεί με ALD.

Διασύνδεση πίσω και μέσης γραμμής

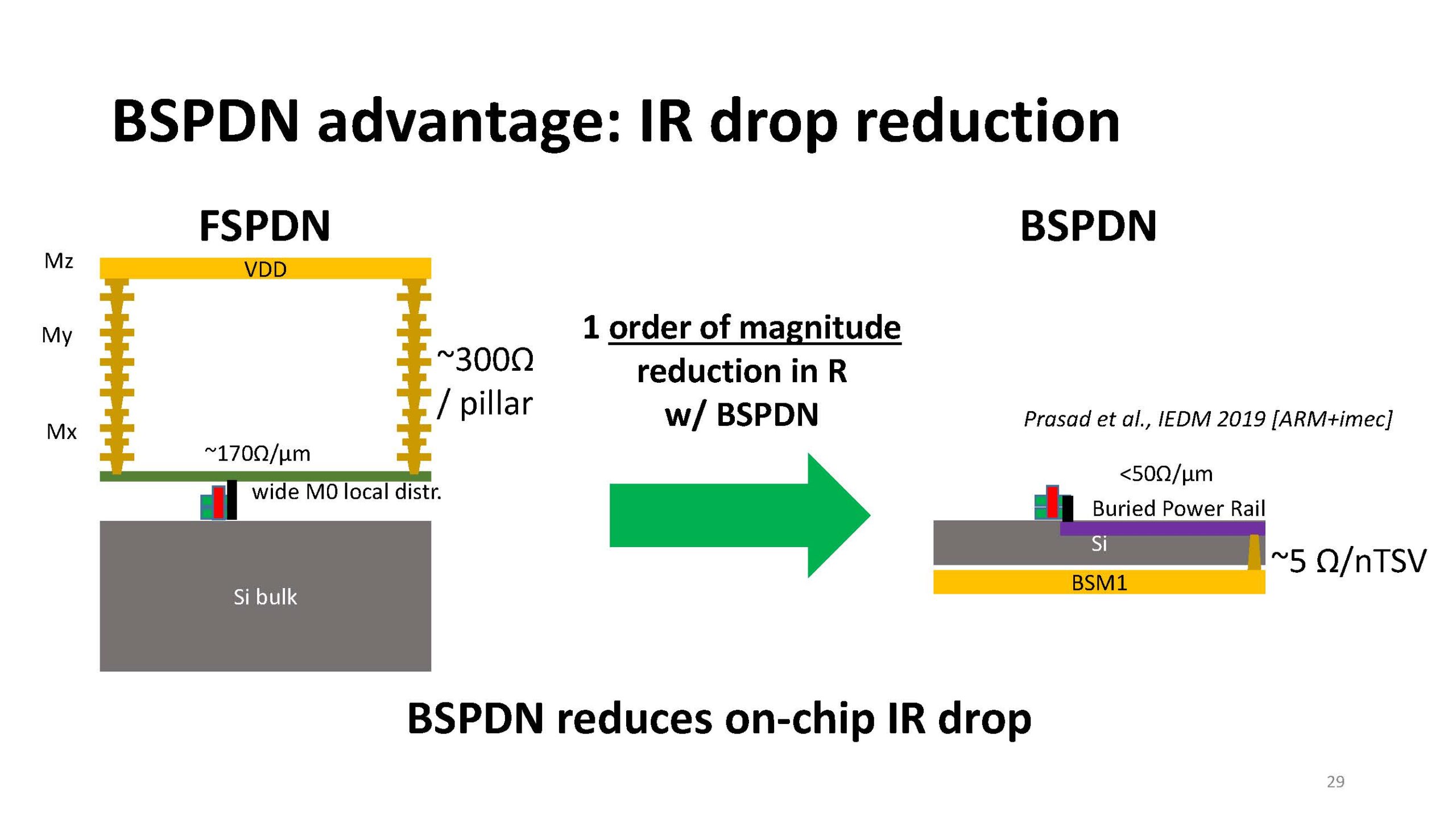

Όπως έχω γράψει προηγουμένως εδώ Το Back Side Power Delivery Network (BSPDN) αναμένεται να παρουσιαστεί φέτος από την Intel και από τη Samsung και την TSMC το 2026. Ο διαχωρισμός της διασύνδεσης σε συνδέσεις σήματος στην μπροστινή πλευρά και συνδέσεις ρεύματος στην πίσω πλευρά μειώνει την πτώση IR (απώλεια ισχύος) κατά μια τάξη μεγέθους, βλ. εικόνα 15.

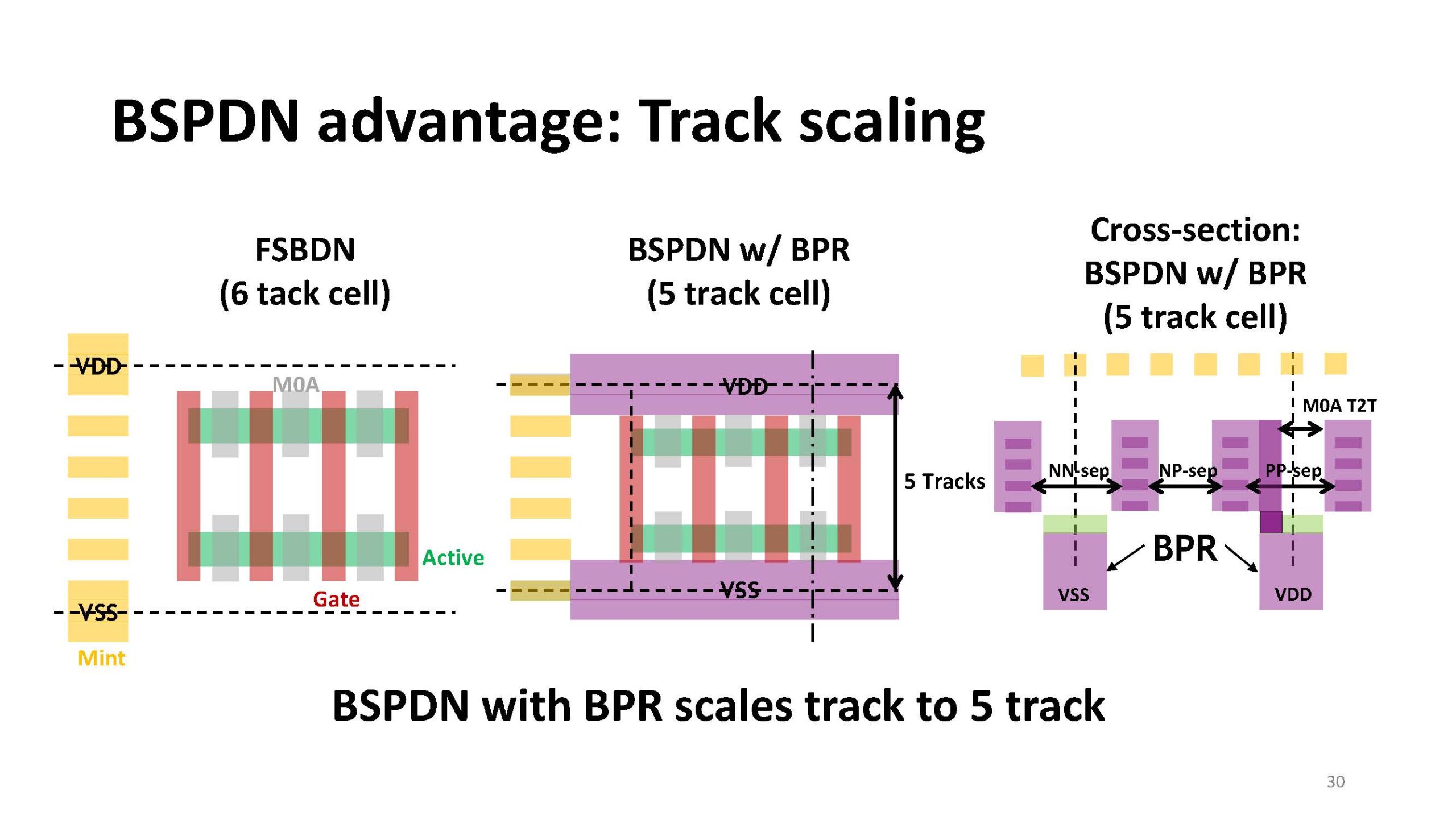

Το BSPDN βελτιώνει επίσης την κλιμάκωση του κομματιού υποστηρίζοντας μια μείωση από κελί 6 κομματιών σε κελί 5 κομματιών, δείτε την εικόνα 16.

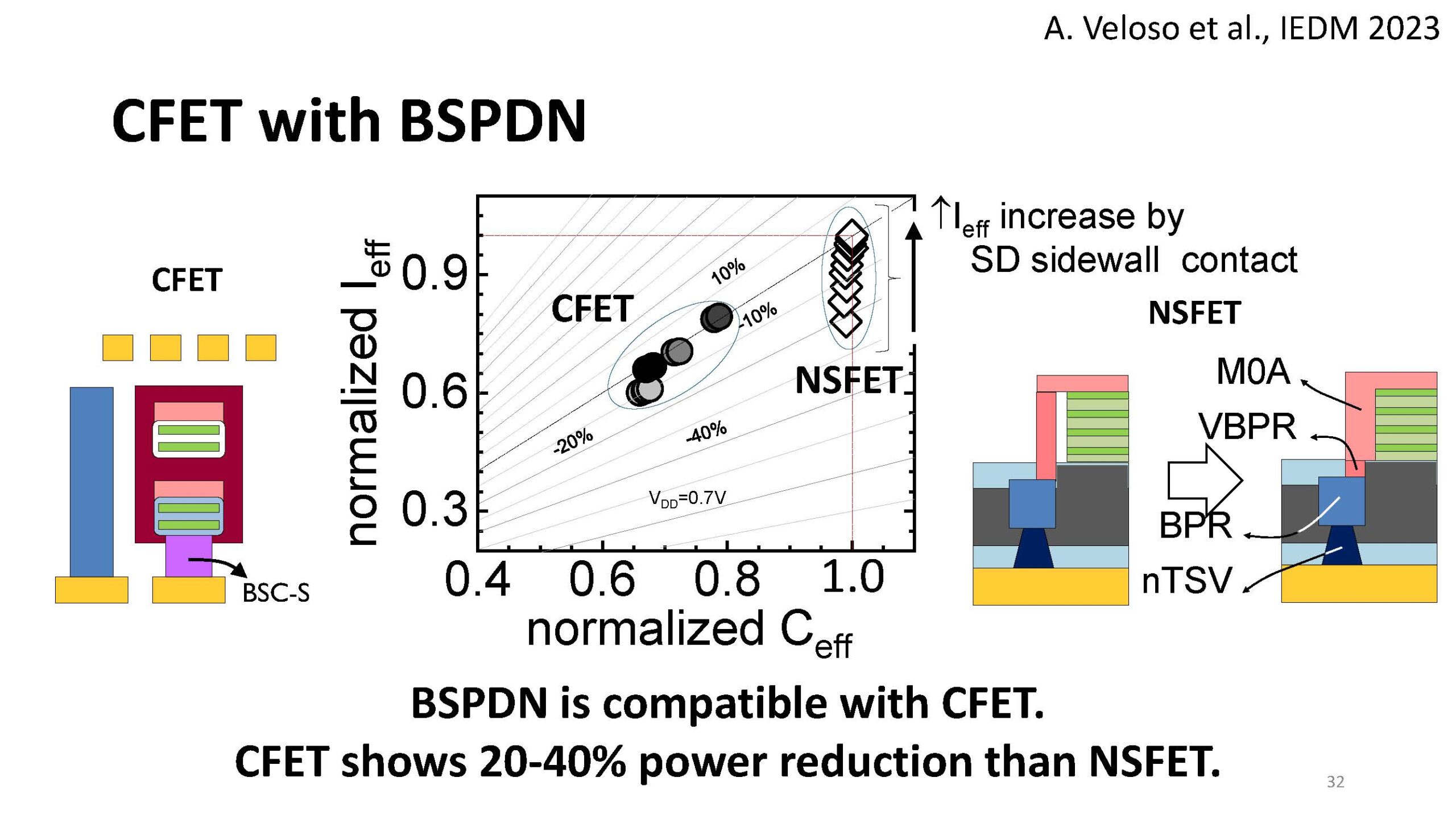

Η ενσωμάτωση του BSPDN με το CFET μπορεί να προσφέρει μείωση ισχύος 20% έως 40% σε σύγκριση με Οριζόντια στοιβαγμένα NanoSheets (HNS), βλέπε σχήμα 17.

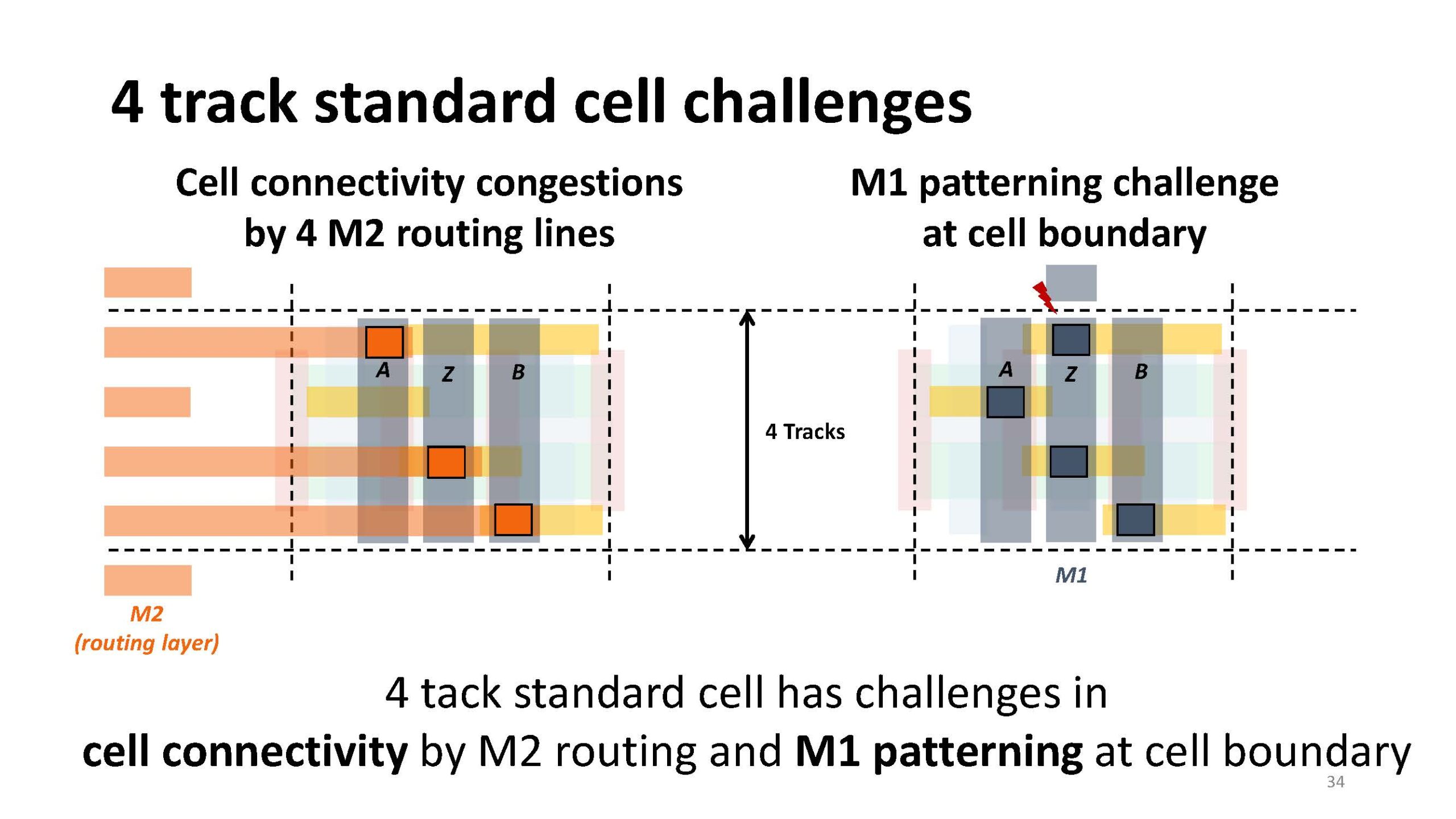

Για να προχωρήσουμε πέρα από μια κυψέλη 5 τροχιών σε μια κυψέλη 4 τροχιών, πρέπει να ξεπεραστούν οι προκλήσεις διασύνδεσης κυψελών, δείτε την εικόνα 18.

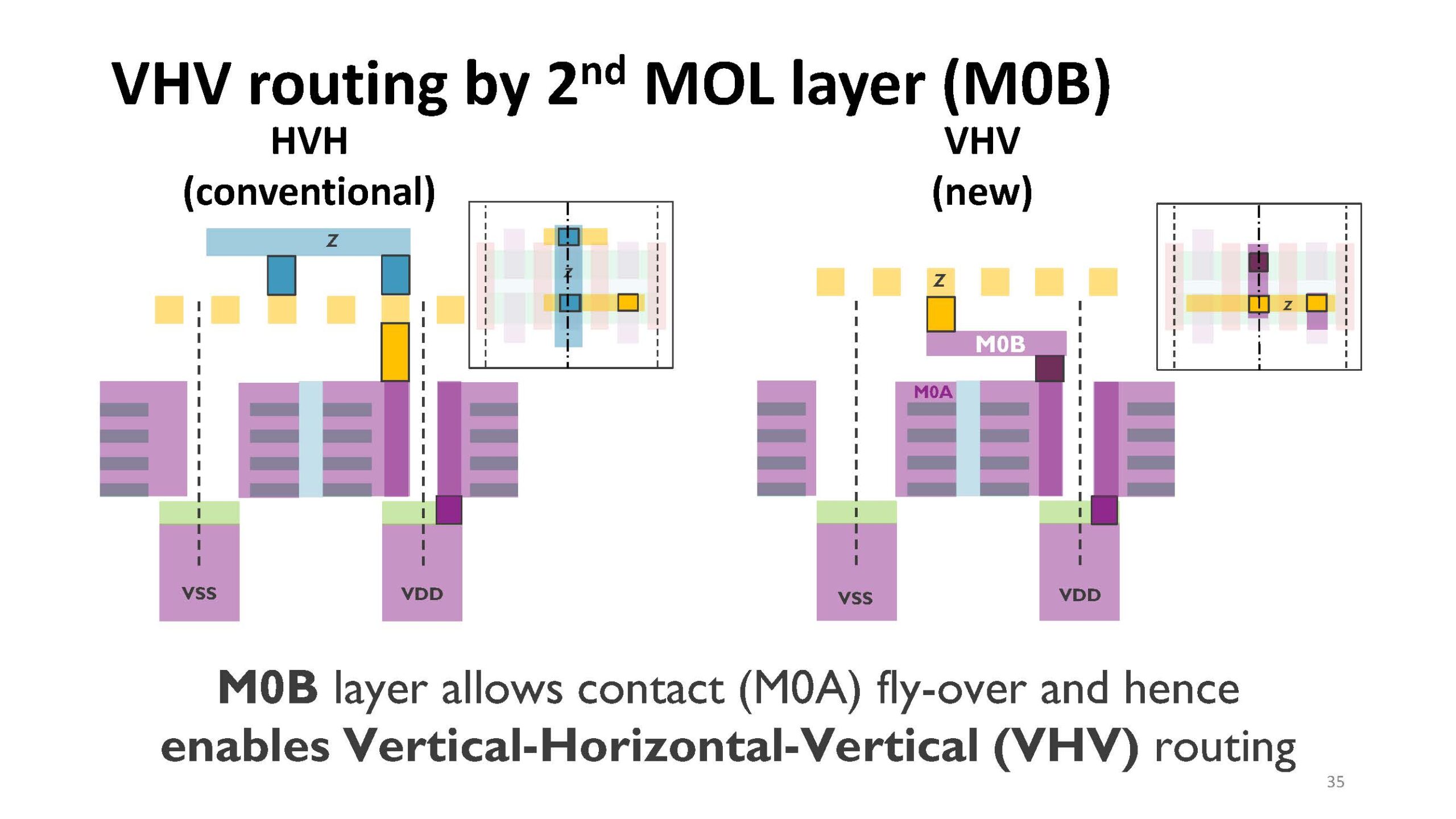

Η κάθετη-οριζόντια-κάθετη διάταξη με πρόσθετα επίπεδα μέσης γραμμής (MOL) μπορεί να ενεργοποιήσει κελιά 4 κομματιών, δείτε την εικόνα 19.

Έχω γράψει στο παρελθόν για τη δουλειά της Imec σε αυτόν τον τομέα εδώ οπότε δεν θα επαναλάβω αυτές τις πληροφορίες.

Ρώτησα τον Naoto τι θα χρειαζόταν για να προχωρήσουμε πέρα από ένα κελί 4 κομματιών σε ένα κελί 3 κομματιών, απάντησε ότι η Imec εργάζεται σε αυτήν τη βελτιστοποίηση τώρα, ότι μπορεί να απαιτεί προσθήκη στρωμάτων MOL και πιθανώς σύνδεση από πάνω προς τα κάτω δίπλα στο συσκευή που θα επηρεάσει την τυπική διάταξη κυψέλης.

Ρώτησα επίσης τον Naoto πότε πίστευε ότι θα μπορούσαμε να δούμε να εφαρμόζονται τα CFET και είπε ότι πιθανώς η γενιά λογικής A10 ή η γενιά A7.

Οι συγγραφείς σημειώνουν ότι η Intel, η Samsung και η TSMC δημοσίευσαν όλες εργασίες για τα CFET στο IEDM φέτος και τόσο η Intel όσο και η TSMC διαθέτουν χάρτες επιλογών τεχνολογίας που δείχνουν τα FinFET να δίνουν τη θέση τους στα HNS και μετά στα CFET.

Συμπέρασμα

Η Imec συνεχίζει να παρουσιάζει εξαιρετική πρόοδο στην ανάπτυξη των CFET ως επιλογή επόμενης γενιάς μετά το HNS. Σε αυτήν την εργασία έχουν περιγραφεί όλες οι επιλογές ενσωμάτωσης συσκευών καθώς και οι επιλογές BSPDN και MOL.

Διαβάστε επίσης:

IEDM 2023 – Μοντελοποίηση εκπομπών άνθρακα 300 mm Fab Wafer

SMIC N+2 στο Huawei Mate Pro 60

Ενημέρωση ASML SEMICON West 2023

Μοιραστείτε αυτήν την ανάρτηση μέσω:

- SEO Powered Content & PR Distribution. Ενισχύστε σήμερα.

- PlatoData.Network Vertical Generative Ai. Ενδυναμώστε τον εαυτό σας. Πρόσβαση εδώ.

- PlatoAiStream. Web3 Intelligence. Ενισχύθηκε η γνώση. Πρόσβαση εδώ.

- PlatoESG. Ανθρακας, Cleantech, Ενέργεια, Περιβάλλον, Ηλιακός, Διαχείριση των αποβλήτων. Πρόσβαση εδώ.

- PlatoHealth. Ευφυΐα βιοτεχνολογίας και κλινικών δοκιμών. Πρόσβαση εδώ.

- πηγή: https://semiwiki.com/semiconductor-services/340811-iedm-2023-imec-cfet/

- :έχει

- :είναι

- :δεν

- $UP

- 06

- 07

- 08

- 09

- 1

- 10

- 11

- 12

- 13

- 14

- 15%

- 16

- 17

- 19

- 2023

- 2026

- 25

- 26

- 29

- 30

- 32

- 35%

- 7

- 8

- 9

- a

- Σχετικά με εμάς

- Επιπλέον

- Πρόσθετος

- Πλεονέκτημα

- έλευση

- Μετά το

- πάλι

- Όλα

- ήδη

- Επίσης

- Αν και

- πάντοτε

- an

- και

- εμφανίζεται

- προσεγγίσεις

- ΕΙΝΑΙ

- ΠΕΡΙΟΧΗ

- AS

- άποψη

- At

- πίσω

- βασίζονται

- BE

- επειδή

- γίνονται

- γίνεται

- ήταν

- πριν

- μεταξύ

- Πέρα

- και οι δύο

- Κάτω μέρος

- by

- κλήση

- που ονομάζεται

- CAN

- άνθρακας

- κύτταρο

- Κύτταρα

- προκλήσεις

- πρόκληση

- ευκαιρία

- σύγκριση

- συμπληρωματικός

- σύνδεση

- Διασυνδέσεις

- περιορισμούς

- επικοινωνήστε μαζί μας

- Επαφές

- συνεχίζεται

- συνεχής

- ελέγχεται

- διανομή

- κατάθεση

- κατατεθεί

- περιγράφεται

- Ανάπτυξη

- συσκευή

- Συσκευές

- διαφορετικές

- κατευθύνει

- συζήτηση

- do

- γίνεται

- διπλασιασμό

- Πτώση

- κάθε

- εύκολος

- άκρη

- αποτέλεσμα

- ενεργοποιήσετε

- δίνει τη δυνατότητα

- απολαύσετε

- αρκετά

- τελικά

- έξοχος

- αναμένεται

- ακριβά

- Εξηγεί

- ρητά

- FET

- Εικόνα

- πτερύγιο

- τελικός

- FINE

- Όνομα

- ροή

- επικεντρώθηκε

- ακολουθήστε

- Για

- σχηματισμός

- από

- εμπρός

- λειτουργία

- θεμελιωδώς

- πύλη

- γενεά

- Δίνοντας

- Go

- Ανάπτυξη

- είχε

- Σκληρά

- Έχω

- he

- ύψος

- Ψηλά

- υψηλότερο

- επισήμανση

- του

- Οριζόντιος

- HTTPS

- Huawei

- i

- απεικονίζει

- Επίπτωση

- επιπτώσεις

- εφαρμοστεί

- σημαντικό

- βελτιωθεί

- βελτιώνει

- in

- αυξημένη

- βιομηχανία

- πληροφορίες

- εσωτερικός

- αντί

- Ενσωμάτωση

- ολοκλήρωση

- Intel

- ενδιαφέρον

- σε

- εισαγάγει

- απομονωμένος

- απομόνωση

- ζήτημα

- IT

- jpg

- στρώμα

- στρώματα

- σχέδιο

- ηγέτες

- Οδηγεί

- αριστερά

- γραμμή

- λογική

- off

- Χαμηλός

- κάνω

- χάρτες

- σύντροφος

- υλικό

- max-width

- Ενδέχεται..

- που αναφέρθηκαν

- Μέσο

- ενδέχεται να

- ελαχιστοποίηση

- μοντελοποίηση

- MOL

- Μονολιθικός

- περισσότερο

- κίνηση

- πολλαπλούς

- πρέπει

- απαραίτητος

- Ανάγκη

- που απαιτούνται

- δίκτυο

- Νέα

- επόμενη

- Όχι.

- σημείωση

- τώρα

- αριθμός

- of

- on

- μια φορά

- ONE

- βελτιστοποίηση

- Επιλογή

- Επιλογές

- or

- τάξη

- ΑΛΛΑ

- δικός μας

- έξω

- Ξεπεράστε

- σελίδα

- μέρος

- ιδιαίτερα

- επίδοση

- Πίσσα

- τοποθέτηση

- Πλάτων

- Πληροφορία δεδομένων Plato

- Πλάτωνα δεδομένα

- συν

- Σημείο

- πιθανώς

- Θέση

- δύναμη

- παρόν

- παρουσίαση

- παρουσιάζονται

- δώρα

- προηγούμενος

- προηγουμένως

- Pro

- διαδικασια μας

- Διεργασίες

- μεταποίηση

- Πρόοδος

- υποσχόμενος

- αποδεικνύει

- παρέχουν

- δημοσιεύθηκε

- καθαρώς

- αναλογία

- Διάβασε

- μείωση

- Μειωμένος

- μειώνει

- μείωση

- σχετικά

- επαναλαμβάνω

- απαιτούν

- Απαιτεί

- ανταποκρίνονται

- δεξιά

- δρομολόγηση

- Είπε

- Samsung

- SC

- απολέπιση

- Δεύτερος

- δείτε

- δει

- δείχνουν

- επίδειξη

- πλευρά

- Σήμα

- So

- μιλούν

- σωρός

- στοιβάζονται

- στοίβαξη

- Στοίβες

- πρότυπο

- Βήματα

- δομή

- μεταγενέστερος

- Στήριξη

- Πάρτε

- ομιλία

- Τεχνολογία

- ΑΝΑΠΤΥΞΗ ΤΕΧΝΟΛΟΓΙΑΣ

- από

- ότι

- Η

- τότε

- θερμικός

- αυτό

- φέτος

- σκέψη

- ώρα

- προς την

- κορυφή

- τροχιά

- μεταβαίνουν

- tsmc

- δύο

- Ενημέρωση

- Εναντίον

- κατακόρυφος

- κάθετα

- μέσω

- vs

- ήταν

- Τρόπος..

- we

- ΛΟΙΠΌΝ

- δυτικά

- Τι

- πότε

- ευρύτερο

- θα

- με

- χωρίς

- Εργασία

- εργαζόμενος

- θα

- γράφω

- γραπτή

- έτος

- εσείς

- zephyrnet