Κατά τη δεκαετία του 2010, τα οφέλη του νόμου του Μουρ άρχισαν να καταρρέουν. Ο νόμος του Moore έλεγε ότι η πυκνότητα των τρανζίστορ διπλασιαζόταν κάθε δύο χρόνια, το κόστος υπολογισμού θα συρρικνωθεί κατά ένα αντίστοιχο 50%. Η αλλαγή στο νόμο του Moore οφείλεται στην αυξημένη σχεδιαστική πολυπλοκότητα της εξέλιξης της δομής του τρανζίστορ από επίπεδες συσκευές, σε Finfets. Τα Finfets χρειάζονται πολλαπλά σχέδια για τη λιθογραφία για να επιτύχουν διαστάσεις συσκευών κάτω από κόμβους 20 nm.

Στις αρχές αυτής της δεκαετίας, οι υπολογιστικές ανάγκες έχουν εκραγεί, κυρίως λόγω του πολλαπλασιασμού των κέντρων δεδομένων και λόγω του όγκου των δεδομένων που παράγονται και επεξεργάζονται. Στην πραγματικότητα, η υιοθέτηση της Τεχνητής Νοημοσύνης (AI) και τεχνικών όπως η Μηχανική Μάθηση (ML) χρησιμοποιούνται πλέον για την επεξεργασία συνεχώς αυξανόμενων δεδομένων και έχει οδηγήσει σε διακομιστές να αυξάνουν σημαντικά την υπολογιστική τους χωρητικότητα.

Οι διακομιστές έχουν προσθέσει πολλούς περισσότερους πυρήνες CPU, έχουν ενσωματώσει μεγαλύτερες GPU που χρησιμοποιούνται αποκλειστικά για ML, δεν χρησιμοποιούνται πλέον για γραφικά και έχουν ενσωματώσει προσαρμοσμένους επιταχυντές ASIC AI ή συμπληρωματική, βασισμένη σε FPGA επεξεργασία AI. Τα πρώτα σχέδια τσιπ τεχνητής νοημοσύνης εφαρμόστηκαν χρησιμοποιώντας μεγαλύτερα μονολιθικά SoC, μερικά από τα οποία έφτασαν το όριο μεγέθους που επιβάλλει το πλέγμα, περίπου 700 mm2.

Σε αυτό το σημείο, ο διαχωρισμός σε ένα μικρότερο SoC συν διάφορα chiplet υπολογιστών και IO φαίνεται να είναι η σωστή λύση. Αρκετοί κατασκευαστές τσιπ, όπως η Intel, η AMD ή η Xilinx έχουν επιλέξει αυτήν την επιλογή για προϊόντα που βγαίνουν στην παραγωγή. Στην εξαιρετική λευκή βίβλο από τον Όμιλο Linley, «Τα Chiplets Gain Rapid Adoption: Why Big Chips Are Getting Small», αποδείχθηκε ότι αυτή η επιλογή οδηγεί σε καλύτερο κόστος σε σύγκριση με τα μονολιθικά SoC, λόγω του αντίκτυπου στην απόδοση των μεγαλύτερων.

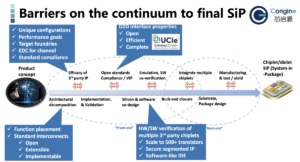

Ο κύριος αντίκτυπος αυτής της τάσης στους προμηθευτές IP είναι κυρίως στις λειτουργίες διασύνδεσης που χρησιμοποιούνται για τη σύνδεση SoC και chiplet. Σε αυτό το σημείο (3 τρίμηνο 2021), χρησιμοποιούνται πολλά πρωτόκολλα, με τη βιομηχανία να προσπαθεί να δημιουργήσει επίσημα πρότυπα για πολλά από αυτά.

Τα τρέχοντα κορυφαία πρότυπα D2D περιλαμβάνουν i) Advanced Interface Bus (AIB, AIB2) που αρχικά ορίστηκε από την Intel και τώρα προσφέρει δωρεάν χρήση, ii) High Bandwidth Memory (HBM) όπου οι βάσεις DRAM στοιβάζονται το ένα πάνω στο άλλο πάνω από έναν παρεμβολέα πυριτίου και συνδέονται με χρήση TSV, iii) Η υποομάδα Open Domain-Specific Architecture (ODSA), μια ομάδα βιομηχανίας, έχει ορίσει δύο άλλες διεπαφές, το Bunch of Wires (BoW) και το OpenHBI.

Ο ετερογενής σχεδιασμός chiplet μας επιτρέπει να στοχεύουμε διαφορετικές εφαρμογές ή τμήματα της αγοράς τροποποιώντας ή προσθέτοντας μόνο τα σχετικά chiplet διατηρώντας το υπόλοιπο σύστημα αμετάβλητο. Νέες εξελίξεις θα μπορούσαν να κυκλοφορήσουν πιο γρήγορα στην αγορά, με σημαντικά χαμηλότερες επενδύσεις, καθώς ο επανασχεδιασμός θα επηρεάσει μόνο το υπόστρωμα της συσκευασίας που χρησιμοποιείται για τη στέγαση των chiplets.

Για παράδειγμα, το υπολογιστικό chiplet μπορεί να επανασχεδιαστεί από TSMC 5nm σε TSMC 3nm για να ενσωματώσει μεγαλύτερη κρυφή μνήμη L1 ή πυρήνες CPU υψηλότερης απόδοσης, διατηρώντας παράλληλα το υπόλοιπο σύστημα αμετάβλητο. Στο αντίθετο άκρο του φάσματος, μόνο το chiplet που ενσωματώνει SerDes μπορεί να επανασχεδιαστεί για ταχύτερους ρυθμούς σε νέους κόμβους διεργασίας που προσφέρουν περισσότερο εύρος ζώνης IO για καλύτερη θέση στην αγορά.

Το Intel PVC είναι ένα τέλειο παράδειγμα ετερογενούς ολοκλήρωσης (διάφορα λειτουργικά chiplet, CPU, διακόπτης, κ.λπ.) που θα μπορούσαμε να ονομάσουμε κάθετη ενοποίηση, όταν ο ίδιος κατασκευαστής τσιπ κατέχει τα διάφορα εξαρτήματα chiplet (εκτός από συσκευές μνήμης).

Ο κατασκευαστής τσιπ που αναπτύσσει SoC για εφαρμογές υψηλής τεχνολογίας, όπως HPC, κέντρο δεδομένων, τεχνητή νοημοσύνη ή δικτύωση, είναι πιθανό να υιοθετήσει πρώιμες αρχιτεκτονικές chiplet. Συγκεκριμένες λειτουργίες, όπως SRAM για μεγαλύτερη κρυφή μνήμη L3 ή επιταχυντές AI, τα πρότυπα Ethernet, PCIe ή CXL θα πρέπει να είναι η πρώτη υποψήφια διεπαφή για σχέδια chiplet.

Όταν αυτοί οι πρώτοι χρήστες έχουν αποδείξει την εγκυρότητα των ετερογενών chiplet που αξιοποιούν πολλαπλά διαφορετικά επιχειρηματικά μοντέλα και προφανώς τη σκοπιμότητα κατασκευής για δοκιμή και συσκευασία, θα έχει δημιουργηθεί ένα οικοσύστημα που είναι κρίσιμο για την υποστήριξη αυτής της νέας τεχνολογίας. Σε αυτό το σημείο, μπορούμε να περιμένουμε μια ευρύτερη υιοθέτηση της αγοράς, όχι μόνο για εφαρμογές υψηλής απόδοσης.

Θα μπορούσαμε να φανταστούμε ότι τα ετερογενή προϊόντα μπορούν να προχωρήσουν περισσότερο, εάν ένας κατασκευαστής τσιπ λανσάρει στην αγορά ένα σύστημα κατασκευασμένο από διάφορα chiplet που στοχεύουν τη λειτουργικότητα υπολογιστών και IO. Αυτή η προσέγγιση καθιστά υποχρεωτική τη σύγκλιση σε ένα πρωτόκολλο D2D, καθώς ένας προμηθευτής IP που προσφέρει chiplet με εσωτερικό πρωτόκολλο D2D δεν είναι ελκυστικός για τη βιομηχανία.

Μια αναλογία με αυτό, είναι το κτίριο SoC στη δεκαετία του 2000, όπου οι εταιρείες ημιαγωγών μεταβαίνουν στην ενσωμάτωση διαφόρων IP σχεδιασμού που προέρχονται από διαφορετικές πηγές. Οι προμηθευτές IP του 2000 θα γίνουν αναπόφευκτα οι προμηθευτές chiplet του 2020. Για ορισμένες λειτουργίες, όπως προηγμένα SerDes ή σύνθετα πρωτόκολλα, όπως PCIe, Ethernet ή CXL, οι προμηθευτές IP έχουν την καλύτερη τεχνογνωσία για την εφαρμογή τους σε πυρίτιο.

Για σύνθετη IP σχεδίασης, ακόμη και αν έχει εκτελεστεί επαλήθευση προσομοίωσης πριν από την αποστολή σε πελάτες, οι πωλητές πρέπει να επικυρώσουν την IP σε πυρίτιο για να εγγυηθούν την απόδοση. Για την ψηφιακή IP, η λειτουργία μπορεί να εφαρμοστεί σε FPGA επειδή είναι ταχύτερη και πολύ λιγότερο δαπανηρή από την κατασκευή ενός τσιπ δοκιμής. Για IP σήματος μεικτών, όπως ένα PHY που βασίζεται σε SerDes, οι πωλητές επιλέγουν την επιλογή Test Chip (TC) που τους επιτρέπει να χαρακτηρίζουν την IP σε πυρίτιο πριν την αποστολή στον πελάτη.

Παρόλο που ένα chiplet δεν είναι απλώς ένα TC, επειδή θα ελεγχθεί εκτενώς και θα πιστοποιηθεί πριν χρησιμοποιηθεί στο πεδίο, ο όγκος της σταδιακής εργασίας που πρέπει να γίνει από τον πωλητή για την ανάπτυξη ενός chiplet παραγωγής είναι πολύ μικρότερος. Με άλλα λόγια, ο πωλητής IP είναι ο καλύτερος σε θέση να απελευθερώσει γρήγορα ένα chiplet κατασκευασμένο από τη δική του IP και να προσφέρει το καλύτερο δυνατό TTM και να ελαχιστοποιήσει τον κίνδυνο.

Το επιχειρηματικό μοντέλο για ετερογενή ενοποίηση είναι υπέρ της κατασκευής διαφόρων chiplet από τον σχετικό προμηθευτή IP (π.χ. ARM για chiplet CPU που βασίζονται σε ARM, Si-Five για υπολογιστικά chiplet με βάση το Risc-V και Alphawave για chiplet SerDes υψηλής ταχύτητας) είναι κάτοχοι της IP Design.

Τίποτα από αυτά δεν εμποδίζει τους κατασκευαστές τσιπ να σχεδιάσουν τα δικά τους chiplet και να προμηθεύουν σύνθετες διευθύνσεις IP σχεδίασης για να προστατεύσουν τις μοναδικές αρχιτεκτονικές τους ή να εφαρμόσουν οικιακές διασυνδέσεις. Παρόμοια με το SoC Design IP στη δεκαετία του 2000, η απόφαση αγοράς ή λήψης chiplet θα σταθμίζεται μεταξύ της προστασίας βασικών ικανοτήτων και της προμήθειας μη διαφοροποιητικών λειτουργιών.

Έχουμε δει ότι η ιστορική και σύγχρονη ανάπτυξη των επιχειρήσεων Σχεδιασμού IP από τη δεκαετία του 2000 έχει διατηρηθεί από τη συνεχή υιοθέτηση της εξωτερικής προμήθειας. Και τα δύο μοντέλα θα συνυπάρχουν (το τσιπετ έχει σχεδιαστεί εσωτερικά ή από έναν προμηθευτή IP), αλλά η ιστορία έχει δείξει ότι η απόφαση αγοράς τελικά παίρνει τη σημασία.

Υπάρχει πλέον συναίνεση στον κλάδο ότι μια μανιακή εστίαση στην επίτευξη του νόμου του Moore δεν ισχύει πλέον για κόμβους προηγμένης τεχνολογίας, π.χ. 7 nm και κάτω. Η ενσωμάτωση chip εξακολουθεί να συμβαίνει, με περισσότερα τρανζίστορ να προστίθενται ανά τετραγωνικό χιλιοστό σε κάθε κόμβο νέας τεχνολογίας. Ωστόσο, το κόστος ανά τρανζίστορ αυξάνεται επίσης με κάθε νέο κόμβο.

Η τεχνολογία Chiplet είναι μια βασική πρωτοβουλία για την αύξηση της ενσωμάτωσης για το κύριο SoC, ενώ χρησιμοποιούνται παλαιότεροι κόμβοι για άλλες λειτουργίες. Αυτή η υβριδική στρατηγική μειώνει τόσο το κόστος όσο και τον κίνδυνο σχεδιασμού που σχετίζεται με την ενσωμάτωση άλλων IP σχεδίασης απευθείας στο κύριο SoC.

Η IPnest πιστεύει ότι αυτή η τάση θα έχει δύο βασικά αποτελέσματα στην επιχείρηση IP διεπαφής, το ένα θα είναι η ισχυρή αύξηση των εσόδων από D2D IP σύντομα (2021-2025) και το άλλο είναι η δημιουργία της ετερογενούς αγοράς chiplet για την αύξηση του πυριτίου υψηλής τεχνολογίας αγορά IP.

Αυτή η αγορά αναμένεται να αποτελείται από σύνθετες λειτουργίες πρωτοκόλλων όπως PCIe, CXL ή Ethernet. Οι προμηθευτές IP που παρέχουν IP διεπαφής ενσωματωμένη σε SoC I/O (USB, HDMI, DP, MIPI, κ.λπ.) ενδέχεται να αποφασίσουν να παραδώσουν chiplet I/O.

Οι άλλες κατηγορίες IP που επηρεάζονται από αυτήν την επανάσταση θα είναι οι προμηθευτές IP μεταγλωττιστή μνήμης SRAM, για την προσωρινή μνήμη L3. Από τη φύση του, το μέγεθος της κρυφής μνήμης αναμένεται να ποικίλλει ανάλογα με τον επεξεργαστή. Παρόλα αυτά, η σχεδίαση chiplet cache L3 μπορεί να είναι ένας τρόπος για τον προμηθευτή IP να αυξήσει τα έσοδα του Design IP προσφέροντας έναν νέο τύπο προϊόντος.

Επίσης, η κατηγορία IP NVM μπορεί να επηρεαστεί θετικά, καθώς η IP NVM δεν είναι πλέον ενσωματωμένη σε SoC που έχουν σχεδιαστεί σε προηγμένους κόμβους διεργασιών. Θα ήταν ένας τρόπος για τους προμηθευτές IP NVM να δημιουργήσουν νέες επιχειρήσεις προσφέροντας chiplet.

Πιστεύουμε ότι τα chiplet επιταχυντών FPGA και AI θα είναι μια νέα πηγή εσόδων για τους κατασκευαστές τσιπ ASSP, αλλά δεν πιστεύουμε ότι μπορούν να ταξινομηθούν αυστηρά ως προμηθευτές IP.

Εάν οι προμηθευτές IP Interface θα είναι σημαντικοί παράγοντες σε αυτήν την επανάσταση του πυριτίου, τα χυτήρια πυριτίου που απευθύνονται στους πιο προηγμένους κόμβους όπως η TSMC και η Samsung θα παίξουν επίσης βασικό ρόλο. Δεν πιστεύουμε ότι τα χυτήρια θα σχεδιάσουν chiplet, αλλά θα μπορούσαν να λάβουν την απόφαση να υποστηρίξουν προμηθευτές IP και να τους ωθήσουν να σχεδιάσουν chiplet που θα χρησιμοποιούνται με SoC στα 3nm, όπως κάνουν σήμερα όταν υποστηρίζουν προηγμένους προμηθευτές IP για την εμπορία των SerDes τους υψηλής ποιότητας ως σκληρή IP στα 7nm και 5nm.

Η πρόσφατη μετάβαση της Intel στο 3rd Τα party foundries αναμένεται επίσης να αξιοποιήσουν IP τρίτων, καθώς και την ετερογενή υιοθέτηση chiplet από βαρέων βαρών ημιαγωγών. Σε αυτήν την περίπτωση, δεν υπάρχει αμφιβολία ότι οι υπερκλιμακωτές συσκευές όπως η Microsoft, η Amazon και η Google θα υιοθετήσουν επίσης αρχιτεκτονικές chiplet… εάν δεν προηγούνται της Intel στην υιοθέτηση chiplet.

By Έρικ Εστέβ (PhD.) Αναλυτής, Ιδιοκτήτης IPnest

Μοιραστείτε αυτήν την ανάρτηση μέσω: Πηγή: https://semiwiki.com/semiconductor-services/ipnest/303790-chiplet-are-you-ready-for-next-semiconductor-revolution/

- 2021

- επιταχυντής

- επιταχυντές

- Υιοθεσία

- Προηγμένη Τεχνολογία

- AI

- Επιτρέποντας

- Amazon

- AMD

- αναλυτής

- εφαρμογές

- αρχιτεκτονική

- ARM

- τεχνητή νοημοσύνη

- Τεχνητή νοημοσύνη (AI)

- ASIC

- ΚΑΛΎΤΕΡΟΣ

- χτίζω

- Κτίριο

- τσαμπί

- λεωφορείο

- επιχείρηση

- επιχειρηματικό μοντέλο

- αγορά

- κλήση

- Χωρητικότητα

- αλλαγή

- τσιπ

- τσιπ

- ερχομός

- Εταιρείες

- Υπολογίστε

- χρήση υπολογιστή

- Ομοφωνία

- Δικαστικά έξοδα

- Πελάτες

- ημερομηνία

- παράδοση

- Υπηρεσίες

- ανάπτυξη

- Συσκευές

- ψηφιακό

- Νωρίς

- πρώιμες υιοθεσίες

- οικοσύστημα

- κ.λπ.

- εξέλιξη

- Όνομα

- Συγκέντρωση

- FPGA

- Δωρεάν

- λειτουργία

- GPU

- Group

- Μεγαλώνοντας

- Ανάπτυξη

- Ψηλά

- ιστορία

- Σπίτι

- HTTPS

- Υβριδικό

- Επίπτωση

- Αυξάνουν

- βιομηχανία

- Πρωτοβουλία

- ολοκλήρωση

- Intel

- Νοημοσύνη

- επένδυση

- IP

- IT

- τήρηση

- Κλειδί

- ξεκινήσει

- Νόμος

- που οδηγεί

- μάθηση

- Led

- Μόχλευση

- LINK

- μάθηση μηχανής

- μεγάλες

- κατασκευαστής

- Κατασκευή

- κατασκευής

- αγορά

- Microsoft

- ML

- μοντέλο

- δικτύωσης

- καινούργιο προϊόν

- κόμβων

- προσφορά

- προσφορά

- ανοίξτε

- Επιλογή

- ΑΛΛΑ

- ιδιοκτήτης

- συσκευασία

- Χαρτί

- επίδοση

- Προϊόν

- παραγωγή

- Προϊόντα

- προστασία

- προστασία

- Τιμές

- επανασχεδιασμό

- ΠΕΡΙΦΕΡΕΙΑ

- Κίνδυνος

- τρέξιμο

- Samsung

- ημιαγωγός

- Shipping

- προσομοίωση

- Μέγεθος

- πρότυπα

- Στρατηγική

- υποστήριξη

- διακόπτης

- σύστημα

- στόχος

- τεχνικές

- Τεχνολογία

- δοκιμή

- κορυφή

- us

- usb

- πωλητές

- Επαλήθευση

- λευκό χαρτί

- λόγια

- Εργασία

- χρόνια

- Βελτιστοποίηση