Νωρίτερα έγραψα στο blog Λειτουργική επαλήθευση IC και ASIC, οπότε σήμερα είναι ώρα να το ολοκληρώσουμε με την κατάσταση της επαλήθευσης λειτουργίας FPGA. Η Wilson Research Group συντάσσει μια έκθεση FPGA κάθε δύο χρόνια από το 2018, επομένως είναι η τρίτη φορά που επικεντρώνεται σε αυτό το τμήμα σχεδιασμού. Στα 5.8 δισεκατομμύρια δολάρια η αγορά FPGA είναι αρκετά μεγάλη και προβλέπεται να αυξηθεί στα 8.1 δισεκατομμύρια δολάρια έως το 2025. Τα FPGA ξεκίνησαν το 1984 με περιορισμένη χωρητικότητα πύλης και τώρα έχουν αυξηθεί ώστε να περιλαμβάνουν εκατομμύρια πύλες, επεξεργαστές και τυποποιημένα πρωτόκολλα δεδομένων.

Οι εφαρμογές χαμηλού όγκου επωφελούνται από το NRE των συσκευών FPGA και οι μηχανικοί μπορούν να πρωτοτυπήσουν γρήγορα τα σχέδιά τους επαληθεύοντας και επικυρώνοντας με ταχύτητα. Τα FPGA περιλαμβάνουν πλέον επεξεργαστές, όπως: Xilinx Zynq UltraSCALE, Intel Stratix, Μικροτσίπ SmartFusion. Από τους 980 συμμετέχοντες στη μελέτη λειτουργικής επαλήθευσης, τα στυλ σχεδίασης FPGA και προγραμματιζόμενου SoC FPGA είναι τα πιο δημοφιλή.

Καθώς το μέγεθος των FPGA έχει αυξηθεί πρόσφατα, η πιθανότητα κυκλοφορίας παραγωγής χωρίς σφάλματα μειώθηκε σε μόλις 17%, που είναι ακόμη χειρότερο από το 30% των έργων IC και ASIC για το σωστό πρώτο πυρίτιο. Σαφώς, χρειαζόμαστε καλύτερη λειτουργική επαλήθευση για πολύπλοκα συστήματα FPGA.

Οι τύποι σφαλμάτων που εντοπίζονται στην παραγωγή εμπίπτουν σε διάφορες κατηγορίες:

- 53% – Λογική ή Λειτουργική

- 31% – Υλικολογισμικό

- 29% – Ρολόι

- 28% – Χρονισμός, διαδρομή πολύ αργή

- 21% – Χρονισμός, διαδρομή πολύ γρήγορη

- 18% – Διεπαφή μικτού σήματος

- 9% – Χαρακτηριστικό ασφαλείας

- 8% – Δυνατότητα ασφαλείας

Μεγεθύνοντας τη μεγαλύτερη κατηγορία αποτυχίας, λογική ή λειτουργική, υπάρχουν πέντε βασικές αιτίες.

Τα έργα FGPA ως επί το πλείστον δεν ολοκληρώθηκαν εγκαίρως, και πάλι λόγω του μεγαλύτερου μεγέθους των συστημάτων, της πολυπλοκότητας της λογικής και ακόμη και των μεθόδων επαλήθευσης που χρησιμοποιούνται.

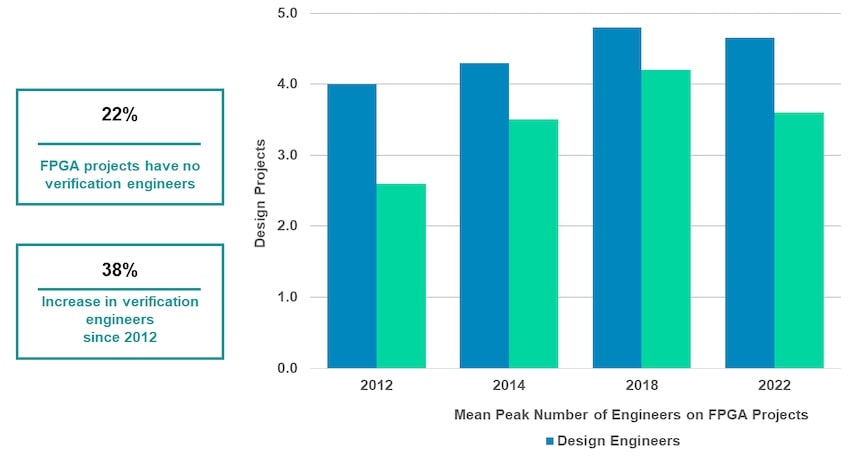

Οι μηχανικοί σε μια ομάδα FPGA μπορούν να έχουν διακριτούς τίτλους όπως μηχανικός σχεδίασης ή μηχανικός επαλήθευσης, ωστόσο στο 22% των έργων δεν υπήρχαν μηχανικοί επαλήθευσης - που σημαίνει ότι οι μηχανικοί σχεδιασμού έκαναν διπλό καθήκον και επαλήθευσαν τη δική τους IP. Τα τελευταία 10 χρόνια έχει σημειωθεί μια αύξηση 38% στον αριθμό των μηχανικών επαλήθευσης σε ένα έργο FPGA, οπότε αυτή είναι η πρόοδος προς την παραγωγή χωρίς σφάλματα.

Οι μηχανικοί επαλήθευσης σε έργα FPGA αφιέρωσαν τον περισσότερο χρόνο τους σε εργασίες εντοπισμού σφαλμάτων στο 47%:

- 47% – Εντοπισμός σφαλμάτων

- 19% – Δημιουργία προσομοίωσης δοκιμής και εκτέλεσης

- 17% – Ανάπτυξη Testbench

- 11% – Προγραμματισμός δοκιμών

- 6% – Άλλο

Ο αριθμός των ενσωματωμένων επεξεργαστών αυξάνεται σταθερά με την πάροδο του χρόνου, επομένως το 65% των σχεδίων FPGA έχουν τώρα έναν ή περισσότερους πυρήνες επεξεργαστών, αυξάνοντας τον βαθμό επαλήθευσης μεταξύ διεπαφών υλικού και λογισμικού. και διαχείριση δικτύων on-chip.

Ο πάντα δημοφιλής επεξεργαστής RISC-V είναι ενσωματωμένος στο 22% των FPGA και οι επιταχυντές AI χρησιμοποιούνται στο 23% των έργων. Υπάρχουν 3-4 μέσος αριθμός τομέων ρολογιού που χρησιμοποιούνται σε FPGA και απαιτούν προσομοιώσεις χρονισμού σε επίπεδο πύλης για επαλήθευση, συν τη χρήση στατικών εργαλείων Clock Domain Crossing (CDC) για επαλήθευση.

Τα χαρακτηριστικά ασφαλείας προστίθενται στο 49% των σχεδίων FPGA για τη διατήρηση ευαίσθητων δεδομένων, συν το 42% των έργων FPGA συμμορφώνονται με τα κρίσιμα για την ασφάλεια πρότυπα ή οδηγίες. Στο SemiWiki έχουμε συχνά γράψει blog ISO 26262 και DO-254 πρότυπα. Οι προσπάθειες σχεδιασμού Λειτουργικής Ασφάλειας (FuSa) απαιτούν από 25% έως 50% του συνολικού χρόνου του έργου.

Οι τρεις κορυφαίες γλώσσες επαλήθευσης είναι η VHDL, η SystemVerilog και η Verilog. αλλά επίσης παρατηρήστε τα πρόσφατα άλματα στις γλώσσες Python και C/C++.

Οι πιο δημοφιλείς μεθοδολογίες FPGA και βασικές βιβλιοθήκες δοκιμαστικής βάσης είναι: Accellera UVM, OSVVM και UVVM. Βασισμένο σε Python κόκοτμπ προστέθηκε ακόμη και ως νέα κατηγορία για το 2022.

Οι γλώσσες διεκδίκησης οδηγούνται από το SystemVerilog Assertions (SVA) με ποσοστό 45%, ακολουθούμενο από το Accellera Open Verification Library (OVL) με 13% και το PSL με 11%. Τα σχέδια FPGA μπορεί να συνδυάζουν VHDL για σχεδιασμό RTL μαζί με SVA για ισχυρισμούς.

Ο επίσημος έλεγχος ιδιοκτησίας αυξάνεται μεταξύ των έργων FPGA, ειδικά καθώς έχουν εισαχθεί περισσότερες αυτόματες επίσημες εφαρμογές από προμηθευτές EDA.

Οι προσεγγίσεις επαλήθευσης που βασίζονται σε προσομοίωση τα τελευταία 10 χρόνια δείχνουν σταθερή υιοθέτηση, που παρατίθενται με σειρά συνάφειας: Κάλυψη κώδικα, λειτουργική κάλυψη, ισχυρισμοί, περιορισμένη τυχαία.

Χαρακτηριστικά

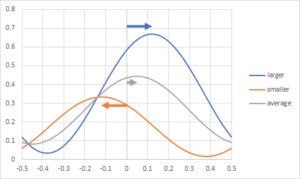

Ο χαμηλός αριθμός 17% χωρίς σφάλματα για έργα FPGA το 2022 που τέθηκε σε παραγωγή ήταν ο πιο εκπληκτικός αριθμός για μένα, καθώς η προσπάθεια ανάκλησης ή επαναπρογραμματισμού μιας συσκευής στο πεδίο είναι δαπανηρή και χρονοβόρα για διόρθωση. Μια πιο ισχυρή προσέγγιση λειτουργικής επαλήθευσης θα πρέπει να οδηγήσει σε λιγότερες διαφυγές σφαλμάτων στην παραγωγή και η διαίρεση των συμμετεχόντων στη μελέτη σε δύο ομάδες δείχνει το όφελος.

Διαβάστε το πλήρες Λευκή Βίβλος 18 σελίδων εδώ.

Σχετικά ιστολόγια

Μοιραστείτε αυτήν την ανάρτηση μέσω:

- SEO Powered Content & PR Distribution. Ενισχύστε σήμερα.

- Platoblockchain. Web3 Metaverse Intelligence. Ενισχύθηκε η γνώση. Πρόσβαση εδώ.

- πηγή: https://semiwiki.com/eda/324651-the-state-of-fpga-functional-verification/

- 1

- 10

- 2018

- 2022

- a

- Σχετικά με εμάς

- επιταχυντές

- προστιθέμενη

- εμμένω

- Υιοθεσία

- AI

- μεταξύ των

- ποσό

- και

- εφαρμογές

- πλησιάζω

- προσεγγίσεις

- εφαρμογές

- ASIC

- Αυτόματο

- μέσος

- είναι

- όφελος

- Καλύτερα

- μεταξύ

- Δισεκατομμύριο

- Έντομο

- σφάλματα

- Χωρητικότητα

- κατηγορίες

- κατηγορία

- Αιτία

- προκαλούνται

- αίτια

- CDC

- ευκαιρία

- έλεγχος

- σαφώς

- ρολόι

- κωδικός

- συνδυασμός

- πλήρης

- συγκρότημα

- περίπλοκο

- κάλυψη

- δημιουργία

- κρίσιμης

- ημερομηνία

- Υπηρεσίες

- σχέδια

- συσκευή

- Συσκευές

- DID

- διακριτή

- τομέα

- domains

- έπεσε

- προσπάθεια

- προσπάθειες

- ενσωματωμένο

- μηχανικός

- Μηχανικοί

- ειδικά

- Even

- Κάθε

- ακριβά

- Αποτυχία

- Πτώση

- Χαρακτηριστικά

- πεδίο

- Όνομα

- επικεντρώθηκε

- ακολουθείται

- επίσημος

- Βρέθηκαν

- FPGA

- από

- λειτουργικός

- Πύλες

- Group

- Ομάδα

- Grow

- Μεγαλώνοντας

- καλλιεργούνται

- κατευθυντήριων γραμμών

- υλικού

- κρατήστε

- HTML

- HTTPS

- in

- περιλαμβάνουν

- Αυξάνουν

- αυξημένη

- αύξηση

- Intel

- διεπαφές

- εισήγαγε

- IP

- IT

- άλματα

- Γλώσσες

- μεγαλύτερος

- μεγαλύτερη

- οδηγήσει

- Led

- βιβλιοθήκες

- Βιβλιοθήκη

- Περιωρισμένος

- Εισηγμένες

- Χαμηλός

- που

- διαχείριση

- αγορά

- max-width

- νόημα

- μεθοδολογίες

- μέθοδοι

- εκατομμύρια

- περισσότερο

- πλέον

- Δημοφιλέστερα

- Ανάγκη

- δίκτυα

- Νέα

- αριθμός

- ONE

- ανοίξτε

- τάξη

- φόρμες

- δική

- Χαρτί

- συμμετέχοντες

- Το παρελθόν

- μονοπάτι

- Πλάτων

- Πληροφορία δεδομένων Plato

- Πλάτωνα δεδομένα

- συν

- Δημοφιλής

- Θέση

- Επεξεργαστής

- επεξεργαστές

- παραγωγή

- Πρόοδος

- σχέδιο

- έργα

- περιουσία

- πρωτόκολλα

- πρωτότυπο

- Python

- γρήγορα

- τυχαίος

- πρόσφατος

- πρόσφατα

- απελευθερώνουν

- συνάφεια

- αναφέρουν

- απαιτούν

- έρευνα

- ερευνητική ομάδα

- εύρωστος

- ρίζα

- γύρος

- τρέξιμο

- Ασφάλεια

- ασφάλεια

- τμήμα

- ευαίσθητος

- διάφοροι

- θα πρέπει να

- δείχνουν

- Δείχνει

- Siemens

- Πυρίτιο

- αφού

- ευμεγέθης

- Μέγεθος

- So

- λογισμικό

- ταχύτητα

- πέρασε

- πρότυπα

- ξεκίνησε

- Κατάσταση

- σταθερός

- Μελέτη

- εκπληκτικός

- συστήματα

- Πάρτε

- εργασίες

- τεχνικές

- δοκιμή

- Η

- Το κράτος

- τους

- Τρίτος

- τρία

- ώρα

- συγχρονισμός

- τίτλους

- προς την

- σήμερα

- πολύ

- εργαλεία

- κορυφή

- προς

- τύποι

- χρήση

- πωλητές

- Επαλήθευση

- επαληθεύεται

- επαληθεύοντας

- μέσω

- τόμος

- Ποιό

- άσπρο

- λευκό χαρτί

- Wilson

- χρόνια

- zephyrnet