Αν δούμε την επέκταση της βιομηχανίας ημιαγωγών τα τελευταία 25 χρόνια, η υιοθέτηση της IP σχεδίασης σε κάθε εφαρμογή φαίνεται να είναι ένας από τους σημαντικότερους παράγοντες επιτυχίας, με απίστευτη ανάπτυξη τεχνολογίας πυριτίου με συντελεστή x100, από 250nm το 2018 σε 3nm (εάν όχι 2nm) το 2023. Προβλέπουμε ότι η μετάβαση στην αρχιτεκτονική βασισμένη σε chiplet θα παίξει σύντομα τον ίδιο ρόλο που έπαιξε η αρχιτεκτονική που βασίζεται σε τσιπ SoC και η μαζική χρήση της IP σχεδίασης τη δεκαετία του 2000.

Το ερώτημα είναι πώς να προβλέψετε με ακρίβεια το χρονοδιάγραμμα υιοθέτησης των chiplet και ποιοι θα είναι οι βασικοί παράγοντες για αυτήν την επανάσταση. Θα δούμε αν η διάχυση της θεωρίας της καινοτομίας μπορεί να είναι χρήσιμη για να τελειοποιήσουμε μια πρόβλεψη, να καθορίσουμε ποιος τύπος εφαρμογής θα είναι ο οδηγός. Οι τυπικές προδιαγραφές πρωτοκόλλου διασύνδεσης chip-to-chip που επιτρέπουν τη γρήγορη υιοθέτηση από τη βιομηχανία, η γρήγορη οδήγηση εφαρμογών όπως το IA ή ο επεξεργαστής εφαρμογών smartphone φαίνεται να είναι ο κορυφαίος παράγοντας, αλλά η αποτελεσματικότητα των εργαλείων EDA ή η συσκευασία νέων τεχνολογιών και η αποκλειστική δημιουργία fab, μεταξύ άλλων, είναι σίγουρα βασικά.

Εισαγωγή: εμφάνιση της τεχνολογίας chiplet

Κατά τη δεκαετία του 2010, τα οφέλη του νόμου του Μουρ άρχισαν να καταρρέουν. Ο νόμος του Moore έλεγε ότι η πυκνότητα των τρανζίστορ διπλασιαζόταν κάθε δύο χρόνια, το κόστος υπολογισμού θα συρρικνωθεί κατά ένα αντίστοιχο 50%. Η αλλαγή στο νόμο του Moore οφείλεται στην αυξημένη σχεδιαστική πολυπλοκότητα της εξέλιξης της δομής του τρανζίστορ από επίπεδες συσκευές, σε Finfets. Τα Finfets χρειάζονται πολλαπλά σχέδια για τη λιθογραφία για να επιτύχουν διαστάσεις συσκευών κάτω από κόμβους 20 nm.

Στο τέλος αυτής της δεκαετίας, οι υπολογιστικές ανάγκες έχουν εκραγεί, κυρίως λόγω του πολλαπλασιασμού των κέντρων δεδομένων και λόγω του όγκου των δεδομένων που παράγονται και επεξεργάζονται. Στην πραγματικότητα, η υιοθέτηση της Τεχνητής Νοημοσύνης (AI) και τεχνικών όπως η Μηχανική Μάθηση (ML) χρησιμοποιούνται πλέον για την επεξεργασία συνεχώς αυξανόμενων δεδομένων και έχει οδηγήσει σε διακομιστές να αυξάνουν σημαντικά την υπολογιστική τους χωρητικότητα. Οι διακομιστές έχουν προσθέσει πολλούς περισσότερους πυρήνες CPU, έχουν ενσωματώσει μεγαλύτερες GPU που χρησιμοποιούνται αποκλειστικά για ML, δεν χρησιμοποιούνται πλέον για γραφικά και έχουν ενσωματώσει προσαρμοσμένους επιταχυντές ASIC AI ή συμπληρωματική, βασισμένη σε FPGA επεξεργασία AI. Τα πρώτα σχέδια τσιπ τεχνητής νοημοσύνης εφαρμόστηκαν χρησιμοποιώντας μεγαλύτερα μονολιθικά SoC, μερικά από τα οποία έφτασαν το όριο μεγέθους που επιβάλλει το πλέγμα, περίπου 700 mm2.

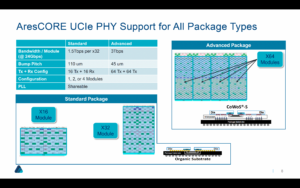

Σε αυτό το σημείο, ο διαχωρισμός σε ένα μικρότερο SoC συν διάφορα chiplet υπολογιστών και IO φαίνεται να είναι η σωστή λύση. Αρκετοί κατασκευαστές τσιπ, όπως η Intel, η AMD ή η Xilinx έχουν επιλέξει αυτήν την επιλογή για προϊόντα που βγαίνουν στην παραγωγή. Στην εξαιρετική λευκή βίβλο από τον Όμιλο Linley, «Τα Chiplets Gain Rapid Adoption: Why Big Chips Are Getting Small», αποδείχθηκε ότι αυτή η επιλογή οδηγεί σε καλύτερο κόστος σε σύγκριση με τα μονολιθικά SoC, λόγω του αντίκτυπου στην απόδοση των μεγαλύτερων. Αυτοί οι κατασκευαστές τσιπ έχουν σχεδιάσει ομοιογενή chiplet, αλλά η εμφάνιση και η υιοθέτηση προτύπων διασύνδεσης όπως το Universal Chiplet Interconnect Express (UCIe) IP διευκολύνει την υιοθέτηση ετερογενών chiplet.

Η εξέλιξη των νεότερων, ταχύτερων προτύπων πρωτοκόλλου επιταχύνεται καθώς η βιομηχανία συνεχίζει να ζητά υψηλότερες επιδόσεις. Δυστυχώς, τα διάφορα πρότυπα δεν συγχρονίζονται από έναν μόνο οργανισμό. Τα νέα πρότυπα PCIe μπορούν να έρθουν ένα χρόνο (ή περισσότερο) νωρίτερα ή αργότερα από το νέο πρότυπο πρωτοκόλλου Ethernet. Η χρήση ετερογενούς ενοποίησης επιτρέπει στους παρόχους πυριτίου να προσαρμοστούν στην ταχέως μεταβαλλόμενη αγορά αλλάζοντας μόνο τη σχεδίαση του σχετικού chiplet. Λαμβάνοντας υπόψη ότι η κατασκευή προηγμένου σχεδιασμού SoC απαιτεί τεράστιες κεφαλαιουχικές δαπάνες για κόμβους διεργασίας 5nm, 4nm ή 3nm, ο αντίκτυπος των αρχιτεκτονικών chiplet είναι τεράστιος για την προώθηση της μελλοντικής καινοτομίας στον χώρο των ημιαγωγών.

Ο ετερογενής σχεδιασμός chiplet μας επιτρέπει να στοχεύουμε διαφορετικές εφαρμογές ή τμήματα της αγοράς τροποποιώντας ή προσθέτοντας μόνο τα σχετικά chiplet διατηρώντας το υπόλοιπο σύστημα αμετάβλητο. Νέες εξελίξεις θα μπορούσαν να κυκλοφορήσουν πιο γρήγορα στην αγορά, με σημαντικά χαμηλότερες επενδύσεις, καθώς ο επανασχεδιασμός θα επηρεάσει μόνο το υπόστρωμα της συσκευασίας που χρησιμοποιείται για τη στέγαση των chiplets. Για παράδειγμα, το υπολογιστικό chiplet μπορεί να επανασχεδιαστεί από TSMC 5nm σε TSMC 3nm για να ενσωματώσει μεγαλύτερη κρυφή μνήμη L1 ή CPU υψηλότερης απόδοσης ή αριθμό πυρήνων CPU, διατηρώντας ταυτόχρονα το υπόλοιπο σύστημα αμετάβλητο. Οι SerDes που ενσωματώνουν chiplet μπορούν να επανασχεδιαστούν για ταχύτερους ρυθμούς σε νέους κόμβους διεργασιών που προσφέρουν περισσότερο εύρος ζώνης IO για καλύτερη θέση στην αγορά.

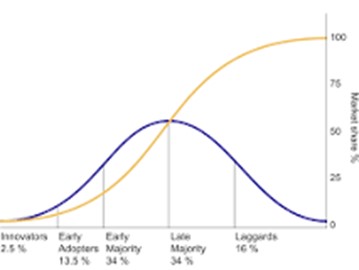

Η χρήση ετερογενούς chiplet θα προσφέρει καλύτερο Time-to-Market (TTM) κατά την ενημέρωση του συστήματος, επαναχρησιμοποιώντας το τμήμα του συστήματος χωρίς αλλαγή εάν έχει σχεδιαστεί σε chiplet. Αυτός θα είναι επίσης ένας τρόπος για να ελαχιστοποιήσετε το κόστος όταν διατηρείτε κάποιο λειτουργικό chiplet σε λιγότερο προηγμένους κόμβους, φθηνότερο από τους πιο προηγμένους. Αλλά το κύριο ερώτημα είναι να προβλέψουμε πότε η τεχνολογία chiplet θα δημιουργήσει ένα σημαντικό τμήμα της αγοράς ημιαγωγών; Θα εξετάσουμε το ιστορικό υιοθέτησης IP καθώς το chiplet και το IP είναι παρόμοια, και τα δύο πρέπει να σπάσουν το σύνδρομο NIH για να επιτύχουν. Θα εξαγάγουμε τις κύριες αιτίες της υιοθέτησης των chiplet και θα δημιουργήσουμε μια πρόβλεψη, χρησιμοποιώντας τη θεωρία καινοτομίας και την καθορισμένη κατηγορία (Innovators, Early Adopters, κ.λπ. βλ. Εικόνα παρακάτω).

Θα εξετάσουμε την υιοθέτηση IP CPU της ARM από το 1991 έως το 2018 και το ιστορικό υιοθέτησης IP από το 1995 έως το 2027 και θα ελέγξουμε πώς αυτό το ποσοστό υιοθέτησης συνάδει με τη Θεωρία Καινοτομίας.

Θα εξηγήσουμε γιατί θα ενισχυθεί η υιοθέτηση chiplet, εξετάζοντας τους λόγους που σχετίζονται με την τεχνολογία και το μάρκετινγκ:

- Από SoC που βασίζεται σε IP έως σύστημα που βασίζεται σε chiplet

- Διαλειτουργικότητα, χάρη στο προτιμώμενο πρότυπο πρωτοκόλλου διασύνδεσης chiplet

- Εξήγηση γιατί η IP διεπαφής προηγμένης τεχνολογίας είναι το κλειδί για την υιοθέτηση Chiplet

- Προκλήσεις που σχετίζονται με το σχεδιασμό προς επίλυση.

- Τελευταίο αλλά εξίσου σημαντικό, επένδυση από χυτήριο

Τέλος, μπορούμε να δημιουργήσουμε μια δοκιμαστική πρόβλεψη υιοθέτησης chiplet, βασισμένη στη θεωρία της καινοτομίας. Απλώς για να αναφέρουμε, ο κλάδος μόλις κινήθηκε στη φάση των «Πρώτων υιοθέτησης», βλέποντας πολλούς προμηθευτές IP και chiplet που εξυπηρετούν HPC και AI.

Αν κατεβάσετε το λευκό χαρτί, θα απολαύσετε με όλο το κείμενο και πολλές εικόνες, μερικές από τις οποίες δημιουργήθηκαν αποκλειστικά για αυτό το έργο.

By Έρικ Εστέβ (PhD.) Αναλυτής, Ιδιοκτήτης IPnest

Η Alphawave υποστήριξε τη δημιουργία αυτής της λευκής βίβλου, αλλά οι απόψεις και η ανάλυση είναι του συγγραφέα. Το άρθρο μπορείτε να βρείτε εδώ:

https://awavesemi.com/resource/will-chiplet-adoption-to-mimic-ip-adoption/

Διαβάστε επίσης:

Συστήματα διαχωρισμού: Ενεργοποίηση υπολογιστών με διασύνδεση UCIe και σχεδιασμό βασισμένο σε τσιπετ

IP διεπαφής το 2022: Η ανάπτυξη 22% σε ετήσια βάση εξακολουθεί να βασίζεται στα δεδομένα

Μοιραστείτε αυτήν την ανάρτηση μέσω:

- SEO Powered Content & PR Distribution. Ενισχύστε σήμερα.

- PlatoData.Network Vertical Generative Ai. Ενδυναμώστε τον εαυτό σας. Πρόσβαση εδώ.

- PlatoAiStream. Web3 Intelligence. Ενισχύθηκε η γνώση. Πρόσβαση εδώ.

- PlatoESG. Ανθρακας, Cleantech, Ενέργεια, Περιβάλλον, Ηλιακός, Διαχείριση των αποβλήτων. Πρόσβαση εδώ.

- PlatoHealth. Ευφυΐα βιοτεχνολογίας και κλινικών δοκιμών. Πρόσβαση εδώ.

- πηγή: https://semiwiki.com/chiplet/339927-will-chiplet-adoption-mimic-ip-adoption/

- :έχει

- :είναι

- :δεν

- $UP

- 1

- 1995

- 200

- 2018

- 2022

- 2023

- 25

- a

- Σχετικα

- επιταχυντές

- Κατορθώνω

- προσαρμόσει

- προστιθέμενη

- προσθήκη

- υιοθετών

- Υιοθεσία

- προηγμένες

- AI

- Δεδομένα AI

- Όλα

- Επιτρέποντας

- επιτρέπει

- Επίσης

- AMD

- μεταξύ των

- ποσό

- ανάλυση

- αναλυτής

- και

- χώρια

- εμφανίζεται

- Εφαρμογή

- εφαρμογές

- αρχιτεκτονική

- ΕΙΝΑΙ

- ARM

- άρθρο

- τεχνητός

- τεχνητή νοημοσύνη

- Τεχνητή νοημοσύνη (AI)

- AS

- ASIC

- ζητώντας

- At

- συγγραφέας

- εύρος ζώνης

- βασίζονται

- BE

- γίνονται

- ξεκίνησε

- είναι

- παρακάτω

- οφέλη

- Καλύτερα

- Μεγάλος

- Ενισχυμένος

- και οι δύο

- Διακοπή

- χτίζω

- αλλά

- by

- κρύπτη

- CAN

- Χωρητικότητα

- κεφάλαιο

- κατηγορία

- αίτια

- σίγουρα

- προκλήσεις

- αλλαγή

- αλλαγή

- φτηνότερος

- έλεγχος

- τσιπ

- τσιπ

- Ελάτε

- σύγκριση

- συμπληρωματικός

- περίπλοκο

- Υπολογίστε

- χρήση υπολογιστή

- θεωρώντας

- Αντίστοιχος

- Κόστος

- Δικαστικά έξοδα

- θα μπορούσε να

- CPU

- δημιουργία

- δημιουργήθηκε

- δημιουργία

- έθιμο

- ημερομηνία

- δεκαετία

- αφιερωμένο

- ορίζεται

- πυκνότητα

- Υπηρεσίες

- σχεδιασμένα

- σχέδια

- Προσδιορίστε

- Ανάπτυξη

- εξελίξεις

- Συσκευές

- διαφορετικές

- Διάχυση

- Διαστάσεις

- διπλασιάστηκε

- κατεβάσετε

- αυτοκίνητο

- οδηγός

- οδήγηση

- δυο

- κατά την διάρκεια

- Νωρίτερα

- Νωρίς

- πρώιμες υιοθεσίες

- χαλάρωση

- οικοσύστημα

- αποδοτικότητα

- ενσωματωμένο

- εμφάνιση

- ενεργοποιητή

- ενεργοποίηση

- τέλος

- απολαύσετε

- κ.λπ.

- συνεχώς αυξανόμενη

- Κάθε

- εξέλιξη

- παράδειγμα

- έξοχος

- αποκλειστικά

- επέκταση

- Εξηγήστε

- ρητή

- εκχύλισμα

- γεγονός

- παράγοντας

- παράγοντες

- Πτώση

- FAST

- γρηγορότερα

- Εικόνα

- Για

- Πρόβλεψη

- προβλέπω

- Βρέθηκαν

- FPGA

- από

- λειτουργικός

- μελλοντικός

- Κέρδος

- παράγεται

- να πάρει

- μετάβαση

- GPU

- γραφικών

- Group

- Ανάπτυξη

- Έχω

- χρήσιμο

- εδώ

- High-End

- υψηλότερο

- ιστορία

- Σπίτι

- Πως

- Πώς να

- hpc

- HTTPS

- ia

- if

- Επίπτωση

- εφαρμοστεί

- επιβάλλονται

- in

- αυξημένη

- αύξηση

- απίστευτη

- βιομηχανία

- Καινοτομία

- καινοτόμους

- ενσωματώσει

- ενσωματωθεί

- Ενσωμάτωση

- ολοκλήρωση

- Intel

- Νοημοσύνη

- περιβάλλον λειτουργίας

- σε

- επένδυση

- IP

- IT

- jpg

- μόλις

- τήρηση

- Κλειδί

- μεγαλύτερος

- Επίθετο

- αργότερα

- ξεκίνησε

- Νόμος

- Οδηγεί

- μάθηση

- ελάχιστα

- Led

- μείον

- Μου αρέσει

- LIMIT

- πλέον

- ματιά

- χαμηλότερα

- μηχανή

- μάθηση μηχανής

- που

- Κυρίως

- μεγάλες

- Makers

- πολοί

- αγορά

- Μάρκετινγκ

- μαζική

- αναφέρω

- ελαχιστοποίηση

- ML

- Μονολιθικός

- περισσότερο

- πλέον

- ως επί το πλείστον

- μετακινήσετε

- μετακινηθεί

- πολλαπλούς

- Ανάγκη

- ανάγκες

- Νέα

- Νέες τεχνολογίες

- νεότερα

- ΝΙΗ

- Όχι.

- κόμβων

- τώρα

- αριθμός

- πολυάριθμες

- of

- προσφορά

- προσφορά

- on

- ONE

- αποκλειστικά

- Απόψεις

- Επιλογή

- or

- επιχειρήσεις

- Άλλα

- ιδιοκτήτης

- πακέτο

- συσκευασία

- Χαρτί

- μέρος

- επίδοση

- εκτέλεση

- φάση

- phd

- PHP

- συλλογή

- Εικόνες

- Πλάτων

- Πληροφορία δεδομένων Plato

- Πλάτωνα δεδομένα

- Δοκιμάστε να παίξετε

- έπαιξε

- συν

- Σημείο

- τοποθέτηση

- Θέση

- Ενεργοποίηση

- ακριβώς

- προβλέψει

- πρόβλεψη

- προτιμάται

- διαδικασια μας

- επεξεργασία

- μεταποίηση

- Επεξεργαστής

- παραγωγή

- Προϊόντα

- πρωτόκολλο

- Παρόχους υπηρεσιών

- ερώτηση

- Πιο γρήγορα

- γρήγορα

- γρήγορα

- Τιμή

- Τιμές

- φθάνοντας

- Διάβασε

- λόγους

- επανασχεδιασμό

- επανασχεδιασμένο

- σχετίζεται με

- υπενθύμιση

- Απαιτεί

- ΠΕΡΙΦΕΡΕΙΑ

- ανασκόπηση

- επανεξέταση

- Επανάσταση

- δεξιά

- Ρόλος

- ίδιο

- δείτε

- βλέποντας

- φαίνεται

- τμήμα

- τμήματα

- επιλέξτε

- ημιαγωγός

- διακομιστές

- εξυπηρετούν

- διάφοροι

- παρουσιάζεται

- σημαντικός

- σημαντικά

- Πυρίτιο

- παρόμοιες

- ενιαίας

- Μέγεθος

- μικρότερος

- smartphone

- λύση

- SOLVE

- μερικοί

- Σύντομα

- Χώρος

- προδιαγραφές

- ταχύτητα

- ΧΟΡΗΓΟΥΜΕΝΟΙ

- πρότυπο

- πρότυπα

- δήλωσε

- Ραβδί

- Ακόμη

- δομή

- επιτυχία

- επιτυχής

- σύστημα

- συστήματα

- στόχος

- τεχνικές

- Τεχνολογίες

- Τεχνολογία

- κείμενο

- από

- ευχαριστώ

- ότι

- Η

- τους

- Τους

- θεωρία

- Αυτοί

- αυτό

- εκείνοι

- Μέσω

- χρονοδιάγραμμα

- προς την

- εργαλεία

- κορυφή

- καταπληκτικός

- tsmc

- δύο

- τύπος

- Δυστυχώς

- Παγκόσμιος

- ενημέρωση

- us

- χρήση

- μεταχειρισμένος

- χρησιμοποιώντας

- διάφορα

- πωλητές

- μέσω

- ήταν

- Τρόπος..

- we

- ήταν

- Τι

- πότε

- ενώ

- άσπρο

- λευκό χαρτί

- WHY

- θα

- με

- Εργασία

- θα

- έτος

- χρόνια

- Βελτιστοποίηση

- εσείς

- zephyrnet