Η Banias Labs είναι μια εταιρεία ημιαγωγών που αναπτύσσει λύσεις υποδομής για επικοινωνίες επόμενης γενιάς. Η αγορά-στόχος της είναι η αγορά υπολογιστικής υποδομής υψηλής απόδοσης, συμπεριλαμβανομένων των κέντρων δεδομένων υπερκλίμακας, των δικτύων, της τεχνητής νοημοσύνης, της οπτικής μονάδας και των SoC μεταγωγέων Ethernet για αναδυόμενα σχέδια υπολογιστών υψηλής απόδοσης. Αυτά τα SoC απαιτούν σχέδια Ethernet υψηλής ταχύτητας και λύσεις χαμηλής καθυστέρησης για την παροχή αυξημένης απόδοσης του συστήματος και την επιτάχυνση του χρόνου διάθεσης στην αγορά. Η εταιρεία έχει αναπτύξει ένα οπτικό DSP SoC σε τεχνολογία διαδικασίας 5nm για να ανταποκριθεί στις απαιτήσεις αυτής της αγοράς.

![]()

Ένα οπτικό DSP SoC είναι ένας εξειδικευμένος τύπος συστήματος-σε-τσιπ (SoC) που έχει σχεδιαστεί για χρήση σε συστήματα οπτικών επικοινωνιών υψηλής ταχύτητας. Εκτός από το DSP, το οπτικό SoC DSP περιλαμβάνει συνήθως μπλοκ IP διεπαφής υψηλής ταχύτητας, όπως ελεγκτές μνήμης Ethernet PHY IP, PCIe IP και DDR. Αυτοί οι τύποι SoC επιτρέπουν τη μεταφορά δεδομένων υψηλής ταχύτητας σε χαμηλές καθυστερήσεις για επεξεργασία σήματος σε πραγματικό χρόνο. Είναι επίσης σχεδιασμένα για να ελαχιστοποιούν την κατανάλωση ενέργειας, καθιστώντας τα ιδανικά για εφαρμογές που απαιτούν αποτελεσματική λειτουργία με μειωμένα θερμικά προβλήματα. Μαζί με τα πλεονεκτήματα έρχονται και οι προκλήσεις. Οι εξειδικευμένες απαιτήσεις των συστημάτων οπτικής επικοινωνίας κάνουν τον σχεδιασμό ενός οπτικού DSP SoC πιο δύσκολο από τον σχεδιασμό ενός κανονικού SoC.

Προκλήσεις υλοποίησης

Οι προκλήσεις περιστρέφονται γύρω από την πολυπλοκότητα του σχεδιασμού, τις αυστηρές απαιτήσεις ισχύος και απόδοσης και την ανάγκη να πληρούνται διάφορα βιομηχανικά πρότυπα. Η ενοποίηση πολλαπλών μπλοκ IP, συμπεριλαμβανομένου του επεξεργαστή DSP, του Ethernet PHY IP και άλλων προσαρμοσμένων μπλοκ απαιτεί προσεκτικό σχεδιασμό και επικύρωση. Πρόσθετες διεπαφές υψηλής ταχύτητας όπως το PCIe και το DDR προσθέτουν περαιτέρω στην πολυπλοκότητα του σχεδιασμού. Οι διεπαφές υψηλής ταχύτητας και τα πολλαπλά μπλοκ IP στο σύστημα μπορούν να δημιουργήσουν παραμόρφωση σήματος, αλληλεπιδράσεις και ηλεκτρομαγνητικές παρεμβολές, οι οποίες μπορούν να επηρεάσουν την απόδοση και την αξιοπιστία του συστήματος. Η ανάλυση και η βελτιστοποίηση ακεραιότητας σήματος και ισχύος πρέπει να εκτελούνται νωρίς στον κύκλο σχεδιασμού για να διασφαλιστεί ότι το σύστημα μπορεί να ανταποκριθεί στις απαιτήσεις απόδοσης και αξιοπιστίας του. Τέλος, η ικανοποίηση των απαιτήσεων χρόνου για την αγορά μπορεί να είναι δύσκολη. Η αγορά υπολογιστικής υποδομής υψηλής απόδοσης εξελίσσεται ταχέως και οι ομάδες ανάπτυξης SoC πρέπει να παραδώσουν γρήγορα τα σχέδιά τους για να παραμείνουν μπροστά από τον ανταγωνισμό.

Getting to First Pass Silicon Success

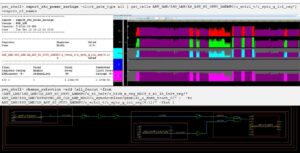

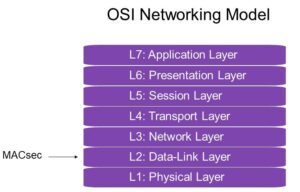

Η υπέρβαση των προαναφερθέντων προκλήσεων απαιτεί μια συνολική προσέγγιση. Ένα από τα κρίσιμα στοιχεία των λύσεων υψηλής απόδοσης και χαμηλής καθυστέρησης είναι το Ethernet PHY IP. Το Ethernet PHY IP είναι υπεύθυνο για τη διεπαφή φυσικού επιπέδου μεταξύ του SoC και του δικτύου Ethernet. Η IP πρέπει να υποστηρίζει διασυνδέσεις Ethernet υψηλής ταχύτητας, συμπεριλαμβανομένων των 10G, 25G, 40G, 50G, 100G, 200G, 400G και 800G, και να παρέχει χαμηλή καθυστέρηση και χαμηλή κατανάλωση ενέργειας. Επιπλέον, η IP πρέπει να υποστηρίζει διάφορα πρότυπα, συμπεριλαμβανομένων των IEEE 802.3 και Ethernet Alliance. Ένα άλλο σημαντικό στοιχείο είναι η σουίτα σχεδίασης EDA. Η σουίτα σχεδίασης EDA πρέπει να παρέχει μια ολοκληρωμένη λύση για το σχεδιασμό και την επαλήθευση του SoC, συμπεριλαμβανομένης της βελτιστοποίησης ισχύος, της ανάλυσης απόδοσης, της βελτιστοποίησης περιοχής και της ανάλυσης απόδοσης. Στο βαθμό που η σουίτα σχεδίασης EDA περιλαμβάνει προηγμένα χαρακτηριστικά, όπως τεχνητή νοημοσύνη (AI) και μηχανική μάθηση (ML), τόσο το καλύτερο για βελτιωμένη παραγωγικότητα και μειωμένο χρόνο διάθεσης στην αγορά.

Το Synopsys επιταχύνει την επιτυχία του πρώτου πέρασμα πυριτίου

Η Synopsys προσφέρει λύσεις που αντιμετωπίζουν τις μοναδικές προκλήσεις της ανάπτυξης SoC για την αγορά υπολογιστικής υποδομής υψηλής απόδοσης. Η εταιρεία παρέχει μια ολοκληρωμένη λύση IP που περιλαμβάνει μελέτη σκοπιμότητας δρομολόγησης, οδηγίες υποστρώματος συσκευασίας, μοντέλα ακεραιότητας σήματος και ισχύος και ενδελεχή ανάλυση διαφωνίας. Αυτό είναι επιτακτική ανάγκη για την αντιμετώπιση των προκλήσεων ακεραιότητας σήματος και ισχύος που αντιμετωπίζονται κατά την ανάπτυξη ενός οπτικού DSP SoC. Το 112G Ethernet PHY IP της Synopsys προσφέρει χαμηλή καθυστέρηση, ευέλικτα μήκη προσέγγισης και ωριμότητα σε τεχνολογία διεργασιών 5nm, καθιστώντας το ιδανική λύση για κέντρα δεδομένων υπερκλίμακας, δικτύωση, AI, οπτική μονάδα και SoC μεταγωγέα Ethernet. Επιπλέον, η Synopsys προσφέρει μια σουίτα σχεδίασης EDA που προσφέρει αποτελέσματα υψηλής ποιότητας με βελτιστοποιημένη ισχύ, απόδοση, επιφάνεια και απόδοση. Το EDA Design Suite της Synopsys που βασίζεται στην τεχνητή νοημοσύνη παρέχει λύσεις για την ενίσχυση της απόδοσης του συστήματος και την επιτάχυνση της κυκλοφορίας, καθιστώντας το βασικό συστατικό μιας επιτυχημένης λύσης για την αγορά υπολογιστικής υποδομής υψηλής απόδοσης.

Χαρακτηριστικά

Η Synopsys παρέχει λύσεις υψηλής απόδοσης και χαμηλής καθυστέρησης που επιταχύνουν την ανάπτυξη προηγμένων SoC μεταγωγέων Ethernet και δικτύωσης. Για να μάθετε περισσότερα σχετικά με τις ολοκληρωμένες λύσεις IP της Synopsys, την ολοκληρωμένη σουίτα σχεδίασης EDA και τη σουίτα EDA με βελτιωμένη τεχνητή νοημοσύνη, επισκεφθείτε τις ακόλουθες σελίδες.

Οι ολοκληρωμένες λύσεις IP της Synopsys

Η ολοκληρωμένη σουίτα EDA της Synopsys

Σουίτα σχεδίασης EDA της Synopsys που βασίζεται σε AI

Διαβάστε επίσης:

Συστήματα Multi-Die: Η μεγαλύτερη διαταραχή στους υπολογιστές εδώ και χρόνια

Τροφοδοτώντας την αυξανόμενη πείνα για εύρος ζώνης με Ethernet υψηλής ταχύτητας

Μοιραστείτε αυτήν την ανάρτηση μέσω:

- SEO Powered Content & PR Distribution. Ενισχύστε σήμερα.

- Platoblockchain. Web3 Metaverse Intelligence. Ενισχύθηκε η γνώση. Πρόσβαση εδώ.

- Minting the Future με την Adryenn Ashley. Πρόσβαση εδώ.

- πηγή: https://semiwiki.com/ip/327703-synopsys-accelerates-first-pass-silicon-success-for-banias-labs-networking-soc/

- :έχει

- :είναι

- a

- Σχετικα

- πάνω από

- επιταχύνουν

- επιταχύνει

- Επιπλέον

- Πρόσθετος

- Επιπλέον

- διεύθυνση

- προηγμένες

- πλεονεκτήματα

- εμπρός

- AI

- Συμμαχία

- Επίσης

- an

- ανάλυση

- και

- Άλλος

- εφαρμογές

- πλησιάζω

- ΕΙΝΑΙ

- ΠΕΡΙΟΧΗ

- γύρω

- τεχνητός

- τεχνητή νοημοσύνη

- Τεχνητή νοημοσύνη (AI)

- AS

- At

- εύρος ζώνης

- BE

- Καλύτερα

- μεταξύ

- Μεγαλύτερη

- Μπλοκ

- ώθηση

- CAN

- προσεκτικός

- Κέντρο

- προκλήσεις

- πρόκληση

- Ελάτε

- Επικοινωνία

- Διαβιβάσεις

- εταίρα

- ανταγωνισμός

- περίπλοκο

- συστατικό

- εξαρτήματα

- περιεκτικός

- χρήση υπολογιστή

- κατανάλωση

- δημιουργία

- κρίσιμης

- έθιμο

- κύκλος

- ημερομηνία

- Κέντρο δεδομένων

- παραδώσει

- παραδίδει

- Υπηρεσίες

- σχεδιασμένα

- σχέδιο

- σχέδια

- αναπτύχθηκε

- ανάπτυξη

- Ανάπτυξη

- αναπτύσσεται

- Αναστάτωση

- Νωρίς

- αποτελεσματικός

- σμυριδόπετρα

- ενεργοποιήσετε

- ενισχυμένη

- εξασφαλίζω

- ουσιώδης

- εξελίσσεται

- αντιμετωπίζουν

- FAST

- Χαρακτηριστικά

- Τελικά

- Όνομα

- εύκαμπτος

- Εξής

- Για

- από

- περαιτέρω

- Μεγαλώνοντας

- κατευθυντήριων γραμμών

- υψηλή απόδοση

- υψηλής ποιότητας

- HTML

- HTTPS

- πείνα

- ιδανικό

- IEEE

- εικόνα

- Επίπτωση

- επιτακτικός

- σημαντικό

- in

- περιλαμβάνει

- Συμπεριλαμβανομένου

- αυξημένη

- βιομηχανία

- βιομηχανικά πρότυπα

- Υποδομή

- ολοκλήρωση

- ακεραιότητα

- Νοημοσύνη

- περιβάλλον λειτουργίας

- διεπαφές

- IP

- θέματα

- IT

- ΤΟΥ

- Labs

- Αφάνεια

- στρώμα

- ΜΑΘΑΊΝΩ

- μάθηση

- Χαμηλός

- μηχανή

- μάθηση μηχανής

- κάνω

- Κατασκευή

- αγορά

- ωριμότητα

- max-width

- Γνωρίστε

- συνάντηση

- Μνήμη

- που αναφέρθηκαν

- ML

- μοντέλα

- ενότητα

- περισσότερο

- πολλαπλούς

- Ανάγκη

- δίκτυο

- δικτύωσης

- επόμενη γενιά

- of

- προσφορές

- on

- ONE

- λειτουργία

- βελτιστοποίηση

- βελτιστοποιημένη

- ΑΛΛΑ

- δική

- συσκευασία

- passieren

- επίδοση

- φυσικός

- Πλάτων

- Πληροφορία δεδομένων Plato

- Πλάτωνα δεδομένα

- Θέση

- δύναμη

- διαδικασια μας

- μεταποίηση

- Επεξεργαστής

- παραγωγικότητα

- παρέχουν

- παρέχει

- γρήγορα

- ταχέως

- φθάσουν

- Διάβασε

- σε πραγματικό χρόνο

- Μειωμένος

- τακτικός

- αξιοπιστία

- απαιτούν

- απαιτήσεις

- Απαιτεί

- υπεύθυνος

- Αποτελέσματα

- Κίνδυνος

- ημιαγωγός

- Σήμα

- Πυρίτιο

- λύση

- Λύσεις

- ειδικευμένος

- πρότυπα

- παραμονή

- Μελέτη

- επιτυχία

- επιτυχής

- τέτοιος

- σουίτα

- υποστήριξη

- διακόπτης

- σύστημα

- συστήματα

- στόχος

- ομάδες

- Τεχνολογία

- από

- ότι

- Η

- τους

- Τους

- θερμικός

- Αυτοί

- αυτοί

- αυτό

- προς την

- πολύ

- μεταβιβάσεις

- τύποι

- συνήθως

- μοναδικός

- χρήση

- επικύρωση

- διάφορα

- επαληθεύοντας

- μέσω

- Επίσκεψη

- Ποιό

- με

- Βελτιστοποίηση

- Σας

- zephyrnet