Da immer mehr Unternehmen an Geräten interessiert sind, die auf RISC-V ISA basieren, und immer mehr Kerne, Beschleuniger und Infrastrukturkomponenten entweder kommerziell oder in Open-Source-Form verfügbar gemacht werden, stehen Endbenutzer vor einer immer schwierigeren Herausforderung um sicherzustellen, dass sie die besten Entscheidungen treffen.

Jeder Benutzer wird wahrscheinlich eine Reihe von Bedürfnissen und Bedenken haben, die fast der Flexibilität der RISC-V-Angebote entsprechen und weit über traditionelle PPA-Metriken hinausgehen und Sicherheitsbedenken oder Qualitätsüberlegungen umfassen. Dazu könnte die Anpassungsfähigkeit der Verifizierungssicherheit gehören, die eine architektonische Erweiterung und die damit einhergehende notwendige Verifizierung ermöglicht.

Traditionell werden drei Ebenen des Prototypings eingesetzt: virtuelle Prototypen, Emulation und FPGA-Prototypen, einschließlich Hybriden zwischen ihnen. Jede Plattform wird dann für verschiedene Zwecke verwendet, darunter Softwareverifizierung, Architekturvalidierung, Funktionsverifizierung der Hardware, Leistungsanalyse und mehr.

Während sich die Design- und Software-Ökosysteme für RISC-V etablieren, hinken die Konfigurations- und Verifizierungsökosysteme hinterher und erfordern den Aufbau neuer Technologien. Es ist die Flexibilität von RISC-V, die große Herausforderungen für die Verifizierung mit sich bringt, die über das hinausgehen, was für die Verifizierung fester Prozessoren erforderlich ist. Es macht auch die gemeinsame Entwicklung von Hardware und Software nicht nur möglich, sondern notwendig.

Co-Entwicklung

In der Vergangenheit wurde zunächst Hardware ausgewählt und anschließend Software entwickelt, die darauf läuft. Bei RISC-V wird die Hardware häufig durch Software gesteuert. „Als Erstes müssen Sie auswählen, welche Standard-RISC-V-Optionen Sie wünschen“, sagt Simon Davidmann, Gründer und CEO von Imperas-Software. „Der RISC-V-Funktionsumfang umfasst derzeit 200 oder 300 Optionen. Woher wissen Sie, ob Ihr Algorithmus von einer Gleitkommaeinheit oder SIMD, Hardware-Multiplikatoren oder sogar einer Vektor-Engine profitieren würde? Sie müssen die Hardwarefunktionen ermitteln, die Sie für die Art der Anwendung oder die Aufgabe, die dieser Prozessor ausführen soll, benötigen und sich leisten können. Das allein wird zu einer kleinen Herausforderung.“

Für solche Kompromisse sind Prototypen erforderlich. „Wenn es das Ziel des Designers ist, Leistung und Zweckmäßigkeit zu bewerten, ist virtuelles Prototyping die einzig praktikable Wahl“, sagt Steve Roddy, CMO bei Quadrik. „Der Bau von Hardware-Prototypen ist mehr als 10 bis 50 Mal zeitaufwändiger als die Erstellung eines SystemC-Modells eines Subsystems oder eines gesamten SoC. Der virtuelle SystemC-Prototyp läuft im Allgemeinen schnell genug, um Leistungsfragen zu beantworten, z. B. wie viele Frames pro Sekunde Durchsatz ich mit diesem Prozessorkern erreichen kann oder wie hoch der Spitzen- und durchschnittliche Bandbreitenbedarf der Funktion X ist, und zwar innerhalb eines akzeptablen Genauigkeitsbereichs.“

Es kann schwierig sein, die richtige Genauigkeit zu erreichen. „Es geht um Genauigkeit und Ihre Fähigkeit, ein Modell sehr schnell zu drehen“, sagt Frank Schirrmeister, Vizepräsident für Lösungen und Geschäftsentwicklung bei Arteris-IP. „Die richtige Genauigkeit wird durch die Anforderungen Ihrer Frage bestimmt, und diese zu generieren ist nicht trivial. Wenn Sie ein ASIP-Anbieter sind, können Sie diese aus jeder beliebigen Vorlage generieren. Abhängig von der Frage benötigen Sie möglicherweise Pipeline-Genauigkeit, Sie benötigen möglicherweise Speichergenauigkeit, es muss nicht völlig genau sein, aber wenn Sie eine CAD-Abteilung involviert haben, haben diese zu viel Angst davor, die falsche Frage zu beantworten.“

Aber Genauigkeit ist ein Kompromiss gegen Geschwindigkeit. „Während einige virtuelle Prototypen zyklusgenau sind, laufen diese oft zu langsam, um den nötigen Software-Durchsatz zu erreichen“, sagt Davidmann von Imperas. „Die leistungsstärksten virtuellen Prototypen sind keine Performance-Engines, da sie keine Prozessor-Pipelines modellieren. Sie betrachten es aus Software-Sicht, wo Sie es kompilieren und auf Hardware ausführen können, und Sie können die ungefähre Leistung erkennen, indem Sie sich die Befehlsanzahl oder ungefähre Timing-Schätzungen ansehen. Das sollte ausreichen, um eine solche architektonische Entscheidung zu treffen.“

Oft sind mehrere Prototypen erforderlich. „Wir erstellen im Allgemeinen aus zwei Gründen Prototypen“, sagt Venki Narayanan, Senior Director für Software und Systemtechnik im FPGA-Geschäftsbereich von Microchip Technology. „Eine davon ist die Architekturvalidierung, um sicherzustellen, dass wir alle Leistungskennzahlen und -anforderungen erfüllen, sowie die Funktionsvalidierung. Der andere Grund ist die Entwicklung eingebetteter Software und Firmware. Wir verwenden verschiedene Ebenen von Prototyping-Techniken, wobei die häufigste darin besteht, unsere eigenen FPGAs zu verwenden, um eine Emulationsplattform sowohl für die Architektur- als auch für die Funktionsvalidierung zu entwickeln. Wir verwenden auch Architekturmodelle wie QEMU, um virtuelle Plattformen sowohl für die Leistungsvalidierung als auch für die Entwicklung eingebetteter Software zu erstellen.“

Die Zahl der Möglichkeiten wächst. „Es gibt heute viele Möglichkeiten, wie Unternehmen Prototypen mit RISC-V entwickeln“, sagt Mark Himelstein, CTO von RISC-V International. „Diese reichen von Einplatinencomputern auf Herstellerebene bis hin zu LINUX-fähigen Unternehmensplatinen. Emulationsumgebungen (wie QEMU) ermöglichen es Entwicklern, mit Software voranzukommen, bevor ihre Hardware fertig ist, und es gibt überall handelsübliche Teile, von eingebetteten SoCs (von Unternehmen wie Espressif und Telink) bis hin zu FPGAs (von Unternehmen wie Microsemi). das kommende Horse Creek-Board von Intel und SiFive.“

Es kommt wieder auf den Kompromiss zwischen Leistung und Genauigkeit an. „Physische Prototypen erfordern weitaus mehr Designaufwand, weil man echtes RTL verbindet und synthetisiert, aber sie liefern eine weitaus höhere Genauigkeit und einen weitaus höheren Durchsatz“, sagt Roddy von Quadric. „Ein physischer Prototyp in einem FPGA-System, sei es selbst entwickelt oder von großen EDA-Unternehmen, erfordert Aufwand. Aber es kann eine Größenordnung schneller laufen als ein SystemC-Modell und mehrere Größenordnungen schneller als eine vollständige Simulation auf Gate-Ebene. Designteams wechseln während des IP-Auswahlprozesses typischerweise von C-basierten Modellen zu physischen Modellen, sowohl zur Überprüfung des tatsächlichen Designs nach der IP-Auswahl als auch als System-Software-Entwicklungsplattform.“

Sobald Sie wissen, welchen Funktionsumfang Sie in der Hardware wünschen, können Sie prüfen, ob bereits jemand eine Lösung erstellt hat, die die meisten Ihrer Anforderungen erfüllt. „Die Chancen stehen gut, dass es bei all den Anbietern eine kommerzielle Lösung gibt, die genau das bietet, was Sie suchen“, sagt Davidmann. „Aber mit RISC-V müssen Sie diese Lösung nicht so akzeptieren, wie sie ist. Ein wesentlicher Teil des Werts von RISC-V ist die Freiheit, es zu ändern, zu modifizieren und verschiedene Dinge hinzuzufügen, die Sie möchten.“

Auswahl einer Implementierung

Es gibt viele Möglichkeiten, eine Reihe von Funktionen zu implementieren, z. B. die Anzahl der Pipeline-Stufen oder spekulative Ausführungsfunktionen. Jeder hat einen anderen Kompromiss zwischen Leistung, Leistung und Fläche. „Die ISA-Variante, sei es RISC-V, Arm, Cadence’s „Ein Systemarchitekt muss unabhängig von der Prozessormarke Fragen zu SoC-Designzielen beantworten. Auf technischer Ebene befindet sich der RISC-V-Zug in Bezug auf die Unterstützung von Modellierungs- und Leistungsanalysetools wirklich in einer stabilen Marktposition. Es gibt zahlreiche konkurrierende Kernanbieter mit jeweils unterschiedlichen Implementierungen und Prozessorfunktionen. Als Hauptsystem-CPU hat sie nicht die Langlebigkeit eines Arms, und daher verfügen weniger Ökosystemteilnehmer in der EDA-Welt über eine allgemein validierte, gebrauchsfertige Modellierungsunterstützung für handelsübliche RISC-V-Kerne dieser Sorte der RISC-V-Anbieter. Als konfigurierbarer, modifizierbarer Kern hinkt die RISC-V-Welt dem Grad der Befehlssatzautomatisierung hinterher, den Tensilica in 25 Jahren aufgebaut hat. Daher verfügt RISC-V als vorgefertigter Baustein über weniger Modellierungsunterstützung und weniger Automatisierung als Plattform für Befehlssatzexperimente.“

Aber das ist nur ein Aspekt einer Umsetzung, der bewertet werden muss. Welche Qualität hat es? Wenn Sie es ändern möchten, wie validieren Sie es erneut?

Die Leistung lässt sich am einfachsten beurteilen. „Das ist nichts anderes, als wenn man sich an einen herkömmlichen Prozessoranbieter wendet“, sagt Davidmann. „Sie werden Ihnen sagen, dass dieser Kern so viele Dhrystones pro Watt liefert, sie werden Ihnen die typischen analytischen Prozessordaten liefern, die besagen, dass diese Mikroarchitektur so schnell läuft.“ Sie verfügen über all diese Daten, und jeder, der einen Prozessorkern lizenziert, ist mit diesen Daten vertraut und wird mit ihnen sprechen und diese Informationen einholen. Sie werden wahrscheinlich viele auswählbare Optionen in ihrem Datenblatt haben und sagen: „Wenn Sie diese Option aktivieren, erhalten Sie dies oder das.“ Sie können es im Datenblatt und auf den Websites der Anbieter nachsehen. ”

Auf dieser Ebene benötigen Sie wahrscheinlich Zyklusgenauigkeit. „Ich sehe, dass die meisten Leute es in einen Emulator pumpen und genügend Daten durchlaufen lassen, um eine vernünftige Entscheidung zu treffen“, sagt Schirrmeister. „Ich sehe keinen baldigen Übergang zu virtuellen Prototypen. Einige Unternehmen sprechen von FPGA-Prototypen, bei denen Sie über eine eigene Single-Board-Lösung verfügen. Abhängig von der Frage, die Sie beantworten müssen, entscheiden Sie sich möglicherweise dafür, es zu konfigurieren, zu generieren und es dann in ein FPGA zu pumpen, um mehr Daten darüber laufen zu lassen, mit den entsprechenden Softwareroutinen darüber. Die Branche verfügt über ausreichend schnelle Einstiegsmöglichkeiten in Emulatoren und Prototyping, um dies zu ermöglichen. Das Grundproblem besteht darin, dass Sie diese Entscheidung auf der Grundlage möglichst genauer Daten treffen möchten, aber zu dem Zeitpunkt, an dem Sie diese Entscheidung treffen möchten, möglicherweise nicht über diese genauen Daten verfügen.“

Viele dieser Prototypen müssen mehr als nur den Prozessor enthalten. „Virtuelle Plattformen bieten die Möglichkeit zur Integration mit anderen externen physischen Hardwarefunktionen wie Speicher und Sensoren, die in einer realen Umgebung arbeiten“, sagt Narayanan von Microchip. „Hybridsysteme können virtuelle Plattformen mit physischen Prototypen für andere externe Funktionen zusammenführen. FPGA-Emulation und Prototyping helfen bei der Suche nach zeitbezogenen Fehlern, wie z. B. Race Conditions, da dies zyklusgenauer ist und externe Funktionen schneller ausgeführt werden.“

Verification

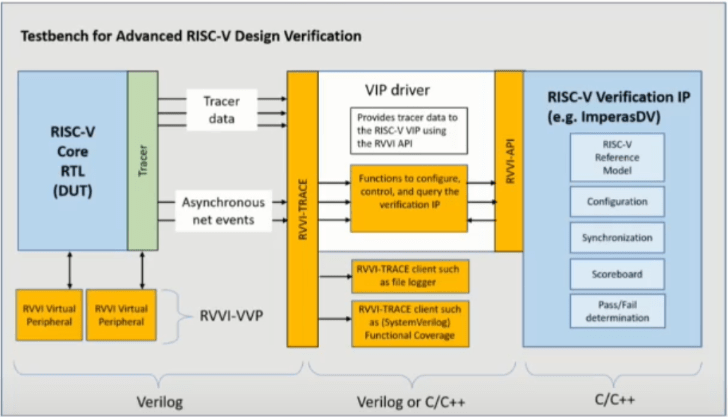

Da das Prozessordesign seit langem intern erfolgt, gibt es kein öffentliches Verifizierungsökosystem für den Bau eines Prozessors und die Funktionen von RISC-V erfordern eine viel flexiblere Verifizierungslösung, als es sie jemals in der Vergangenheit gab. Die Entstehung davon fängt gerade erst an.

„Es gibt Branchenkennzahlen wie Dhrystones oder CoreMark, damit die Leute die Leistung vergleichen können“, sagt Davidmann. „Aber wie kann man die Verifizierungsqualität vergleichen? Es müssen gleiche Wettbewerbsbedingungen herrschen, damit jeder Anbieter sagen kann: „So machen wir es.“ Wir brauchen einige Qualitätsmetriken im Zusammenhang mit der Verifizierung.“

Hier kann die Open-Source-Bewegung helfen. „Wenn man sich das RISC-V-Ökosystem anschaut, hat man eine große Anzahl sehr erfahrener Prozessorentwickler“, sagt Schirrmeister. „Es gibt zwei Extreme. Erstens bekomme ich einen Kern von einem Anbieter, und wenn er nicht funktioniert, liegt ein Problem damit vor. Andererseits habe ich völlige Freiheit und mache alles selbst. Irgendwo zwischen diesen beiden Extremen entwickelt sich ein Gleichgewicht. Sie erhalten etwas, bei dem Ihr Anbieter ein gewisses Maß an Verifizierung vorsieht, und für die Erweiterungen sind Sie dann selbst verantwortlich.“

Und hier kommen Kennzahlen ins Spiel. „ISA-Kompatibilität ist nur die erste Stufe auf einer Leiter voller Komplexität, die nur wenige Unternehmen erklommen haben“, sagt Dave Kelf, CEO von Breker Verification Systems. „Prototyping ist vielleicht die einzige Möglichkeit, einen zuverlässigen Prozessorbetrieb vollständig sicherzustellen, aber die Nutzung realer Workloads zum Antrieb dieser Prototypen kratzt an der Oberfläche der tatsächlichen Prozessorabdeckung. Dies steht im Widerspruch zu den Wettbewerbsbemühungen einer offenen ISA, die zu einer beschleunigten Entwicklung und zu Problemen bei der Markteinführung führt.“

Aber was sind diese Kennzahlen? „In der OpenHW-Qualitätsgruppe versuchen wir herauszufinden, wie diese Metriken aussehen sollten“, sagt Davidmann. „Dazu gehören Dinge wie die funktionale Abdeckung, denn es handelt sich nicht nur um einfache Anweisungen. Für einen hochwertigen Prozessor braucht man viel mehr. Sie benötigen eine Methodik zur Überprüfung, bei der Sie sicher sein können, dass Ihre Vergleiche mit einer Referenz alles abdecken. Die funktionale Abdeckung zeigt nur, dass Sie den Test haben, aber das muss mit einer Methodik gekoppelt werden, die mit einer Form bekannter Referenz verglichen werden kann. Wir werden die Fault-Injection-Technologie hinzufügen, damit Sie herausfinden können, ob Ihr Prüfstand tatsächlich Probleme erkennt.“

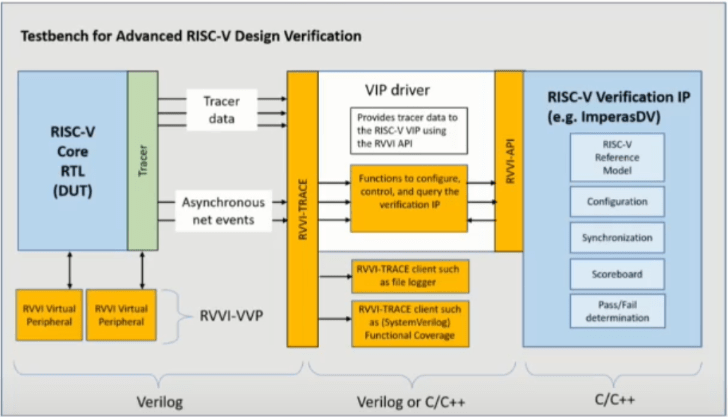

Abb. 1: Definieren der Architektur einer RISC-V-Verifizierungslösung. Quelle: Imperas

Es wird eine Reihe von Werkzeugen benötigt. „Mit zunehmender Reife des RISC-V-Ökosystems beginnen kommerzielle Implementierungen, definierte Marktsegmente zu unterstützen“, sagt Ashish Darbari, Gründer und CEO von Axiomise. „Wir sehen Unterstützung für Märkte wie die Automobilindustrie, die die Einhaltung der funktionalen Sicherheit erfordern. Wir sehen Unterstützung für IoT, das Sicherheit erfordert. RISC-V-Anbieter investieren in fortschrittliche Verifizierungstechniken, einschließlich virtueller Prototypen für Architekturmodellierung und Leistung. Es stehen jetzt Tools für die frühzeitige Einführung formaler Methoden zur Verfügung, um Fehler frühzeitig im Entwurfsprozess zu beseitigen und das Einfügen von Fehlern zu vermeiden, da Designer Schwierigkeiten haben, Eckfehler durch Simulation auf der Prozessor-Speicher-Schnittstelle zu erkennen.“

Eines der erforderlichen Tools ist die Fähigkeit, Testfälle basierend auf einer Funktionsliste oder einer Reihe von Funktionen zu generieren. „Die automatisierte Generierung von Testinhalten, um Prototypen voranzutreiben, die die Komplexität der Verifizierung zeitnah berücksichtigen, ist von entscheidender Bedeutung“, sagt Kelf von Breker. „Diese Erzeugungsmechanismen fangen jetzt an, auf den Markt zu kommen.“

Zusammenfassung

Ein Ökosystem ist nur so gut wie seine schwächste Komponente, und für RISC-V ist das die EDA-Toolchain. Dafür gibt es zwei Gründe. Erstens gab es bis vor Kurzem keinen kommerziellen Markt für Tools zur Prozessorverifizierung. Obwohl sie in der Vergangenheit existierten, waren sie alle entweder verschwunden oder in den alten Prozessorunternehmen aufgelöst worden. Zweitens schafft die Flexibilität der RISC-V ISA einen neuen Optimierungsansatz auf Systemebene, der einen neuen Satz an Tools erfordert. Es braucht Zeit, bis diese Chance verstanden wird und kommerzielle Tools auf den Markt kommen, die sie angemessen nutzen.

Verbunden

Ein minimales RISC-V

Gibt es Platz für eine noch kleinere Version eines RISC-V-Prozessors, der 8-Bit-Mikrocontroller ersetzen könnte?

RISC-V dringt in den Mainstream vor

Open-Source-Prozessorkerne tauchen zunehmend in heterogenen SoCs und Paketen auf.

Effiziente Ablaufverfolgung in RISC-V

So arbeiten Sie mit dem neuen RISC-V-Debug-Standard.

Wie sicher sind RISC-V-Chips?

Open Source allein garantiert keine Sicherheit. Es kommt immer noch auf die Grundlagen des Designs an.

- SEO-gestützte Content- und PR-Distribution. Holen Sie sich noch heute Verstärkung.

- Platoblockkette. Web3-Metaverse-Intelligenz. Wissen verstärkt. Hier zugreifen.

- Quelle: https://semiengineering.com/selecting-the-right-risc-v-core/

- 1

- 10

- a

- Fähigkeit

- Fähig

- Über uns

- oben

- beschleunigt

- Beschleuniger

- Akzeptieren

- akzeptabel

- Konto

- Genauigkeit

- genau

- berührt das Schneidwerkzeug

- Adresse

- Adoption

- advanced

- Nach der

- gegen

- Algorithmus

- Alle

- bereits

- Betrag

- Analyse

- Analytische

- und

- und Infrastruktur

- beantworten

- erscheinen

- Anwendung

- Ansatz

- angemessen

- Arc

- architektonisch

- Architektur

- Bereich

- ARM

- Aussehen

- bewertet

- Automatisiert

- Automation

- Automobilindustrie

- verfügbar

- durchschnittlich

- Zurück

- Bandbreite

- basierend

- basic

- weil

- wird

- Werden

- Bevor

- Anfang

- Sein

- Nutzen

- BESTE

- zwischen

- Beyond

- Big

- Bit

- Blockieren

- Tafel

- Marke

- bringen

- allgemein

- Fehler

- Bugs

- bauen

- Building

- erbaut

- Geschäft

- Geschäftsentwicklung

- CAD

- Fähigkeiten

- fähig

- Ringen

- CEO

- sicher

- challenges

- Herausforderungen

- Chancen

- Übernehmen

- Pommes frites

- Wahl

- Entscheidungen

- Auswählen

- Kletterte

- Business Development

- Sicherheit

- wie die

- kommerziell

- kommerziell

- gemeinsam

- Unternehmen

- vergleichen

- Kompatibilität

- konkurrierenden

- wettbewerbsfähig

- abschließen

- Komplexität

- Compliance

- Komponente

- Komponenten

- Computer

- Bedenken

- Bedingungen

- Vertrauen

- Konfiguration

- Sich zusammenschliessen

- Überlegungen

- Inhalt

- Kernbereich

- könnte

- gekoppelt

- Berichterstattung

- Abdeckung

- CPU

- erstellt

- schafft

- Erstellen

- Schaffung

- Creek

- CTO

- Zur Zeit

- technische Daten

- Dave

- Entscheidung

- Definition

- Übergeben

- Anforderungen

- Abteilung

- Abhängig

- Einsatz

- Design

- Designprozess

- Designer

- entwickeln

- entwickelt

- Entwickler

- Entwicklung

- Entwicklung

- Geräte

- anders

- schwer

- Direktor

- Tut nicht

- Nicht

- nach unten

- Antrieb

- angetrieben

- Fahren

- im

- jeder

- Früh

- einfachste

- Ökosystem

- Ecosystems

- Anstrengung

- Bemühungen

- entweder

- eingebettet

- ermöglicht

- Motor

- Entwicklung

- Motor (en)

- genug

- gewährleisten

- Gewährleistung

- Unternehmen

- Ganz

- Eintrag

- Arbeitsumfeld

- Umgebungen

- Equals

- Gleichgewicht

- etablierten

- Schätzungen

- bewerten

- Sogar

- ÜBERHAUPT

- alles

- Ausführung

- erfahrensten

- Verlängerung

- Erweiterung

- Erweiterungen

- extern

- Extreme

- Gesicht

- vertraut

- Fashion

- FAST

- beschleunigt

- Merkmal

- Eigenschaften

- wenige

- Feld

- Feige

- Finden Sie

- Suche nach

- Vorname

- passen

- fixiert

- Flexibilität

- flexibel

- unten stehende Formular

- formal

- Gründer

- Unternehmensgründer und CEO

- FPGA

- Freiheit

- für

- voller

- voll

- Funktion

- funktional

- Funktionen

- Grundlagen

- allgemein

- erzeugen

- Erzeugung

- Generation

- bekommen

- bekommen

- ABSICHT

- gibt

- Go

- Ziele

- gehen

- gut

- mehr

- Gruppe an

- persönlichem Wachstum

- Garantie

- passieren

- Hardware

- Hilfe

- hilft

- hochwertige

- einheimisch

- Pferd

- Ultraschall

- HTTPS

- riesig

- Impact der HXNUMXO Observatorien

- implementieren

- Implementierung

- in

- das

- Dazu gehören

- Einschließlich

- zunehmend

- zunehmend

- Energiegewinnung

- Information

- Infrastruktur

- Anleitung

- integrieren

- Intel

- interessiert

- Schnittstelle

- International

- Investitionen

- beteiligt

- iot

- IP

- Probleme

- IT

- selbst

- Job

- Wesentliche

- Art

- Wissen

- bekannt

- Leiter

- grosse

- Legacy

- Niveau

- Cholesterinspiegel

- Nutzung

- Lizenzierung

- wahrscheinlich

- linux

- Liste

- Lang

- lange Zeit

- Langlebigkeit

- aussehen

- suchen

- gemacht

- Main

- um

- Hersteller

- MACHT

- viele

- Kennzeichen

- Markt

- Märkte

- reift

- max-width

- Triff

- Memory

- Methodik

- Methoden

- Metrik

- minimal

- Modell

- Modellieren

- für

- ändern

- mehr

- vor allem warme

- Bewegung

- ziehen um

- notwendig,

- Need

- Bedürfnisse

- Neu

- Anzahl

- und viele

- Ziel

- Odds

- Angebote

- EINEM

- XNUMXh geöffnet

- Open-Source-

- die

- Betrieb

- Gelegenheit

- Optimierung

- Option

- Optionen

- Auftrag

- Bestellungen

- Andere

- besitzen

- Pakete

- Teil

- Teile

- passt

- Haupt

- Personen

- Leistung

- physikalisch

- Pipeline

- Drehpunkt

- Plattform

- Plattformen

- Plato

- Datenintelligenz von Plato

- PlatoData

- spielend

- Points

- Perspektive

- Position

- Möglichkeiten

- möglich

- Werkzeuge

- Präsident

- wahrscheinlich

- Aufgabenstellung:

- Probleme

- Prozessdefinierung

- Prozessor

- Prozessoren

- Fortschritt

- richtig

- Prototyp

- Prototypen

- Prototyping

- die

- vorausgesetzt

- Versorger

- Öffentlichkeit

- Pumpe

- Pumpen

- Zweck

- Zwecke

- Qualität

- Frage

- Fragen

- Rennen

- Angebot

- fertig

- echt

- realen Welt

- Grund

- vernünftig

- Gründe

- kürzlich

- Ungeachtet

- zuverlässig

- ersetzen

- erfordern

- falls angefordert

- Anforderung

- Voraussetzungen:

- erfordert

- Verantwortung

- Zimmer

- Führen Sie

- Laufen

- Sicherheit

- Sicherheit und Gefahrenabwehr

- Zweite

- Verbindung

- Sicherheitdienst

- Segmente

- ausgewählt

- Auswahl

- Auswahl

- Senior

- Sensoren

- kompensieren

- mehrere

- sollte

- erklären

- Konzerte

- signifikant

- Bernd

- Einfacher

- Simulation

- Single

- Langsam

- kleinere

- So

- Software

- Software-Entwicklung

- Lösung

- Lösungen

- einige

- Jemand,

- etwas

- irgendwo

- Bald

- Quelle

- Geschwindigkeit

- verbrachte

- Wirbelsäule ... zu unterstützen.

- stabil

- Stufen

- Standard

- Beginnen Sie

- Steve

- Immer noch

- Kämpfen

- so

- Suite

- Support

- Oberfläche

- System

- Systeme und Techniken

- Nehmen

- nimmt

- Reden

- sprechen

- Teams

- Technische

- Techniken

- Technologie

- Vorlage

- Test

- Das

- ihr

- deswegen

- Ding

- nach drei

- Durch

- Durchsatz

- Zeit

- Zeitaufwendig

- mal

- zeitliche Koordinierung

- zu

- heute

- gemeinsam

- auch

- Werkzeuge

- Top

- Gesamt

- Spur

- traditionell

- WENDE

- typisch

- typisch

- verstanden

- Einheit

- anstehende

- -

- Mitglied

- Nutzer

- validiert

- Bestätigung

- Wert

- Vielfalt

- Verkäufer

- Anbieter

- Verification

- Version

- lebensfähig

- Vizepräsident:in

- Anzeigen

- Assistent

- virtuelle Plattformen

- wollen

- Wege

- Webseiten

- Was

- Was ist

- ob

- welche

- während

- werden wir

- .

- Arbeiten

- trainieren

- weltweit wie ausgehandelt und gekauft ausgeführt wird.

- würde

- Falsch

- X

- Jahr

- Ihr

- Zephyrnet