S2C ist seit fast zwei Jahrzehnten weltweit führend im FPGA-Prototyping und seine FPGA-Prototyping-Plattformen haben die Verfügbarkeit der neuesten FPGAs genau verfolgt – einschließlich der neuesten FPGAs von Xilinx und Intel. Und sie halten definitiv ihr Versprechen, ihre Prototyping-Lösungen für Hyperscale-Design-Prototyping weiterzuentwickeln – Hochskalieren Kapazitäten und Fähigkeiten der Prototyping-Plattform zur Unterstützung von Gate-Designs mit mehreren Milliarden.

Rückblickend auf Anfang des vierten Quartals 4 kündigte S2020C die Unterstützung für die damals neuen Xilinx VU2P UltraScale+ FPGAs an und bietet Single-, Dual- und Quad-FPGA-Prototyping-Plattformen. Im Dezember 19 folgte dann die Ankündigung von S2020C mit der Ankündigung seiner hochdichten Prodigy Logic Matrix-Familie von Prototyping-Plattformen mit 2 FPGAs pro Logic Matrix, 8 Logic Matrix pro einzelnem Server-Rack (8 FPGAs) und der Verbindung mehrerer Server-Racks zusammen. Die ersten Iterationen von Logic Matrix wurden mit Xilinx VU64 FPGAs (genannt „.“) ausgeliefert LX1) an frühe Kunden, die nicht auf die VU19P-Version (genannt „.“) warten konnten LX2).

Jetzt erweitert S2C sein Logic Matrix-Spiel mit dem LX2, was die nutzbare Gate-Kapazität im Prototyping um 60 % gegenüber der VU440-Version steigert! Mehr nutzbare Gates pro FPGA bedeuten weniger FPGAs, weniger FPGA-Verbindungen und eine höhere Leistung bei demselben Prototyp-Design. Mit einer geschätzten Torkapazität von 392 Millionen Toren pro Jahr LX2, ein voll bestücktes Standard-Server-Rack mit 8 LX2 ermöglicht eine geschätzte Prototyping-Kapazität von über 3 Milliarden ASIC-Gates!

Abbildung 1: Prodigy Logic Matrix LX2

| Prodigy Logic Matrix-Familie | ||

| LX1 | LX2 | |

| FPGA | XCVU440 | XCVU19P |

| Geschätzte ASIC-Gates (M) | 240 | 392 |

| Anzahl der FPGAs | 8 | 8 |

| Systemlogikzellen (K) | 44,328 | 71,504 |

| FPGA-Speicher (MB) | 709 | 1,327.2 |

| DSP-Slices | 23,040 | 30,720 |

| Externe Benutzer-E/As | 9,216 | 10,368 |

| SerDes-Transceiver | 384 GTH | 640 GTY |

| Prodigy-Anschlüsse | 64 | 72 |

| PGT-Anschlüsse | 8 | 0 |

| Transceiver-Anschlüsse | 80 MSAS mit jeweils 4 GTH + 8 IOs | 160 MCIO mit jeweils 4 GTY + 8 IOs |

| SerDes-Leistung | 16 Gbps | 28 Gbps |

Abbildung 2: Logic-Matrix-Familie

Flexible Hochgeschwindigkeitsverbindungen sind der Schlüssel zum FPGA-Prototyping mit hoher Dichte, und Logic Matrix unterstützt eine hierarchische, dreistufige Verbindungsstrategie: ShortBridge zur Verbindung zwischen benachbarten FPGAs; SysLink für FPGA-Kabelverbindungen mit hoher Bandbreite und TransLink Für längere FPGA-SerDes-Verbindungen über MCIO-Kabel. Um die FPGA-Verbindung zu vereinfachen und den Wert zu maximieren TransLinkDer Partitionierungsfluss von S2C unterstützt das neu eingeführte High-Speed Transceiver Pin Multiplexing (HSTPM) von Xilinx und vereinfacht die zyklusgenaue Signalübertragung, das Pin-Multiplexing und die SerDes-FPGA-Konnektivität mit geringer Latenz.

Um die Zeit bis zum Prototyping zu minimieren und die Prototyping-Produktivität zu maximieren, wurden die anderen Prototyping-Produktivitätstools von S2C unter Berücksichtigung von Logic Matrix entwickelt, darunter Player Pro-Laufzeit Software – und zusätzliche S2C-Prototyping-Tools einschließlich ProtoBridge, MDM-Profiund S2Cs Prototypenbereites IP.

Player Pro-Laufzeit Software ist im Lieferumfang enthalten LX2und bietet praktische Funktionen wie erweitertes Taktmanagement, integrierten Selbsttest, automatische Platinenerkennung, I/O-Spannungsprogrammierung, mehrere FPGA-Downloads sowie Fernüberwachung und -verwaltung des Systems. Ebenfalls enthalten ist AXEVision, ein integriertes AXI-over-Ethernet-Debugging-Tool zur Vereinfachung des Remote-Debugging von AXI-bezogenen Designs.

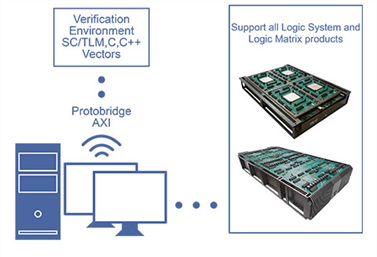

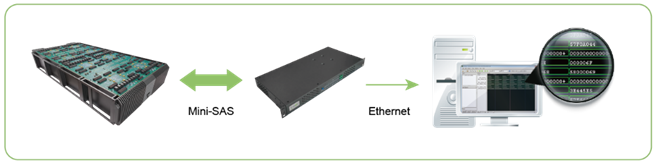

ProtoBridge unterstützt Datenübertragungen mit hohem Durchsatz (bis zu 1 GB/s) zwischen dem Host-PC und dem LX2 – Ermöglicht die Übertragung großer Mengen softwaremodellierter Transaktionen, Videostreams oder anderer Teststimuli zur Systemvalidierung.

Abbildung 3: ProtoBridge

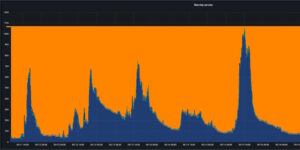

MDM-Profi Bietet umfassendes Trace-Debugging mit Cross-Triggern für bis zu acht FPGAs, Multi-FPGA-Signal-Trace-Anzeige in einem einzigen Anzeigefenster, 64 GB externen Trace-Wellenformspeicher, Trace-Abtastraten von bis zu 125 MHz und unterstützt Trigger-State-Machine-Sprachen für komplexe Trace-Erfassungen Anforderungen.

Abbildung 4: MDM Pro

S2C's bietet auch eine umfangreiche Bibliothek von Prototypenbereites IP für die LX2 – Plug-and-Play-Tochterkarten – die die Erstellung der Prototyping-Umgebung rund um den FPGA-Prototyp beschleunigen.

Abbildung 5: Prototypenfähige IP-Tochterkarten

Wunderkind-Logikmatrix LX2 ist ab sofort verfügbar. Für weitere Informationen wenden Sie sich bitte an Ihren örtlichen S2C-Vertriebsmitarbeiter oder besuchen Sie uns www.s2ceda.com.

Teile diesen Beitrag über: Quelle: https://semiwiki.com/prototyping/s2c-eda/304634-s2c-delivers-on-plan-to-scale-up-fpga-prototyping-platforms-to-billions-of-gates/- 2020

- Erweiterung

- angekündigt

- Ankündigung

- um

- ASIC

- Verfügbarkeit

- Milliarde

- Tafel

- Kabel

- Kapazität

- Verbindung

- Konnektivität

- Kunden

- technische Daten

- liefern

- Design

- Entdeckung

- Abstand

- Früh

- Arbeitsumfeld

- Familie

- Eigenschaften

- Feige

- Vorname

- Fluss

- FPGA

- Spiel

- Gates

- Global

- HTTPS

- Einschließlich

- Information

- Intel

- IP

- Wesentliche

- Sprachen

- grosse

- neueste

- Bibliothek

- aus einer regionalen

- Management

- Matrix

- Million

- Überwachung

- bieten

- Angebote

- Andere

- PC

- Leistung

- Plattform

- Plattformen

- Pro

- PRODUKTIVITÄT

- Produktivitätswerkzeuge

- Programmierung

- Prototyping

- Honorar

- Voraussetzungen:

- Vertrieb

- vergrößern

- Software

- Lösungen

- Bundesstaat

- Stimulus

- Lagerung

- Strategie

- Ströme

- Support

- Unterstützt

- System

- Test

- Transaktionen

- Wert

- Video

- warten

- WHO