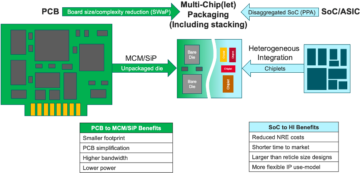

Experten am Tisch: Semiconductor Engineering setzte sich zusammen, um mit Frank Ferro, Gruppenleiter Produktmanagement bei, über den weiteren Weg für Speicher in zunehmend heterogenen Systemen zu sprechen Kadenz; Steven Woo, Kollege und angesehener Erfinder bei Rambus; Jongsin Yun, Speichertechnologe bei Siemens EDA; Randy White, Programmmanager für Speicherlösungen bei Keysight; und Frank Schirrmeister, Vizepräsident für Lösungen und Geschäftsentwicklung bei Arterien. Was folgt, sind Auszüge aus diesem Gespräch. Teil eins dieser Diskussion finden Sie hier hier.

![[L-R]: Frank Ferro, Cadence; Steven Woo, Rambus; Jongsin Yun, Siemens EDA; Randy White, Keysight; und Frank Schirrmeister, Arteris.](https://platoaistream.com/wp-content/uploads/2024/01/rethinking-memory.png)

[L-R]: Frank Ferro, Cadence; Steven Woo, Rambus; Jongsin Yun, Siemens EDA; Randy White, Keysight; und Frank Schirrmeister, Arteris

SE: Welche Konfigurationen müssen überdacht werden, da wir mit KI/ML und Leistungsanforderungen zu kämpfen haben? Werden wir eine Abkehr von der Von-Neumann-Architektur erleben?

Umwerben: Was die Systemarchitekturen angeht, gibt es in der Branche eine Spaltung. Die traditionellen Anwendungen, die die dominierenden Arbeitspferde sind und die wir in der Cloud auf x86-basierten Servern ausführen, werden nicht verschwinden. Es gibt Jahrzehnte von Software, die aufgebaut und weiterentwickelt wurde und deren gute Leistung auf dieser Architektur beruht. Im Gegensatz dazu ist KI/ML eine neue Klasse. Die Leute haben die Architekturen überdacht und sehr domänenspezifische Prozessoren gebaut. Wir sehen, dass etwa zwei Drittel der Energie nur für die Übertragung der Daten zwischen einem Prozessor und einem HBM-Gerät aufgewendet werden, während nur etwa ein Drittel für den tatsächlichen Zugriff auf die Bits in den DRAM-Kernen aufgewendet wird. Die Datenverschiebung ist jetzt viel anspruchsvoller und teurer. Wir werden die Erinnerung nicht loswerden. Wir brauchen es, weil die Datensätze immer größer werden. Die Frage ist also: „Was ist der richtige Weg für die Zukunft?“ Über das Stapeln wurde viel diskutiert. Wenn wir diesen Speicher direkt auf den Prozessor legen würden, würde das zwei Dinge für Sie tun. Erstens wird die Bandbreite heutzutage durch die Uferfront oder den Umfang des Chips begrenzt. Dorthin gehen die I/Os. Wenn Sie ihn jedoch direkt auf den Prozessor stapeln, können Sie jetzt die gesamte Fläche des Chips für verteilte Verbindungen nutzen und mehr Bandbreite im Speicher selbst nutzen, der direkt nach unten eingespeist werden kann der Prozessor. Die Verbindungen werden viel kürzer und die Energieeffizienz steigt wahrscheinlich um das Fünffache bis Sechsfache. Zweitens erhöht sich die Bandbreite, die Sie aufgrund der größeren Array-Verbindung zum Speicher erhalten können, ebenfalls um einen ganzzahligen Faktor. Durch die Kombination dieser beiden Dinge kann mehr Bandbreite bereitgestellt und der Betrieb energieeffizienter gemacht werden. Die Branche entwickelt sich entsprechend den Anforderungen weiter, und das ist definitiv eine Möglichkeit, wie sich Speichersysteme in Zukunft weiterentwickeln werden, um energieeffizienter zu werden und mehr Bandbreite bereitzustellen.

Eisen: Als ich etwa 2016 begann, an HBM zu arbeiten, fragten einige der fortgeschritteneren Kunden, ob es gestapelt werden könne. Sie haben schon seit Längerem darüber nachgedacht, wie man den DRAM obendrauf stapeln kann, weil es klare Vorteile gibt. Auf der physikalischen Ebene wird der PHY grundsätzlich vernachlässigbar, was viel Strom und Effizienz spart. Aber jetzt haben Sie einen Prozessor mit mehreren 100 W, der über einen Speicher verfügt. Die Erinnerung kann der Hitze nicht standhalten. Es ist wahrscheinlich das schwächste Glied in der Wärmekette, was eine weitere Herausforderung darstellt. Es gibt Vorteile, aber sie müssen noch herausfinden, wie sie mit der Thermik umgehen. Es besteht jetzt ein größerer Anreiz, diese Art von Architektur voranzutreiben, da Sie dadurch insgesamt Leistung und Strom einsparen und Ihre Recheneffizienz verbessern. Es gibt jedoch einige physische Designherausforderungen, die bewältigt werden müssen. Wie Steve sagte: Wir sehen alle möglichen Architekturen, die herauskommen. Ich stimme voll und ganz zu, dass die GPU/CPU-Architekturen nicht verschwinden werden, sondern immer noch dominant sein werden. Gleichzeitig versucht jedes Unternehmen auf der Welt, eine bessere Mausefalle für seine KI zu entwickeln. Wir sehen On-Chip-SRAM und Kombinationen aus Speicher mit hoher Bandbreite. LPDDR hat in letzter Zeit ziemlich viel Aufsehen erregt, wenn es darum geht, wie man LPDDR aufgrund der Leistung im Rechenzentrum nutzen kann. Wir haben sogar gesehen, dass GDDR in einigen KI-Inferenzanwendungen sowie in allen alten Speichersystemen verwendet wird. Sie versuchen nun, so viele DDR5-Speicher wie möglich auf einer Stellfläche unterzubringen. Ich habe jede erdenkliche Architektur gesehen, egal ob DDR, HBM, GDDR oder andere. Es hängt von Ihrem Prozessorkern ab, wie hoch Ihr Gesamtwert ist und wie Sie Ihre spezielle Architektur durchbrechen können. Das dazugehörige Speichersystem, damit Sie Ihre CPU und Ihre Speicherarchitektur je nach Verfügbarkeit anpassen können.

Und ein: Ein weiteres Problem ist die Nichtvolatilität. Wenn die KI beispielsweise mit dem Leistungsintervall zwischen der Ausführung einer IoT-basierten KI zurechtkommen muss, dann benötigen wir viel Strom aus und ein, und all diese Informationen für das KI-Training müssen immer wieder rotieren. Wenn wir Lösungen haben, mit denen wir diese Gewichte im Chip speichern können, sodass wir nicht immer für das gleiche Gewicht hin- und herfahren müssen, dann wird das eine Menge Energie einsparen, insbesondere für IoT-basierte KI. Es wird eine andere Lösung geben, um diesen Energiebedarf zu decken.

Schirrmeister: Was mich aus NoC-Perspektive fasziniert, ist, dass man diese Pfade von einem Prozessor, der über einen NoC läuft, bis hin zum Zugriff auf eine Speicherschnittstelle mit einem Controller, der möglicherweise über UCIe geht, optimieren muss, um einen Chiplet an einen anderen Chiplet weiterzuleiten, der dann über Speicher verfügt Es. Es ist nicht so, dass Von-Neumann-Architekturen tot wären. Aber es gibt mittlerweile so viele Variationen, je nachdem, welche Arbeitslast Sie berechnen möchten. Sie müssen im Kontext des Gedächtnisses betrachtet werden, und das Gedächtnis ist nur ein Aspekt. Woher beziehen Sie die Daten aus der Datenlokalität? Wie sind sie in diesem DRAM angeordnet? Wir arbeiten an all diesen Dingen, wie zum Beispiel der Leistungsanalyse von Speichern und der anschließenden Optimierung der Systemarchitektur darauf. Es treibt viele Innovationen für neue Architekturen voran, woran ich nie gedacht hätte, als ich an der Universität etwas über Von Neumann lernte. Am äußersten anderen Ende gibt es Dinge wie Netze. Mittlerweile gibt es eine ganze Reihe weiterer Architekturen, die in Betracht gezogen werden müssen, und dies hängt von der Speicherbandbreite, den Rechenkapazitäten usw. ab, die nicht im gleichen Tempo wachsen.

Weiß: Es gibt einen Trend zu disaggregierter Datenverarbeitung oder verteilter Datenverarbeitung, was bedeutet, dass dem Architekten mehr Tools zur Verfügung stehen müssen. Die Speicherhierarchie hat sich erweitert. Enthalten sind Semantik sowie CXL und verschiedene Hybridspeicher, die für Flash und im DRAM verfügbar sind. Eine parallele Anwendung zum Rechenzentrum ist die Automobilindustrie. In der Automobilindustrie wurde dieser Sensor schon immer mit ECUs (elektronischen Steuergeräten) verrechnet. Ich bin fasziniert davon, wie es sich zum Rechenzentrum entwickelt hat. Schneller Vorlauf, und heute haben wir verteilte Rechenknoten, sogenannte Domänencontroller. Das ist gleich. Es wird versucht, darauf einzugehen, dass die Leistung möglicherweise keine so große Rolle spielt, weil die Größe von Computern nicht so groß ist, aber die Latenz ist im Automobilbereich sicherlich eine große Sache. ADAS benötigt eine extrem hohe Bandbreite, und Sie müssen verschiedene Kompromisse eingehen. Und dann gibt es mehr mechanische Sensoren, aber ähnliche Einschränkungen in einem Rechenzentrum. Sie haben Cold Storage, der keine geringe Latenz haben muss, und dann haben Sie andere Anwendungen mit hoher Bandbreite. Es ist faszinierend zu sehen, wie sehr sich die Werkzeuge und Möglichkeiten für den Architekten weiterentwickelt haben. Die Branche hat wirklich gut reagiert und wir alle bieten verschiedene Lösungen an, die in den Markt einfließen.

SE: Wie haben sich Speicherdesign-Tools entwickelt?

Schirrmeister: Als ich in den 90er Jahren mit meinen ersten Chips begann, war Excel das am häufigsten verwendete Systemtool. Seitdem habe ich immer gehofft, dass es bei den Dingen, die wir auf Systemebene, Speicher, Bandbreitenanalyse usw. tun, irgendwann kaputt gehen könnte. Das hat meine Teams ziemlich stark beeinflusst. Damals war es eine sehr fortschrittliche Sache. Aber Randy meint, dass jetzt bestimmte komplexe Dinge mit einer Genauigkeit simuliert werden müssen, die zuvor ohne die Berechnung nicht möglich war. Um ein Beispiel zu nennen: Die Annahme einer bestimmten Latenz für einen DRAM-Zugriff kann zu schlechten Architekturentscheidungen und möglicherweise zu einer falschen Gestaltung der Datentransportarchitekturen auf dem Chip führen. Die Kehrseite ist auch wahr. Wenn Sie immer vom schlimmsten Fall ausgehen, überdimensionieren Sie die Architektur. Wenn Tools die DRAM- und Leistungsanalyse durchführen und die richtigen Modelle für die Controller zur Verfügung stehen, kann ein Architekt alles simulieren. Das ist eine faszinierende Umgebung. Meine Hoffnung aus den 90er Jahren, dass Excel irgendwann einmal scheitern könnte Das Tool auf Systemebene könnte tatsächlich wahr werden, da bestimmte der dynamischen Auswirkungen in Excel nicht mehr möglich sind, weil Sie sie simulieren müssen – insbesondere, wenn Sie eine Die-to-Die-Schnittstelle mit PHY-Eigenschaften und dann eine Verbindungsschicht hinzufügen Eigenschaften wie die Überprüfung, ob alles korrekt war und ggf. das erneute Versenden von Daten. Wenn diese Simulationen nicht durchgeführt werden, wird die Architektur suboptimal sein.

Eisen: Der erste Schritt bei den meisten Bewertungen, die wir durchführen, besteht darin, ihnen den Speicherteststand zur Verfügung zu stellen, um mit der Prüfung der DRAM-Effizienz zu beginnen. Das ist ein großer Schritt, selbst wenn man so einfache Dinge wie die Ausführung lokaler Tools für die DRAM-Simulation erledigt und dann zu vollständigen Simulationen übergeht. Wir sehen, dass immer mehr Kunden nach dieser Art von Simulation fragen. Sicherzustellen, dass Ihre DRAM-Effizienz im oberen 90er-Bereich liegt, ist ein sehr wichtiger erster Schritt bei jeder Bewertung.

Umwerben: Ein Grund für den Aufstieg vollständiger Systemsimulationstools ist, dass DRAMs viel komplizierter geworden sind. Mittlerweile ist es sehr schwierig, mit einfachen Tools wie Excel bei manchen dieser komplexen Arbeitslasten auch nur in der Lage zu sein. Wenn Sie sich die Datenblätter für DRAM in den 90er Jahren ansehen, waren diese etwa 40 Seiten lang. Jetzt sind es Hunderte von Seiten. Das spricht nur für die Komplexität des Geräts, um die hohen Bandbreiten herauszuholen. Dies hängt mit der Tatsache zusammen, dass der Arbeitsspeicher einen großen Einfluss auf die Systemkosten sowie auf die Bandbreite und Latenz im Zusammenhang mit der Leistung des Prozessors hat. Es ist auch ein großer Treiber für die Leistung, sodass Sie jetzt auf einer viel detaillierteren Ebene simulieren müssen. In Bezug auf den Tool-Flow wissen Systemarchitekten, dass der Speicher ein großer Treiber ist. Daher müssen die Tools ausgefeilter sein und sich sehr gut mit anderen Tools verbinden lassen, damit der Systemarchitekt den besten Gesamtüberblick darüber erhält, was vor sich geht – insbesondere darüber, wie sich der Speicher auf das System auswirkt.

Und ein: Auf dem Weg zum KI-Zeitalter werden viele Multi-Core-Systeme verwendet, aber wir wissen nicht, welche Daten wohin gehen. Es verläuft auch paralleler zum Chip. Der Speicher ist um einiges größer. Wenn wir die ChatGPT-Art der KI verwenden, erfordert die Datenverarbeitung für die Modelle etwa 350 MB Daten, was allein für eine Gewichtung eine riesige Datenmenge ist, und die tatsächliche Eingabe/Ausgabe ist viel größer. Dieser Anstieg der erforderlichen Datenmenge bedeutet, dass es viele probabilistische Effekte gibt, die wir bisher noch nicht gesehen haben. Es ist ein äußerst anspruchsvoller Test, alle Fehler im Zusammenhang mit dieser großen Speichermenge zu erkennen. Und ECC wird überall verwendet, sogar bei SRAM, wo ECC traditionell nicht verwendet wurde, mittlerweile aber bei den größten Systemen weit verbreitet ist. Das Testen all dessen ist eine große Herausforderung und muss durch EDA-Lösungen unterstützt werden, um all diese unterschiedlichen Bedingungen zu testen.

SE: Vor welchen Herausforderungen stehen Ingenieurteams täglich?

Weiß: An jedem beliebigen Tag finden Sie mich im Labor. Ich krempele die Ärmel hoch und mache mir die Hände schmutzig, stochere in Drähten herum, löte und so weiter. Ich denke viel über die Post-Silicon-Validierung nach. Wir sprachen über frühe Simulation und On-Die-Tools – BiST und ähnliches. Letztendlich möchten wir vor der Auslieferung irgendeine Form der Systemvalidierung oder Tests auf Geräteebene durchführen. Wir haben darüber gesprochen, wie man die Erinnerungsmauer überwinden kann. Wir verorten Erinnerungen, HBM und solche Dinge. Wenn wir uns die Entwicklung der Verpackungstechnologie ansehen, haben wir mit Bleiverpackungen begonnen. Sie waren nicht sehr gut für die Signalintegrität. Jahrzehnte später wechselten wir zu optimierter Signalintegrität, wie zum Beispiel Ball Grid Arrays (BGAs). Wir konnten nicht darauf zugreifen, was bedeutete, dass Sie es nicht testen konnten. Also entwickelten wir dieses Konzept namens „Device Interposer“ – einen BGA-Interposer – und das ermöglichte es uns, eine spezielle Vorrichtung dazwischen zu platzieren, die die Signale weiterleitet. Dann könnten wir es an die Testausrüstung anschließen. Spulen wir bis heute vor, und jetzt haben wir HBM und Chiplets. Wie platziere ich mein Gerät dazwischen auf dem Silikon-Interposer? Wir können nicht, und das ist der Kampf. Es ist eine Herausforderung, die mich nachts wach hält. Wie führen wir eine Fehleranalyse vor Ort bei einem OEM- oder Systemkunden durch, bei dem dieser nicht die Effizienz von 90 % erreicht? Es gibt weitere Fehler im Link, sie können nicht richtig initialisiert werden und das Training funktioniert nicht. Handelt es sich um ein Systemintegritätsproblem?

Schirrmeister: Würden Sie dies nicht lieber von zu Hause aus mit einer virtuellen Schnittstelle tun, als zu Fuß ins Labor zu gehen? Ist die Antwort nicht mehr Analyse, die Sie in den Chip integrieren? Mit Chiplets integrieren wir alles noch weiter. Es ist eigentlich keine Option, Ihren Lötkolben dort reinzubringen, daher muss es eine Möglichkeit für On-Chip-Analysen geben. Wir haben das gleiche Problem mit dem NoC. Die Leute schauen sich das NoC an, und Sie senden die Daten und dann sind sie weg. Wir müssen die Analysen dort integrieren, damit die Leute Fehler beheben können, und das erstreckt sich auch auf die Fertigungsebene, damit Sie endlich von zu Hause aus arbeiten und alles auf der Grundlage von Chip-Analysen erledigen können.

Eisen: Vor allem bei Speicher mit hoher Bandbreite kommt man physisch nicht hinein. Wenn wir den PHY lizenzieren, haben wir auch ein passendes Produkt, sodass Sie jedes einzelne dieser 1,024 Bits im Blick haben können. Sie können mit dem Lesen und Schreiben von DRAM über das Tool beginnen, sodass Sie nicht physisch hineingehen müssen. Die Interposer-Idee gefällt mir. Während des Tests entfernen wir einige Pins aus dem Interposer, was im System nicht möglich ist. Es ist wirklich eine Herausforderung, in diese 3D-Systeme einzusteigen. Sogar aus Sicht des Design-Tool-Flows scheinen die meisten Unternehmen für viele dieser 2.5D-Tools ihren eigenen individuellen Flow zu verwenden. Wir beginnen damit, eine standardisiertere Methode zum Aufbau eines 2.5D-Systems zu entwickeln, von der Signalintegrität über die Leistung bis hin zum gesamten Ablauf.

Weiß: Ich hoffe, dass wir auch im weiteren Verlauf das gleiche Maß an Genauigkeit beibehalten können. Ich bin Mitglied der UCIe-Formfaktor-Compliance-Gruppe. Ich überlege, wie man einen bekanntermaßen guten Würfel, einen goldenen Würfel, charakterisiert. Letztendlich wird dies viel mehr Zeit in Anspruch nehmen, aber wir werden einen guten Mittelweg zwischen der Leistung und Genauigkeit der Tests, die wir benötigen, und der eingebauten Flexibilität finden.

Schirrmeister: Wenn ich mir Chiplets und ihre Einführung in einer offeneren Produktionsumgebung anschaue, ist das Testen eine der größeren Herausforderungen, damit es richtig funktioniert. Wenn ich ein großes Unternehmen bin und alle Aspekte kontrolliere, kann ich die Dinge angemessen einschränken, sodass Tests usw. möglich sind. Wenn ich dem UCIe-Slogan folgen möchte, dass UCI nur einen Buchstaben von PCI entfernt ist, und ich mir eine Zukunft vorstelle, in der die UCIe-Baugruppe aus Fertigungssicht wie heutige PCI-Steckplätze in einem PC wird, dann sind die Testaspekte dafür wirklich wichtig herausfordernd. Wir müssen eine Lösung finden. Es gibt viel zu tun.

Ähnliche Artikel

Die Zukunft der Erinnerung (Teil 1 der obigen Rundung)

Von Versuchen zur Lösung von Wärme- und Stromversorgungsproblemen bis hin zu den Rollen von CXL und UCIe bietet die Zukunft eine Reihe von Möglichkeiten für den Speicher.

- SEO-gestützte Content- und PR-Distribution. Holen Sie sich noch heute Verstärkung.

- PlatoData.Network Vertikale generative KI. Motiviere dich selbst. Hier zugreifen.

- PlatoAiStream. Web3-Intelligenz. Wissen verstärkt. Hier zugreifen.

- PlatoESG. Kohlenstoff, CleanTech, Energie, Umwelt, Solar, Abfallwirtschaft. Hier zugreifen.

- PlatoHealth. Informationen zu Biotechnologie und klinischen Studien. Hier zugreifen.

- Quelle: https://semiengineering.com/rethinking-memory/

- :hast

- :Ist

- :nicht

- :Wo

- $UP

- 1

- 2016

- 3d

- 40

- a

- LiveBuzz

- oben

- Zugang

- Zugriff

- Genauigkeit

- präsentieren

- berührt das Schneidwerkzeug

- ADAs

- hinzufügen

- Adresse

- Adoption

- advanced

- Vorteil

- Vorteilen

- aufs Neue

- AI

- KI-Training

- AI / ML

- Alle

- erlaubt

- erlaubt

- ebenfalls

- immer

- Betrag

- an

- Analyse

- Analytik

- und

- Ein anderer

- beantworten

- jedem

- nicht mehr

- von jedem Standort

- Anwendung

- Anwendungen

- passend

- Architekten

- Architektur

- SIND

- Bereich

- um

- vereinbart worden

- Feld

- AS

- fragen

- Aussehen

- Aspekte

- Versammlung

- annehmen

- At

- Versuche

- Automobilindustrie

- verfügbar

- ein Weg

- Zurück

- Badewanne

- Ball

- Bandbreite

- Bar

- basierend

- Grundsätzlich gilt

- Grundlage

- BE

- weil

- werden

- wird

- war

- Bevor

- Sein

- Vorteile

- BESTE

- Besser

- zwischen

- Big

- größer

- Bit

- Break

- bringen

- bauen

- erbaut

- Geschäft

- Geschäftsentwicklung

- aber

- by

- Kadenz

- namens

- kam

- CAN

- Kann bekommen

- Fähigkeiten

- Häuser

- Center

- sicher

- sicherlich

- Kette

- challenges

- Herausforderungen

- herausfordernd

- Charakteristik

- charakterisieren

- Überprüfung

- Chip

- Pommes frites

- Klasse

- klar

- Cloud

- Kälte

- Cold Storage

- Kombinationen

- wie die

- Kommen

- gemeinsam

- Unternehmen

- Unternehmen

- Komplex

- Komplexität

- Compliance

- kompliziert

- Berechnen

- Computer

- Computing

- konzept

- Bedingungen

- Vernetz Dich

- betrachtet

- Einschränkungen

- Kontext

- Kontrast

- Smartgeräte App

- Controller

- Gespräch

- Kernbereich

- und beseitigen Muskelschwäche

- Kosten

- könnte

- Paar

- CPU

- schafft

- Kunde

- Kunden

- technische Daten

- Data Center

- Datensätze

- Tag

- Täglich, von Tag zu Tag

- Tage

- tot

- Deal

- Jahrzehnte

- Entscheidungen

- definitiv

- Anforderungen

- Abhängig

- hängt

- Design

- Entwerfen

- detailliert

- Entwicklung

- Gerät

- Sterben

- anders

- schwer

- Direkt

- Direktor

- Diskussion

- Abfluss

- Distinguished

- verteilt

- Verteiltes rechnen

- do

- die

- Tut nicht

- Dabei

- Domain

- dominant

- erledigt

- Nicht

- nach unten

- angetrieben

- Fahrer

- im

- dynamisch

- Früh

- Effekten

- Effizienz

- effizient

- elektronisch

- Ende

- Energie

- Entwicklung

- Ganz

- Arbeitsumfeld

- Ausrüstung

- Era

- Fehler

- insbesondere

- Äther (ETH)

- Auswertung

- Auswertungen

- Sogar

- schließlich

- Jedes

- alles

- überall

- Evolution

- entwickelt sich

- entwickelt

- entwickelt sich

- Beispiel

- Excel

- ergänzt

- teuer

- erweitert

- Extrem

- äußerst

- Augenfarbe

- Gesicht

- Tatsache

- Faktor

- Scheitern

- faszinierend

- FAST

- möglich

- Kerl

- Treue

- Feld

- Abbildung

- Endlich

- Finden Sie

- Vorname

- Blinken (Flash)

- Flexibilität

- Flip

- Fluss

- folgt

- Fußabdruck

- Aussichten für

- unten stehende Formular

- weiter

- vorwärts

- gefunden

- frank

- für

- voller

- weiter

- Zukunft

- bekommen

- bekommen

- ABSICHT

- gegeben

- Global

- Go

- Goes

- gehen

- Golden

- weg

- gut

- gute Arbeit

- habe

- Gitter

- Gruppe an

- persönlichem Wachstum

- hätten

- Handling

- Hände

- glücklich

- Haben

- mit

- ganzer

- Hilfe

- Hierarchie

- GUTE

- hält

- Startseite

- ein Geschenk

- Ultraschall

- Hilfe

- HTML

- HTTPS

- riesig

- hunderte

- Hybrid

- i

- Idee

- if

- Bild

- wirkt

- Auswirkungen

- wichtig

- zu unterstützen,

- in

- Incentive

- inklusive

- falsch

- Erhöhung

- zunehmend

- Krankengymnastik

- Energiegewinnung

- Information

- Innovation

- innerhalb

- integrieren

- Integrität

- verbindet

- Schnittstelle

- in

- Beteiligung

- Problem

- Probleme

- IT

- SEINE

- selbst

- Job

- nur

- Wissen

- bekannt

- Labor

- grosse

- größer

- höchste

- Latency

- später

- Schicht

- führen

- lernen

- Brief

- Niveau

- Lizenz

- Gefällt mir

- Limitiert

- LINK

- Links

- aus einer regionalen

- aussehen

- suchen

- Los

- viel

- Sneaker

- halten

- um

- Making

- Management

- Manager

- Herstellung

- viele

- Markt

- max-width

- vielleicht

- me

- Mittel

- gemeint

- mechanisch

- mittlere

- Memories

- Memory

- könnte

- für

- mehr

- vor allem warme

- schlauer bewegen

- gerührt

- Bewegung

- ziehen um

- viel

- my

- Need

- Bedürfnisse

- hört niemals

- Neu

- Nacht-

- Fiber Node

- jetzt an

- Anzahl

- of

- WOW!

- Alt

- on

- EINEM

- einzige

- XNUMXh geöffnet

- Entwicklungsmöglichkeiten

- Optimieren

- optimiert

- Optimierung

- Option

- Optionen

- or

- Auftrag

- Andere

- Anders

- Gesamt-

- Überwinden

- besitzen

- Pakete

- Verpackung

- Seiten

- Parallel

- Teil

- besondere

- passieren

- Weg

- Pfade

- PC

- Personen

- ausführen

- Leistung

- Perspektive

- physikalisch

- Physisch

- Stifte

- Planet

- Plato

- Datenintelligenz von Plato

- PlatoData

- Points

- möglich

- möglicherweise

- Werkzeuge

- Präsident

- vorher

- wahrscheinlich

- Aufgabenstellung:

- Prozessor

- Prozessoren

- Produkt

- Produktmanagement

- Produktion

- Programm

- ordnungsgemäße

- richtig

- die

- setzen

- Frage

- ganz

- Erhöhung

- Bewerten

- lieber

- Lesebrillen

- wirklich

- bezogene

- verlassen

- falls angefordert

- erfordert

- lösen

- reagiert

- Folge

- Loswerden

- Recht

- Rise

- Rollen

- Rollen

- Führen Sie

- Laufen

- gleich

- Speichern

- Ersparnisse

- sagen

- Skalieren

- Zweite

- sehen

- Sehen

- scheint

- gesehen

- Semantik

- Halbleiter

- senden

- Sensor

- Sensoren

- Server

- mehrere

- Blätter

- verschieben

- Schiff

- Seite

- Seiten

- Siemens

- Signal

- Signale

- Silizium

- ähnlich

- Einfacher

- Simulation

- Simulationen

- da

- Single

- Größe

- Slots

- So

- Software

- Lösung

- Lösungen

- einige

- anspruchsvoll

- spricht

- besondere

- verbrachte

- Drücken

- Stapel

- gestapelt

- Stapeln

- standardisiert

- Standpunkt

- Anfang

- begonnen

- Beginnen Sie

- Schritt

- Steve

- steven

- Immer noch

- Lagerung

- speichern

- Kämpfen

- so

- Unterstützte

- sicher

- System

- Systeme und Techniken

- Tabelle

- Nehmen

- Reden

- Teams

- Technologe

- Technologie

- AGB

- Test

- Testen

- Tests

- als

- zur Verbesserung der Gesundheitsgerechtigkeit

- Das

- Die Zukunft

- ihr

- Sie

- dann

- Dort.

- Thermal-

- Diese

- vom Nutzer definierten

- Ding

- think

- Dritte

- fehlen uns die Worte.

- diejenigen

- dachte

- Durch

- Zeit

- zu

- heute

- gemeinsam

- Werkzeug

- Werkzeuge

- Top

- TOTAL

- Kompromisse

- traditionell

- traditionell

- Ausbildung

- Transportwesen

- Trend

- was immer dies auch sein sollte.

- Versuch

- XNUMX

- zwei Drittel

- tippe

- verstehen

- Bereiche

- Universität

- us

- -

- benutzt

- Verwendung von

- Bestätigung

- Wert

- Variationen

- verschiedene

- sehr

- Schraubstock

- Vizepräsident:in

- Anzeigen

- Assistent

- von

- Gehen

- Pinnwand

- wollen

- wurde

- Weg..

- we

- Gewicht

- GUT

- waren

- Was

- was auch immer

- wann

- ob

- welche

- während

- Weiß

- ganze

- warum

- werden wir

- mit

- ohne

- umwerben

- Arbeiten

- Von zuhause aus arbeiten

- arbeiten,

- Wurst

- Schreiben

- U

- Ihr

- Zephyrnet