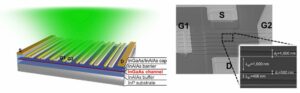

02. Juni 2023 (Nanowerk-Neuigkeiten) Forscher von CEA-Leti haben gezeigt, dass sich Elektronen und andere Ladungsträger in Germanium-Zinn schneller bewegen können als in Silizium oder Germanium, was niedrigere Betriebsspannungen und kleinere Grundflächen in vertikaler Richtung als in planaren Geräten ermöglicht. Dieser Proof-of-Concept-Durchbruch bedeutet, dass vertikale Transistoren aus Germaniumzinn vielversprechende Kandidaten für zukünftige Hochleistungschips mit geringem Stromverbrauch und möglicherweise Quantencomputer sind. Germanium–Zinn Transistoren weisen eine 2.5-fach höhere Elektronenbeweglichkeit auf als ein vergleichbarer Transistor aus reinem Germanium. Ansonsten ist GeSn mit dem Bestehenden kompatibel CMOS-Prozess zur Chipherstellung. Da Germanium und Zinn zur gleichen Gruppe des Periodensystems gehören wie Silizium, könnten diese Transistoren mit bestehenden Produktionslinien direkt in herkömmliche Siliziumchips integriert werden. Ein kürzlich veröffentlichter Artikel in Nachrichtentechnik („Vertikale GeSn-Nanodraht-MOSFETs für CMOS jenseits von Silizium“) stellt fest, dass „GeSn-Legierungen eine einstellbare Energiebandlücke bieten, indem der Sn-Gehalt und einstellbare Bandversätze in epitaktischen Heterostrukturen mit Ge und SiGe variiert werden.“ Tatsächlich hat ein aktueller Bericht gezeigt, dass die Verwendung von Ge0.92Sn0.08 als Quelle auf Ge-Nanodrähten (NWs) verbessert die p-MOSFET-Leistungen.“

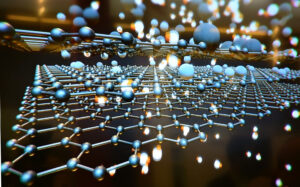

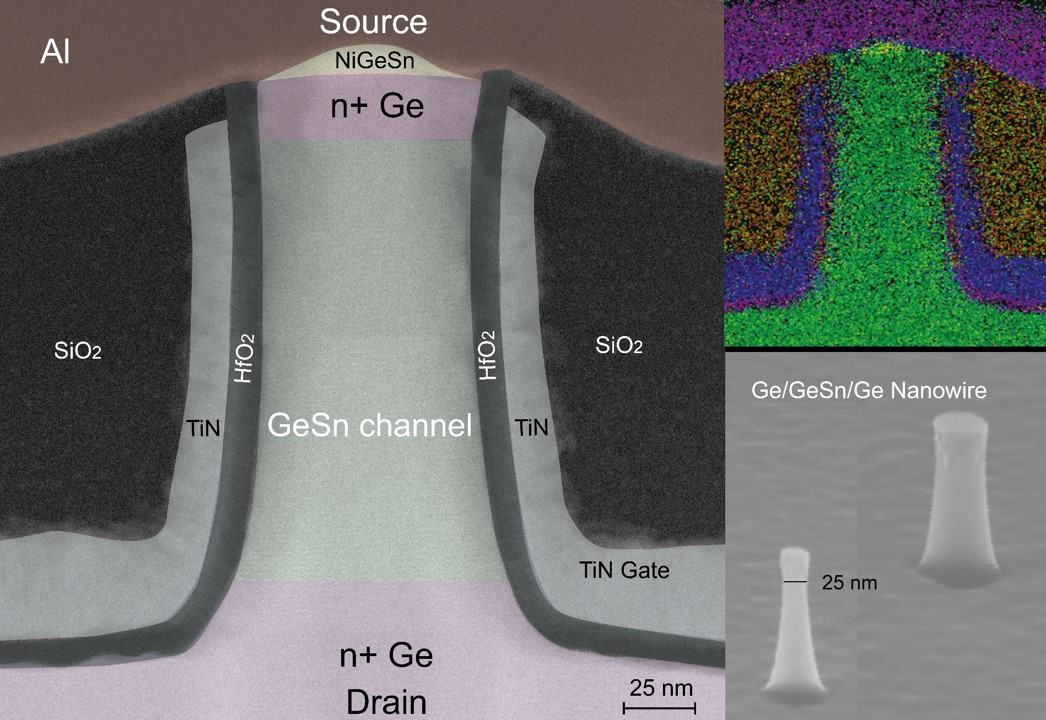

Elektronenmikroskopische Aufnahme des Germanium-Zinn-Transistors: Das Design folgt einer 3D-Nanodraht-Geometrie, die auch in der neuesten Generation von Computerprozessoren verwendet wird. (Bild: Forschungszentrum Jülich) „Zusätzlich zu ihren beispiellosen elektrooptischen Eigenschaften besteht ein großer Vorteil von GeSn-Binärdateien auch darin, dass sie in denselben Epitaxiereaktoren wie Si und SiGe-Legierungen gezüchtet werden können, was eine optoelektronische Halbleiterplattform für alle Gruppen IV ermöglicht.“ das monolithisch auf Si integriert werden kann“, heißt es in dem Papier. Diese Projektforschung umfasste neben CEA-Leti, das die Epitaxiestapel lieferte, auch Beiträge mehrerer Organisationen. Die Epitaxie wird auf einer sehr geordneten Vorlage, einem Siliziumsubstrat, mit einer sehr präzisen Kristallstruktur durchgeführt. Durch die Änderung des Materials duplizierte CEA-Leti seine Diamantkristallstruktur in den darauf aufgetragenen Schichten. „Epitaxie ist die Kunst der Herstellung mehrerer Schichten durch Duplizieren der ursprünglichen Struktur und wird bei niedriger Temperatur mit gasförmigen Vorläufern in einem chemischen Gasphasenabscheidungsreaktor (CVD) durchgeführt“, sagte Jean-Michel Hartmann, CEA-Fellow und Teamleiter, Gruppenleiter. IV-Epitaxie bei CEA-Leti. Die Abscheidung eines solchen Stapels und die Beherrschung des Epitaxieschichtwachstums ist ein äußerst komplexer Schritt in einem Prozessablauf, der strukturierte Zylinder und die Abscheidung eines konformen Gate-Stapels erfordert – kurz gesagt, die Herstellung des gesamten Bauelements. CEA-Leti, eines der wenigen RTOs weltweit, das in der Lage ist, solch komplexe in-situ-dotierte Ge/GeSn-Stapel abzuscheiden, hat diesen Teil der gemeinsamen Forschung durchgeführt, über die in der Arbeit berichtet wird. „Die Zusammenarbeit zeigte das Potenzial von GeSn mit geringer Bandlücke für fortschrittliche Transistoren mit interessanten elektrischen Eigenschaften, wie z. B. hohen Trägermobilitäten im Kanal, niedrigen Betriebsspannungen und einem kleineren Platzbedarf“, erklärte Hartmann, Mitautor des Papiers. „Die Industrialisierung ist noch weit entfernt. Wir treiben den Stand der Technik voran und zeigen das Potenzial von Germaniumzinn als Kanalmaterial.“ An der Arbeit beteiligten sich auch Wissenschaftler des ForschungsZentrums Jülich, Deutschland; die University of Leeds, Vereinigtes Königreich; IHP – Innovationen für Hochleistungsmikroelektronik, Frankfurt (Oder), Deutschland, und RWTH Aachen, Deutschland.

Elektronenmikroskopische Aufnahme des Germanium-Zinn-Transistors: Das Design folgt einer 3D-Nanodraht-Geometrie, die auch in der neuesten Generation von Computerprozessoren verwendet wird. (Bild: Forschungszentrum Jülich) „Zusätzlich zu ihren beispiellosen elektrooptischen Eigenschaften besteht ein großer Vorteil von GeSn-Binärdateien auch darin, dass sie in denselben Epitaxiereaktoren wie Si und SiGe-Legierungen gezüchtet werden können, was eine optoelektronische Halbleiterplattform für alle Gruppen IV ermöglicht.“ das monolithisch auf Si integriert werden kann“, heißt es in dem Papier. Diese Projektforschung umfasste neben CEA-Leti, das die Epitaxiestapel lieferte, auch Beiträge mehrerer Organisationen. Die Epitaxie wird auf einer sehr geordneten Vorlage, einem Siliziumsubstrat, mit einer sehr präzisen Kristallstruktur durchgeführt. Durch die Änderung des Materials duplizierte CEA-Leti seine Diamantkristallstruktur in den darauf aufgetragenen Schichten. „Epitaxie ist die Kunst der Herstellung mehrerer Schichten durch Duplizieren der ursprünglichen Struktur und wird bei niedriger Temperatur mit gasförmigen Vorläufern in einem chemischen Gasphasenabscheidungsreaktor (CVD) durchgeführt“, sagte Jean-Michel Hartmann, CEA-Fellow und Teamleiter, Gruppenleiter. IV-Epitaxie bei CEA-Leti. Die Abscheidung eines solchen Stapels und die Beherrschung des Epitaxieschichtwachstums ist ein äußerst komplexer Schritt in einem Prozessablauf, der strukturierte Zylinder und die Abscheidung eines konformen Gate-Stapels erfordert – kurz gesagt, die Herstellung des gesamten Bauelements. CEA-Leti, eines der wenigen RTOs weltweit, das in der Lage ist, solch komplexe in-situ-dotierte Ge/GeSn-Stapel abzuscheiden, hat diesen Teil der gemeinsamen Forschung durchgeführt, über die in der Arbeit berichtet wird. „Die Zusammenarbeit zeigte das Potenzial von GeSn mit geringer Bandlücke für fortschrittliche Transistoren mit interessanten elektrischen Eigenschaften, wie z. B. hohen Trägermobilitäten im Kanal, niedrigen Betriebsspannungen und einem kleineren Platzbedarf“, erklärte Hartmann, Mitautor des Papiers. „Die Industrialisierung ist noch weit entfernt. Wir treiben den Stand der Technik voran und zeigen das Potenzial von Germaniumzinn als Kanalmaterial.“ An der Arbeit beteiligten sich auch Wissenschaftler des ForschungsZentrums Jülich, Deutschland; die University of Leeds, Vereinigtes Königreich; IHP – Innovationen für Hochleistungsmikroelektronik, Frankfurt (Oder), Deutschland, und RWTH Aachen, Deutschland.

- SEO-gestützte Content- und PR-Distribution. Holen Sie sich noch heute Verstärkung.

- PlatoAiStream. Web3-Datenintelligenz. Wissen verstärkt. Hier zugreifen.

- Die Zukunft prägen mit Adryenn Ashley. Hier zugreifen.

- Kaufen und verkaufen Sie Anteile an PRE-IPO-Unternehmen mit PREIPO®. Hier zugreifen.

- Quelle: https://www.nanowerk.com/nanotechnology-news2/newsid=63102.php

- :hast

- :Ist

- 10

- 3d

- 7

- 8

- 9

- a

- Fähig

- Zusatz

- einstellbar

- advanced

- Vorrückend

- Vorteil

- ebenfalls

- an

- und

- SIND

- Kunst

- AS

- At

- ein Weg

- BAND

- BE

- weil

- Beyond

- Durchbruch

- by

- CAN

- Kandidaten

- durchgeführt

- Träger

- Center

- Ändern

- Kanal

- berechnen

- chemisch

- Chip

- Pommes frites

- Mitverfasser

- Zusammenarbeit

- wie die

- vergleichbar

- kompatibel

- Komplex

- Computer

- Computer

- konzept

- Inhalt

- Beiträge

- konventionellen

- könnte

- Kristall

- Datum

- geliefert

- weisen nach, dass

- zeigt

- Einzahlungen

- Design

- Gerät

- Geräte

- Diamond

- Direkt

- Elektronen

- ermöglichen

- Energie

- Verbessert

- Ganz

- zeigen

- vorhandenen

- erklärt

- äußerst

- Tatsache

- weit

- beschleunigt

- Kerl

- wenige

- Fluss

- folgt

- Fußabdruck

- Aussichten für

- für

- Zukunft

- ge

- Generation

- Geometrie

- Deutschland

- Global

- Gruppe an

- gewachsen

- Wachstum

- Haben

- High

- Hohe Leistungsfähigkeit

- höher

- HTTPS

- Image

- in

- inklusive

- Innovationen

- integriert

- interessant

- in

- IT

- SEINE

- dank

- jpg

- Art

- Reich Gottes

- neueste

- Lagen

- Führer

- Linien

- Sneaker

- gemacht

- Dur

- Making

- Herstellung

- Mastering

- Ihres Materials

- Mittel

- Mitte

- Mobilität

- schlauer bewegen

- Notizen

- of

- bieten

- on

- EINEM

- die

- Betrieb

- or

- Organisationen

- Original

- Andere

- Andernfalls

- Papier

- Teil

- Leistung

- Leistungen

- durchgeführt

- periodisch

- PHP

- Plattform

- Plato

- Datenintelligenz von Plato

- PlatoData

- gegebenenfalls

- Potenzial

- präzise

- Prozessdefinierung

- Prozessoren

- Produktion

- Projekt

- aussichtsreich

- Beweis

- Proof of Concept

- immobilien

- veröffentlicht

- setzen

- Quant

- Quantencomputer

- kürzlich

- kürzlich

- berichten

- Berichtet

- Meldungen

- Forschungsprojekte

- Said

- gleich

- Wissenschaftler

- Halbleiter

- mehrere

- Short

- gezeigt

- Silizium

- kleinere

- Quelle

- Stapel

- Stacks

- Bundesstaat

- Schritt

- Immer noch

- Struktur

- so

- Tabelle

- Team

- Vorlage

- als

- zur Verbesserung der Gesundheitsgerechtigkeit

- Das

- das Gelenk

- Der Staat

- ihr

- Diese

- vom Nutzer definierten

- fehlen uns die Worte.

- mal

- zu

- Top

- Vereinigt

- Großbritannien

- Universität

- beispiellos

- -

- benutzt

- vertikal

- sehr

- we

- welche

- mit

- Arbeiten

- Zephyrnet