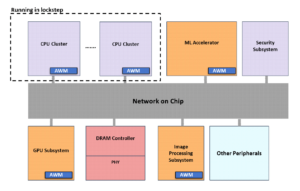

Der alte Satz, dass die Heilung schlimmer ist als die Krankheit, trifft bei der Erörterung von MBIST für große SOCs zu, wo die parallele Ausführung vieler MBIST-Tests die Kapazitäten von Stromverteilungsnetzwerken (PDN) übersteigen kann. Der integrierte Selbsttest des Speichers (MBIST) wird normalerweise automatisch beim Einschalten ausgeführt. Aufgrund des Wunsches, die Test- und Chip-Boot-Zeiten zu verkürzen, werden diese Tests häufig parallel ausgeführt. Das Problem besteht darin, dass sie leicht eine Schaltaktivität erzeugen können, die um eine Größenordnung über den Werten liegt, die beim normalen Chipbetrieb auftreten. Tatsächlich kann diese höhere Schaltaktivität nicht nur zu einem Versorgungsausfall führen, der sich auf die Testergebnisse auswirkt, sondern auch die hohe erzeugte Hitze kann Chips schädigen. Diese Effekte können zu einer falschen Klasseneinteilung oder zu direkten und latenten Ausfällen von Ereignissen führen.

Die Lösung besteht darin, die MBIST-Aktivität zu simulieren, um die Belastung des PDN und die damit verbundenen thermischen Effekte vorherzusagen. Mit den vorliegenden Simulationsergebnissen können Entwickler richtig entscheiden, wie viele und welche Speicherblöcke parallel getestet werden können. Dies ist jedoch in großen SOCs mit vielen Speicherblöcken nicht immer möglich, da die Simulationszeiten möglicherweise unerschwinglich sind. Bei Gate-Level- und noch ungenauerer RTL-Simulation ist es möglicherweise nicht möglich, genügend Zyklen auszuführen, um die benötigten Informationen zu erhalten.

In einem Whitepaper mit dem Titel „Analyse der Energieauswirkungen der MBIST-Nutzung“ untersucht Siemens EDA, wie Designer ausreichend Simulationen durchführen können, um vor dem Tapeout fundierte Entscheidungen über die Teststrategie zu treffen. Siemens arbeitete mit ARM an einem seiner Testchips, um einen Testfall zu erstellen, in dem sie Hardware-Emulation mit den DFT- und Power-Apps für den Siemens-Hardware-Emulator Veloce anwenden konnten. Zunächst wird die Veloce DFT-App verwendet, um die interne Aktivität während der MBIST-Emulation auszugeben. Die App verwendet die Standard Test Interface Language (STIL) und erzeugt branchenübliche Ausgabedateien.

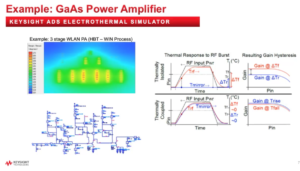

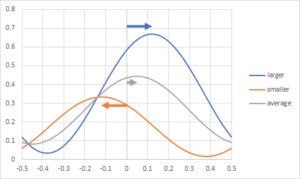

Die Veloce Power-App nutzt die Aktivitätsinformationen der MBIST-Läufe, um Wellenformen, Leistungsprofile und Heatmaps zu erstellen, die anzeigen können, wenn Leistungsspitzen oberhalb bestimmter Grenzwerte auftreten. Mit diesen Informationen können Testingenieure fundierte Entscheidungen über die Sequenzierung von MBIST treffen.

Der im Siemens-Whitepaper beschriebene ARM-Testfall enthält 176 Millionen Tore. Siemens nutzte für diesen Testfall ein Veloce-System mit 6 Veloce Strato-Boards. Der Lauf des Veloce-Emulators dauerte nur 26 Stunden, was 15,600 Mal schneller ist als die Simulation auf Gate-Ebene. Ein weiterer Vorteil des Veloce Flow besteht darin, dass die Aktivitätsinformationen von der Power-App an die Elektrowerkzeuge im Flow gestreamt werden, wodurch Speicherplatz und Zeit gespart werden. Die Ergebnisse des Testfalls zeigten mehrere Leistungsspitzen, die gegen die SOC-Designspezifikationen verstießen. Die Ausgabe der Veloce Power-App zeigt die gesamten Leistungspegel durch die Simulation zusammen mit den einzelnen Leistungsbeiträgen für Takt, kombinatorische Logik und Speicher. Ebenso gibt es Informationen darüber, wo auf dem Würfel die Kraft verbraucht wird. Anhand dieser Informationen lässt sich leicht feststellen, wo Probleme vorliegen.

Um solche Probleme zu finden, müssen Millionen oder Milliarden von Taktzyklen ausgeführt werden. Aufgrund der Einschränkungen von Softwaresimulatoren ist die Durchführung der erforderlichen Analyse unerschwinglich. Die Emulation bietet eine einzigartige Möglichkeit, die Auswirkungen von MBIST und anderen Testvorgängen auf die Energieversorgung lange vor Silizium genau zu untersuchen. Das Siemens-Whitepaper bietet Einblicke in die Energiemethode, die in einem realen Testfall verwendet wird. Das Whitepaper steht zum Lesen auf der Siemens-Website zum Download bereit.

Teile diesen Beitrag über: Quelle: https://semiwiki.com/eda/306889-mbist-power-creates-lurking-danger-for-socs/

- Über uns

- Analyse

- App

- Apps

- ARM

- verfügbar

- Sein

- Verursachen

- Chip

- Pommes frites

- Uhr

- enthält

- könnte

- Heilung

- Design

- Krankheit

- im

- leicht

- Ingenieure

- Event

- Veranstaltungen

- beschleunigt

- Vorname

- Fluss

- gefunden

- Gates

- erzeugen

- Hardware

- High

- Ultraschall

- HTTPS

- Energiegewinnung

- Information

- IT

- Sprache

- grosse

- führen

- Niveau

- Cholesterinspiegel

- Belastung

- Lang

- Landkarten

- Million

- Millionen

- erforderlich

- Netzwerk

- Angebote

- Einkauf & Prozesse

- Auftrag

- Andere

- Papier

- Werkzeuge

- Aufgabenstellung:

- Profil

- Lesebrillen

- Die Ergebnisse

- Führen Sie

- Laufen

- Einsparung

- Siemens

- Simulation

- Software

- Raumfahrt

- Geschwindigkeit

- Strategie

- gestreamt

- liefern

- System

- Test

- Testen

- Tests

- Thermal-

- Durch

- Zeit

- Werkzeuge

- einzigartiges

- gewöhnlich

- Webseite

- WHITE PAPER

- gearbeitet