Das Plasmaätzen ist möglicherweise der wichtigste Prozess in der Halbleiterfertigung und neben der Fotolithographie möglicherweise der komplexeste aller Fertigungsvorgänge. Fast die Hälfte aller Fab-Schritte ist für ihre Arbeit auf ein Plasma, ein energiereiches ionisiertes Gas, angewiesen.

Trotz immer kleiner werdender Transistor- und Speicherzellen liefern Ingenieure weiterhin zuverlässige Ätzprozesse.

„Um nachhaltig Chips mit Präzision im Nanomaßstab und der richtigen Kostenstruktur herzustellen, müssen Hersteller von Waferfertigungsgeräten die Grenzen der Plasmaphysik, der Materialtechnik und der Datenwissenschaft verschieben, um die benötigten Gerätelösungen zu liefern“, sagte Thomas Bondur, Corporate Vice President für Marketing der Etch Product Group bei Lam Research. Nirgendwo wird dies deutlicher als beim Plasmaätzen, das Hand in Hand mit der Lithographie arbeitet, um exakte, wiederholbare Merkmale auf Wafern zu erzeugen.

In diesem Bericht werden wichtige Ätzschritte in 3D-NAND, DRAM, Nanosheet-FETs und Verbindungen untersucht, mit einem Blick in die Zukunft auf 2D-Geräte und Low-Budget-Back-End-Verarbeitung. Die Industrie strebt auch nach nachhaltigeren Ätzchemikalien, um den COXNUMX-Ausstoß zu reduzieren2 Emissionen aus seinen Fabriken.

Für viele Werkzeughersteller spielt die Prozessmodellierung eine zentrale Rolle bei der Entwicklung von Ätzprozessen. Ziel ist es, die Markteinführungszeit zu verkürzen und gleichzeitig die Wafer- und Maskenkosten zu senken.

„Die Optimierung des Ätzprozesses bei einigen der schwierigsten Schritte kann ein Jahr oder länger dauern“, sagte Barrett Finch, Senior Marketing Director bei Lam Research. „Wir haben kürzlich einige Prozesssimulationsarbeiten in drei Wochen abgeschlossen, die bei typischen Tests und Entwicklungen auf Siliziumbasis voraussichtlich drei Monate dauern würden.“

Dies kann allein für die Masken- und Waferkosten eines Geräteherstellers Hunderttausende oder sogar Millionen Dollar betragen.

Grundlagen des Radierens

Der Ätzprozess arbeitet Hand in Hand mit der Lithographie. Dem Ätzen geht typischerweise die Abscheidung eines Films voraus (durch Epitaxie, chemische oder physikalische Gasphasenabscheidung usw.). Typischerweise a CVD Folie ist beschichtet mit Photolack und dann durch ein Muster belichtet Fadenkreuz (Maske) verwenden optische Lithographie (248 nm oder 193 nm UV, 13.5 nm EUV). Die Resistentwicklung zeigt dann das Muster. In einer Einzelwafer-Plasmaätzkammer bombardieren und entfernen die Ätzchemikalien und Ionen typischerweise den CVD-Film dort, wo der Fotolack fehlt (im Positivlack). Nach dem Ätzen Resistenzveraschen, chemische Nassreinigung und/oder Nassätzung durchführen, um Rückstände zu entfernen.

Plasmaätzprozesse können grob in Dielektrikum-, Silizium- oder Leiterätzungen eingeteilt werden. Dielektrika wie Siliziumdioxid und Siliziumnitrid lassen sich am besten mit fluorierten Gasen ätzen, während Silizium- und Metallschichten am besten mit Chlorchemikalien reagieren. Es gibt im Wesentlichen drei Trockenätzmodi: reaktives Ionenätzen, Plasmaätzen und Sputterätzen (Ionenstrahl). Bei Ätzprozessen geht es um die komplexen Wechselwirkungen zwischen den chemischen Reaktanten, dem Plasma und den Wafermaterialien. Wenn eine HF-Vorspannung an ein reaktives Gas angelegt wird, bombardieren Elektronen und positiv geladene Ionen den Wafer, um Material physikalisch zu entfernen (zu ätzen), während die chemischen Spezies und freien Radikale mit dem freigelegten Material reagieren und flüchtige Nebenprodukte bilden. Das Ätzen kann entweder isotrop (gleichmäßig vertikal und horizontal reagierend), anisotrop (nur vertikal) oder irgendwo dazwischen erfolgen.

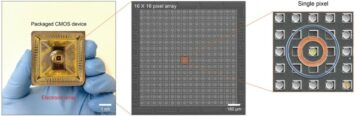

Abb. 1: Der Übergang von FinFET zu GAA führt zu kritischen isotropen selektiven Ätzanforderungen. Quelle: Lam Research

Die Kennzahlen, die den Ätzingenieuren am meisten am Herzen liegen, sind Ätzrate, Profilkontrolle, Gleichmäßigkeit (über den gesamten Wafer) und Ätzselektivität, da diese Auswirkungen auf Ausbeute und Produktivität haben. Die Ätzselektivität ist einfach das Verhältnis der Entfernung des zu ätzenden Materials im Verhältnis zu seiner Unterschicht – zum Beispiel SiO2 auf Silizium. Beim Ätzen ist es außerdem vorteilhaft, nicht zu viel Fotolack zu entfernen. Wenn dies jedoch der Fall ist, wird das Muster häufig auf eine Hartmaske (Siliziumdioxid, Siliziumnitrid, SiOC, TiN) übertragen, bevor es auf den darunter liegenden Film übertragen wird.

Die Selektivitätsspezifikationen variieren von 2:1 bis zu 1,000:1 (hochselektives Ätzen). Mit jedem neuen Knoten werden diese Spezifikationen strenger. „Da EUV mit hoher NA in den nächsten vier Jahren beginnen wird, reguläres EUV zu ersetzen, ist der Fokus viel geringer, sodass man keinen dicken Fotolack mehr belichten kann – und mit dick meine ich 30 Nanometer“, sagte Philippe Bézard, Forschungs- und Entwicklungsingenieur für Trockenätzen bei imec. „Aber Sie müssen unten immer noch die gleiche Filmdicke strukturieren. Jetzt fordern Sie also eine viel höhere Selektivität in dem Sinne, dass wir statt 2:1 eher 10:1 erreichen müssen, was einer plötzlichen Verbesserung der Selektivität um das Vier- bis Fünffache entspricht.“

Vom Proof of Concept (POC) zur Großserienfertigung (HVM)

Bézard beschreibt drei Phasen der Entwicklung des Ätzprozesses:

- Bestimmen, welche Ätzmittel, Gase, Hilfsschichten usw. für die Ätzung erforderlich sind;

- Nachweis der Leistung bei der vollständigen Entfernung von Filmen innerhalb der Spezifikationen mit Prozessgleichmäßigkeit auf einem Wafer und

- Bestimmen, wie der Prozess über Tausende von Wafern in HVM mit hoher Ausbeute und geringer Drift wiederholt werden kann.

In der Regel kümmern sich erfahrene Ätz- und Integrationsingenieure um die ersten beiden Phasen der Entwicklung. In der dritten Phase könnte wiederum technisches Fachwissen zum Einsatz kommen, maschinelles Lernen könnte jedoch hilfreich sein.

„Maschinelles Lernen und Datenanalyse im Allgemeinen sind erst in der dritten Phase sinnvoll“, sagte er. „Es ist sehr leistungsstark, weil es Zugriff auf eine Menge Daten hat und eine Million kleiner, einfacher Dinge verstehen kann, die alle interagieren. Für ein menschliches Gehirn ist es also sehr schwierig, dies herauszufinden, aber für ein Computerprogramm ist es besser zu bewältigen. Aber in Fällen, in denen es um eine neue Anwendung, das Ätzen eines neuen Materials oder eine neue Integration geht, zeigt es keine Verbesserung gegenüber Menschen.“

Der ML-Einsatz betrifft auch die Herstellungskosten, da in Phase drei Tausende von Wafern verwendet werden – mindestens eine Größenordnung mehr als in den Phasen eins und zwei.

Barrett Finch, leitender Direktor der Etch Product Group bei Lam Research, beschreibt die Wegfindung für neue Prozesse als die Annahme eines Proof-of-Concept anhand eines nominalen Prozessablaufs und -layouts und die Entwicklung eines oder mehrerer funktionierender Geräte auf einem Wafer. Dieser POC wird dann an ein Produktentwicklungsteam in der Fabrik übertragen, um den Prozess zu skalieren und die Ausbeute zu verbessern.

„Der Arbeitsaufwand, der erforderlich ist, um einen nominellen Proof-of-Concept in ein brauchbares, ertragreiches Produkt umzuwandeln, wird oft unterschätzt, und dadurch entsteht eine große Lücke zur Rentabilität“, sagte Finch. „Die Prozessfenstermodellierung versucht, diese Lücke zu schließen, indem sie Fab-Variationen in die frühen Phasen der F&E-Pfadfindung einführt.“ Er schlägt vor, dass virtuelle DOEs und Monte-Carlo-basierte Analysen über eine Reihe von Prozessparametern einen POC testen, indem sie die erwartete Variabilität simulieren.

„Die Modellierung von Prozessfenstern kann die Frage beantworten: ‚Welche CD bzw. welches Variabilitätsniveau muss ich einhalten, um die minimale Geräteleistung und -ausbeute zu erreichen?‘ Wir haben in wenigen Tagen virtuelle Prozessfenstertests mit mehr als einer Million virtuellen Wafern durchgeführt, was im wirklichen Leben unmöglich wäre“, sagte er.

Mehrere Parameter beeinflussen Ätzrate, Profil und Selektivität. Ein wichtiger Faktor ist die Temperatur. „Die Auswirkungen thermischer Effekte bei der Ätzverarbeitung werden von unseren Kunden erkannt, wenn sie Ätzraten, Selektivitäten und geätzte Profile steuern. Alle diese Parameter können sich sowohl auf die Geräteausbeute als auch auf die Fertigungsproduktivität auswirken“, sagte Benjamin Vincent, Senior Manager für Halbleiterprozess- und Integrationstechnik bei Lam Research. Er behauptet, dass die Simulation besonders hilfreich sein kann, wenn ein Prozessschritt mehrere mögliche Konfigurationen hat (der Prozessraum ist groß) oder wenn die nachgelagerten Ergebnisse des Schritts höchst unvorhersehbar sind.

„Der Ätzprozess hängt von der Oberflächentemperatur des Wafers ab, die von mehreren Wärmeflüssen abhängt – einschließlich Wärmeleitung, Ionenaufprallenergien, Oberflächenreaktionen und Plasmastrahlungswärmeflüssen“, sagte Alex Guermouche, Produktmarketingmanager bei Esgee Technologies, a Lam Forschungsunternehmen. „Daher müssen Plasmamodelle alle diese physikalischen Merkmale berücksichtigen, um Temperaturänderungen auf der Waferoberfläche genau darzustellen. Prozesssimulationssoftware kann eine Reihe von Ätzattributen modellieren, sodass wir schneller ein besseres Ätzergebnis erzielen und die Fähigkeit des Kunden, die Produktion zu steigern oder die Ausbeute zu optimieren, beschleunigen.“

Präzises Timing des Ätzprozesses

Bei engeren Geometrien und dünneren Filmen besteht die Notwendigkeit, die Ätzrate mit einer guten Kontrolle über andere Betriebsparameter in Einklang zu bringen.

„Angesichts schrumpfender Designregeln gehen viele Ätzprozesse zu sehr schnellen Plasmaätzprozessschritten über, die eine hochpräzise Steuerung aller Reaktionseingänge erfordern: Leistung, Druck, Chemie und Temperatur“, sagte Finch und wies darauf hin, dass es auch einen Trend zu optimiertem Plasma gibt Pulsierendes Verhalten, um ein bestimmtes Ionen-zu-Neutral-Verhältnis zu erzeugen und dann Nebenprodukte wegzufegen. „Eine fortgeschrittene Modellierung solcher Bedingungen wird entscheidend sein, um eine weitere Geräteskalierung zu ermöglichen.“

Hersteller von Ätzsystemen verwenden seit einiger Zeit Modellierungssoftware, um die Entwicklung des nächsten Knotens zu beschleunigen oder die Erträge zu steigern. Angesichts der Komplexität des Prozesses und all seiner Variablen ist dies keine Überraschung.

„Es gibt einfach nicht genug Zeit oder genügend Wafer, um alle möglichen Prozessexperimente bei der Entwicklung von Next-Node-Technologien durchzuführen“, sagte Finch. „Die Anzahl der Einstellungskombinationen für Ätzgeräte kann Millionen oder sogar Milliarden betragen, und die Waferentwicklung mit roher Gewalt unter Ausnutzung aller Prozessmöglichkeiten ist einfach unmöglich.“

Selbstverständlich werden alle guten Modelle anhand tatsächlicher Chips verifiziert. „Ein genaues Modell sollte prädiktiv sein und das Zielproblem lösen, das ein Benutzer lösen möchte“, sagte Finch. „Jedes Mal, wenn eine Prozess- oder Designänderung auf der Grundlage von Simulationsarbeiten empfohlen wird, sollten die tatsächlichen Fabrikdaten die Ergebnisse der Empfehlung widerspiegeln. In unserem Fall konnten wir die Auswirkungen von Prozessänderungen mithilfe modellbasierter Ergebnisse genau vorhersagen und schwierige Probleme bei der Prozess- und Technologieentwicklung schnell lösen.“

Werkzeuglieferanten arbeiten auch an fortschrittlichen Ätzprozessen, um Linien enger zu integrieren und den einstigen Zwei-Masken-Ebenen-Prozess (zwei Lithographieschritte) in einen einzigen Prozess umzuwandeln, um den Prozess zu vereinfachen und Kosten zu senken.

„Anstatt vorhandene Hardware anzupassen, um das Schweizer Taschenmesser noch besser auszustatten, führen Unternehmen anwendungsspezifische Technologien ein, beispielsweise neue Systeme, um Probleme von Spitze zu Spitze zu lösen“, sagte Bézard. Ziel ist es, zwei einander zugewandte Linien näher zusammenzubringen, was derzeit einen Schritt zur Linienmusterung gefolgt von einer Schnittmaske erfordert. „Was Applied Materials und andere einführen, ist eine Möglichkeit, direkt in horizontaler Richtung zu ätzen.“ Solche Prozesse können auch Durchgangslöcher erweitern.

Ätzschritte für Nanoblatt-FETs

Die kritischste Ätzung tritt ein Nanoblatt Zu den Prozessabläufen gehören das Dummy-Gate-Ätzen, das anisotrope Säulenätzen, das isotrope Spacer-Ätzen und der Kanalfreigabeschritt. [1] Die Profilätzung durch abwechselnde Schichten aus Silizium und SiGe ist anisotrop und nutzt fluorierte Chemie. Das Ätzen des inneren Abstandshalters (Einkerbung) und der Kanalfreigabeschritt sind optimiert, um SiGe mit extrem geringem Siliziumverlust zu entfernen.

Der Kanalfreigabeschritt ist entscheidend. „Die Freisetzung des Nanoblatts erfordert eine extrem hohe Selektivität“, sagte Bézard. „Die meisten Nanoblätter bestehen aus Silizium, dann aus Silizium-Germanium und Silizium. Es gibt abwechselnde Schichten und Sie müssen eine entfernen, ohne die andere zu verändern.“ In einigen Veröffentlichungen wurde die Durchführung einer mehrstufigen SiGe-Ätzung diskutiert, um die durch einen einzelnen Ätzschritt verursachte Belastung der Struktur zu reduzieren.

Als nächstes erfolgt die Bildung selbstausrichtender Kontakte. „Hier versuchen wir im Wesentlichen, Siliziumdioxid zu ätzen und das Siliziumnitrid nicht zu berühren oder zu vertiefen. Aktuelle Spezifikationen belaufen sich beispielsweise auf eine Aussparung von 3 nm, aber die Leute fordern null Verlust“, sagte Bézard. „In diesem Fall verwenden wir nicht einmal das Wort Selektivität. Wir reden nur von Pausen – und zwar von null Pausen.“

3D NAND

Aussichten für 3D NAND Bei Flash nimmt die Anzahl der Schichten weiter zu und erfordert in Zukunft die Einführung mehrerer gestapelter Schichten, wodurch schließlich vertikale Reihen gestapelter Geräte entstehen. „Außerdem gibt es große Bestrebungen, den Wortleitungsabstand oder den Vertikal-/Z-Abstand der Schichten zu skalieren, wenn die Anzahl der Schichten zunimmt, um die Bitdichte weiter zu erhöhen“, sagte Robert Clark, leitender Mitarbeiter des technischen Personals Technologiedirektor bei TEL. „Aus prozesstechnischer Sicht müssen Ätz- und Abscheidungsprozesse ständig verbessert werden, um den immer höheren Aspektverhältnissen bei immer kleineren kritischen Abmessungen gerecht zu werden, die eine kontinuierliche Skalierung erfordert.“

Clark beschrieb zukünftige Veränderungen. „Im Hinblick auf fortschrittliche Knoten von Ladungsfallenbauelementen mit mehreren Ebenen wird die Entwicklung der Gate-Stapel erforderlich sein, um kürzere Gate-Längen, mehr Ebenen pro Zelle und eine verbesserte Programmiereffizienz zu erreichen – möglicherweise durch die Verwendung von High-k-Materialien.“ Wahrscheinlich werden in Zukunft auch Kanäle mit höherer Leitfähigkeit erforderlich sein, um Poly-Si-Kanäle zu ersetzen“, sagte er.

Zu den kritischsten Ätzvorgängen bei 3D-NAND gehört das tiefe Ätzen von etwa 100 nm großen Löchern durch mehrschichtige Oxid-Nitrid-Stapel (über 200 Schichten), die bis zu 10 µm tief sein können. Bézard von Imec sagte, dieser Ätzschritt sei besonders teuer.

„Wir haben ein physikalisches Phänomen, das als Differenzaufladungseffekt bezeichnet wird“, sagte er. „Im Plasma haben wir zur Vereinfachung Elektronen, Ionen und neutrale Spezies. Elektronen bewegen sich in alle Richtungen, Ionen werden jedoch senkrecht zur Oberfläche beschleunigt. Es gibt also positive Ladungen am Boden des Lochs und negative Ladungen oben, und es entsteht ein elektrisches Feld, das versucht, einfallende Ionen abzustoßen.“

Daher sind hohe Leistungspegel erforderlich, um den Graben vollständig zu ätzen. „Wir versuchen, eine Leistung von 30 bis 50 Gigawatt ohne Lichtbogenbildung aufrechtzuerhalten, und daher muss das Spannfutter extrem gut poliert und gut gefertigt sein“, sagte er.

Die tiefen Ätzungen verursachen auch Spannungen, die minimiert werden müssen, insbesondere weil die mehrschichtige NAND-Fertigung anschließend eine Waferverdünnung, eine präzise Ausrichtung und eine Hybridverbindung mit der nächsten Schicht erfordert.

Andere Prozesse

Nicht alle Chiphersteller produzieren Spitzenchips, die EUV-Lithographie erfordern. Viele Fabriken erweitern ihre 193-nm-Litho- und Ätzprozesse.

„Wir haben vor kurzem mit der Einführung eines Hochtemperatur-SOC-Materials begonnen, das seine Strukturierungsfähigkeit erweitert und höheren Temperaturen standhalten kann, unabhängig davon, ob es als Unterschicht für eine CVD-Schicht oder Maske verwendet wird“, sagte Brian Wilbur, Direktor für Diversifizierung von Halbleiterprodukten bei Brewer Science.

beol Für die dichtesten Metallleitungen wird voraussichtlich ein dramatischer Übergang von Dual-Damascene-Integrationsschemata zur subtraktiven Abscheidung und Ätzung anderer Verbindungen als Kupfer stattfinden. Hier wurden zwei Metalle – Ruthenium und Molybdän – am gründlichsten entwickelt. Molybdän oxidiert jedoch beim Ätzen eher, wodurch es besser mit Dual-Damascene-Schemata kompatibel ist. Ruthenium ist ein Edelmetall und weist daher nicht die gleichen Korrosionsprobleme auf, ist aber teurer.

Auch Gerätestrukturen werden zunehmend intolerant Kantenplatzierungsfehler. Laut Clark von TEL werden neue Schemata für die Selbstausrichtung von Schicht zu Schicht sowie zwischen Durchkontaktierungen und Leitungen benötigt. „Die ersten Implementierungen werden wahrscheinlich für Dinge wie vergrabene Wortleitungen in DRAM und die MOL-Metallschichten mit kleinem Abstand für die Logik gelten, wo eine höhere thermische Stabilität sowie ein geringerer spezifischer Widerstand oder Metalle ohne Liner erforderlich sind.“

Entwicklungen der nächsten Generation

Langfristig wird die Branche idealerweise auf Back-End-Prozesse mit niedrigerem Wärmebudget (näher an 300 °C als 400 °C) umsteigen, um Geräte in Back-End-Verbindungsschichten zu integrieren.

„Die Branche muss unbedingt damit beginnen, Geräte in mehr Schichten zu bauen“, sagte Clark von TEL. „Das bedeutet, dass wir Speicher- und Logikgeräte benötigen, die im Rahmen des BEOL-Wärmebudgets gebaut werden.“

Bisher erscheinen Geräte, die aus halbleitenden Oxiden hergestellt werden, vielversprechend, sowohl für die Integration von Speichergeräten in einen logischen BEOL-Fluss als auch für den Aufbau von CMOS-Arrays auf dem Speicherarray in DRAMs.

Eine weitere wesentliche Veränderung betrifft die Integration von 2D-Materialien, die Forschungsinstitute und führende Chiphersteller bereits zu testen beginnen. Es werden Ätzverfahren für Materialien wie Wolframdisulfid oder Molybdändisulfid in Betracht gezogen. Die Folien bestehen aus einer einzigen Materialschicht, daher ist die Entwicklung von Herstellungsprozessen für deren Integration äußerst anspruchsvoll.

Nachhaltigkeit

Chiphersteller und Materiallieferanten verfolgen alternative Chemikalien, um den Kohlenstoffausstoß zu reduzieren. Beim Ätzen sind die Hauptverursacher fluorierte Gase mit hohem Treibhauspotenzial.

„Ein Grund, warum PFOS (Perfluoroctansulfonsäure) problematisch ist, liegt darin, dass das Molekül so stabil ist“, sagte Bézard von imec. „Licht oder chemische Reaktionen in der Atmosphäre reichen nicht aus, um es abzubauen.“

Er sagte, dass eine Reihe alternativer Gasmischungen mit höherem Sauerstoffgehalt leichter dissoziieren und ein geringeres GWP aufweisen. „Allerdings muss jeder Kandidat genauso gute oder sogar bessere Leistungen erbringen, um starten zu können.“

Aber Nachhaltigkeit ist keine besondere Herausforderung beim Ätzen oder Abscheiden. Es handelt sich um eine ganzheitliche Branchenherausforderung von der Lithografie bis zur Verpackung, bei der die Auswirkungen eines neuen Materials die gesamte Geräteverarbeitung beeinflussen.

Referenz

1. K. Derbyshire, „Was ist anders an Transistoren der nächsten Generation?“, Halbleitertechnik, 20. Oktober 2022.

Ähnliche Beiträge

Hochselektives Ätzen für Chips der nächsten Generation wird eingeführt

Die Herstellung von 3D-Strukturen erfordert eine atomare Kontrolle darüber, was entfernt wird und was auf einem Wafer verbleibt.

- SEO-gestützte Content- und PR-Distribution. Holen Sie sich noch heute Verstärkung.

- PlatoAiStream. Web3-Datenintelligenz. Wissen verstärkt. Hier zugreifen.

- Die Zukunft prägen mit Adryenn Ashley. Hier zugreifen.

- Kaufen und verkaufen Sie Anteile an PRE-IPO-Unternehmen mit PREIPO®. Hier zugreifen.

- Quelle: https://semiengineering.com/etch-processes-push-toward-higher-selectivity-cost-control/

- :hast

- :Ist

- :nicht

- :Wo

- $UP

- 000

- 1

- 10

- 13

- 20

- 2022

- 2D

- 2D-Materialien

- 30

- 3d

- 50

- a

- Fähigkeit

- Fähig

- Über uns

- beschleunigen

- beschleunigt

- Zugang

- unterbringen

- erreichen

- Nach

- genau

- genau

- über

- präsentieren

- Adresse

- Adoption

- advanced

- vorteilhaft

- beeinflussen

- aufs Neue

- Ziel

- alex

- Alle

- Zulassen

- bereits

- ebenfalls

- Alternative

- Betrag

- an

- Analyse

- und

- Ein anderer

- beantworten

- jedem

- erscheinen

- Anwendung

- anwendungsspezifisch

- angewandt

- SIND

- Armee

- Feld

- AS

- Aussehen

- helfen

- At

- Atmosphäre

- Attribute

- ein Weg

- Back-End

- Balance

- basierend

- Grundsätzlich gilt

- BE

- Strahl

- weil

- Werden

- war

- Bevor

- Anfang

- Sein

- unten

- Christoph

- BESTE

- Besser

- zwischen

- vorspannen

- Big

- Milliarden

- Bit

- beide

- Boden

- Grenzen

- Gehirn

- Break

- Norbert

- Brute-Force-

- Haushalt

- Budgets

- Building

- erbaut

- aber

- by

- namens

- CAN

- Kandidat

- Kohlenstoff

- Kohlenstoff-Emissionen

- österreichische Unternehmen

- Häuser

- Fälle

- CD

- Die Zellen

- challenges

- herausfordernd

- Labor-Klimakammer

- Übernehmen

- Änderungen

- Kanal

- Kanäle

- berechnen

- berechnet

- Gebühren

- aufladen

- chemisch

- Chemikalien

- Chemie

- Pommes frites

- Reinigung

- Menu

- eng

- näher

- Kombinationen

- Unternehmen

- Unternehmen

- kompatibel

- abschließen

- Abgeschlossene Verkäufe

- Komplex

- Komplexität

- Computer

- konzept

- Bedingungen

- Leitfähigkeit

- Dirigent

- betrachtet

- konstante

- Kontakte

- Inhalt

- fortsetzen

- weiter

- weiter

- Smartgeräte App

- Kupfer

- Unternehmen

- Korrosion

- Kosten

- Kostenreduzierung

- Kosten

- könnte

- Kurs

- erstellen

- schafft

- Erstellen

- kritischem

- Strom

- Zur Zeit

- Kunden

- Schneiden

- technische Daten

- Datenanalyse

- Datenwissenschaft

- Tage

- tief

- Übergeben

- Dichte

- hängt

- beschrieben

- Design

- entwickelt

- Entwicklung

- Entwicklung

- Gerät

- Geräte

- anders

- schwer

- Größe

- Richtung

- Direkt

- Direktor

- diskutiert

- Diversifizierung

- do

- die

- Dollar

- nach unten

- dramatisch

- Antrieb

- trocknen

- im

- jeder

- Früh

- leicht

- bewirken

- Effekten

- Effizienz

- entweder

- Die elektrische

- Elektronen

- Emissionen

- ermöglichen

- Ingenieur

- Entwicklung

- Ingenieure

- genug

- gleichermaßen

- Ausrüstung

- ausgestattet

- Äquivalent

- insbesondere

- essential

- im Wesentlichen

- etc

- Sogar

- schließlich

- Jedes

- anspruchsvoll

- Überprüft

- ausführen

- vorhandenen

- erwartet

- teuer

- Experimente

- Expertise

- ausgesetzt

- Verlängerung

- äußerst

- zugewandt

- weit

- FAST

- beschleunigt

- Eigenschaften

- wenige

- Feld

- Abbildung

- Filme

- Filme

- Vorname

- Blinken (Flash)

- Fluss

- Fließt

- Setzen Sie mit Achtsamkeit

- gefolgt

- Folgende

- Aussichten für

- Zwingen

- unten stehende Formular

- Ausbildung

- vorwärts

- vier

- Frei

- für

- voll

- weiter

- Zukunft

- Lücke

- GAS

- Allgemeines

- erzeugen

- bekommen

- gegeben

- Global

- die globale Erwärmung

- Kundenziele

- gut

- groß

- Gruppe an

- Wachsen Sie über sich hinaus

- Wächst

- Hälfte

- Griff

- hart

- Hardware

- Haben

- he

- hilfreich

- hier

- High

- Hohe Ausbeute

- höher

- hoch

- Loch

- Bohrungen

- ganzheitliche

- Horizontale

- Houses

- Ultraschall

- aber

- HTTPS

- human

- Humans

- hunderte

- Hybrid

- i

- Impact der HXNUMXO Observatorien

- unmöglich

- zu unterstützen,

- verbessert

- Verbesserung

- in

- das

- Einschließlich

- Eingehende

- integrieren

- zunehmend

- Energiegewinnung

- Eingänge

- Instanz

- beantragen müssen

- integrieren

- Integration

- Integration

- Interaktion

- Interaktionen

- verbindet

- in

- Einführung

- Probleme

- IT

- SEINE

- jpg

- nur

- Wesentliche

- Lam

- grosse

- größer

- Schicht

- Lagen

- Layout

- führenden

- lernen

- am wenigsten

- Niveau

- Cholesterinspiegel

- Lebensdauer

- Gefällt mir

- wahrscheinlich

- Line

- Linien

- LITHO

- wenig

- Logik

- länger

- aussehen

- Verlust

- Los

- Sneaker

- Maschine

- Maschinelles Lernen

- gemacht

- Main

- halten

- um

- Makers

- Making

- Manager

- hergestellt

- Hersteller

- Herstellung

- viele

- Markt

- Marketing

- Marketing Director

- Maske"

- Ihres Materials

- Materialien

- max-width

- Kann..

- bedeuten

- Mittel

- Mitglied

- Memory

- Metall

- Metallindustrie

- Metrik

- könnte

- Million

- Millionen

- Minimum

- Kommt demnächst...

- Modell

- Modellieren

- für

- Modi

- MOL

- Molekül

- Monat

- mehr

- vor allem warme

- schlauer bewegen

- ziehen um

- viel

- mehrere

- fast

- Need

- erforderlich

- Bedürfnisse

- Negativ

- Neutral

- Neu

- weiter

- nicht

- Edel

- Knoten

- Fiber Node

- jetzt an

- Anzahl

- Oktober

- of

- vorgenommen,

- on

- einmal

- EINEM

- einzige

- die

- Einkauf & Prozesse

- Optimierung

- Optimieren

- optimiert

- or

- Auftrag

- Andere

- Anders

- UNSERE

- übrig

- Sauerstoff

- Verpackung

- Parameter

- besondere

- besonders

- Schnittmuster

- Personen

- ausführen

- Leistung

- Durchführung

- vielleicht

- Perspektive

- Phase

- Phänomen

- Philippe

- physikalisch

- Physisch

- Physik

- Säule

- Tonhöhe (Pitch)

- zentrale

- Plasma

- Plato

- Datenintelligenz von Plato

- PlatoData

- spielt

- PoC

- positiv

- Möglichkeiten

- möglich

- gegebenenfalls

- Potenzial

- möglicherweise

- Werkzeuge

- größte treibende

- präzise

- Präzision

- vorhersagen

- Präsident

- Druck

- Aufgabenstellung:

- Probleme

- Prozessdefinierung

- anpassen

- Verarbeitung

- produziert

- Produkt

- Produktentwicklung

- Produktion

- PRODUKTIVITÄT

- Produkte

- Profil

- Profil

- Rentabilität

- Programm

- Programmierung

- aussichtsreich

- Beweis

- Proof of Concept

- Publikationen

- Push

- Frage

- schnell

- F&E

- Rampe

- Angebot

- Bewerten

- Honorar

- Verhältnis

- erreichen

- Reagieren

- Reaktion

- Reaktionen

- echt

- wahres Leben

- Grund

- kürzlich

- Software Empfehlungen

- empfohlen

- Veteran

- Reduzierung

- Reduktion

- reflektieren

- regulär

- Release

- zuverlässig

- verlassen

- Entfernung

- entfernen

- Entfernt

- Entfernen

- wiederholbar

- wiederholt

- ersetzen

- berichten

- erfordern

- falls angefordert

- Voraussetzungen:

- erfordert

- Forschungsprojekte

- Folge

- Die Ergebnisse

- Enthüllt

- Recht

- ROBERT

- Rollen

- Rollen

- rund

- Ohne eine erfahrene Medienplanung zur Festlegung von Regeln und Strategien beschleunigt der programmatische Medieneinkauf einfach die Rate der verschwenderischen Ausgaben.

- Führen Sie

- Said

- gleich

- sagen

- Skalieren

- Skalierung

- Regelungen

- Wissenschaft

- Sucht

- gesehen

- selektiv

- Halbleiter

- Senior

- Sinn

- Einstellung

- mehrere

- verschieben

- sollte

- Silizium

- Einfacher

- vereinfachen

- einfach

- Simulation

- Single

- erfahren

- klein

- So

- Software

- Lösungen

- LÖSEN

- einige

- irgendwo

- Quelle

- Raumfahrt

- spezifisch

- Spezifikationen

- Spezifikation

- Geschwindigkeit

- Stabilität

- stabil

- gestapelt

- Stacks

- Unser Team

- Stufen

- Anfang

- begonnen

- Schritt

- Shritte

- Immer noch

- Der Stress

- Struktur

- Anschließend

- wesentlich

- so

- plötzlich

- ausreichend

- Schlägt vor

- Lieferanten

- Oberfläche

- Überraschung

- Nachhaltigkeit

- nachhaltiger

- Sweep

- Schweiz

- Systeme und Techniken

- Nehmen

- Einnahme

- Reden

- gezielt

- Team

- Technische

- Technologies

- Technologie

- Technische Entwicklung

- Begriff

- Test

- Testen

- Tests

- als

- zur Verbesserung der Gesundheitsgerechtigkeit

- Das

- Die Zukunft

- ihr

- Sie

- dann

- Dort.

- Thermal-

- Diese

- vom Nutzer definierten

- Dritte

- fehlen uns die Worte.

- gründlich

- Tausende

- nach drei

- Durch

- Tier

- Fester

- Zeit

- zeitliche Koordinierung

- zu

- gemeinsam

- Tonne

- TONE

- auch

- Top

- aufnehmen

- gegenüber

- übertragen

- Transformieren

- Übergang

- Trend

- versuchen

- XNUMX

- typisch

- typisch

- zugrunde liegen,

- unberechenbar

- auf

- nach oben

- us

- -

- benutzt

- Mitglied

- Verwendung von

- Nutzen

- verified

- vertikal

- vertikal

- sehr

- lebensfähig

- Vizepräsident:in

- vincent

- Assistent

- flüchtig

- wollen

- will

- wurde

- Weg..

- we

- Wochen

- GUT

- Was

- wann

- ob

- welche

- während

- ganze

- warum

- werden wir

- mit

- .

- ohne

- Word

- Arbeiten

- arbeiten,

- Werk

- würde

- Jahr

- Jahr

- Ausbeute

- nachgiebig

- Erträge

- U

- Zephyrnet

- Null