Neue Bump-Strukturen werden entwickelt, um höhere Verbindungsdichten in Flip-Chip-Gehäusen zu ermöglichen, aber sie sind komplex, teuer und immer schwieriger herzustellen.

Für Produkte mit hoher Pinzahl: Flip Chip [1] Pakete sind seit langem eine beliebte Wahl, da sie die gesamte Chipfläche für die Verbindung nutzen. Die Technologie ist seit den 1970er Jahren im Einsatz, beginnend mit IBMs C4 (Controlled Collapse Chip Connection), doch erst in den 1990er Jahren kam sie wirklich weit verbreitet zum Einsatz.

Seitdem hat sich die Bump-Technologie weiterentwickelt, um die zunehmende Leistungs- und Signalverbindungsdichte zu bewältigen, die für Speicher, Hochleistungsrechner und mobile Computergeräte erforderlich ist. Um diesen Bedarf zu decken, ist eine neue Verbindungstechnologie erforderlich, die kleinere Bump-Abstände ermöglicht und derzeit in Produktion ist.

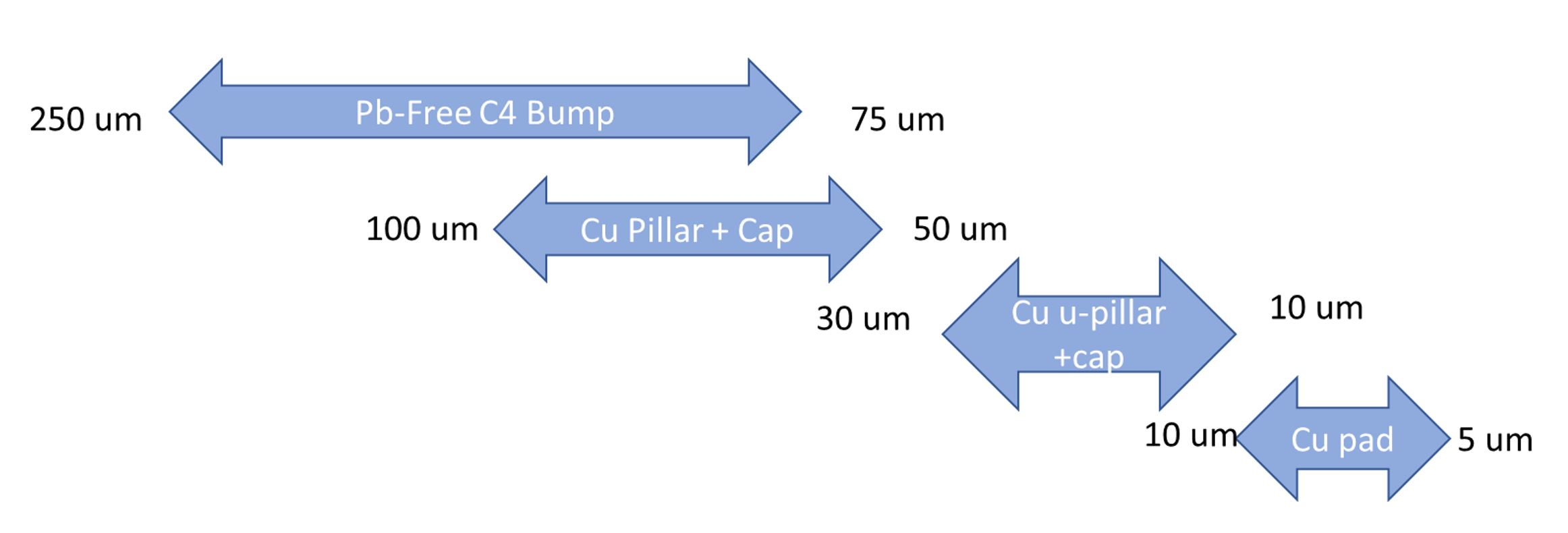

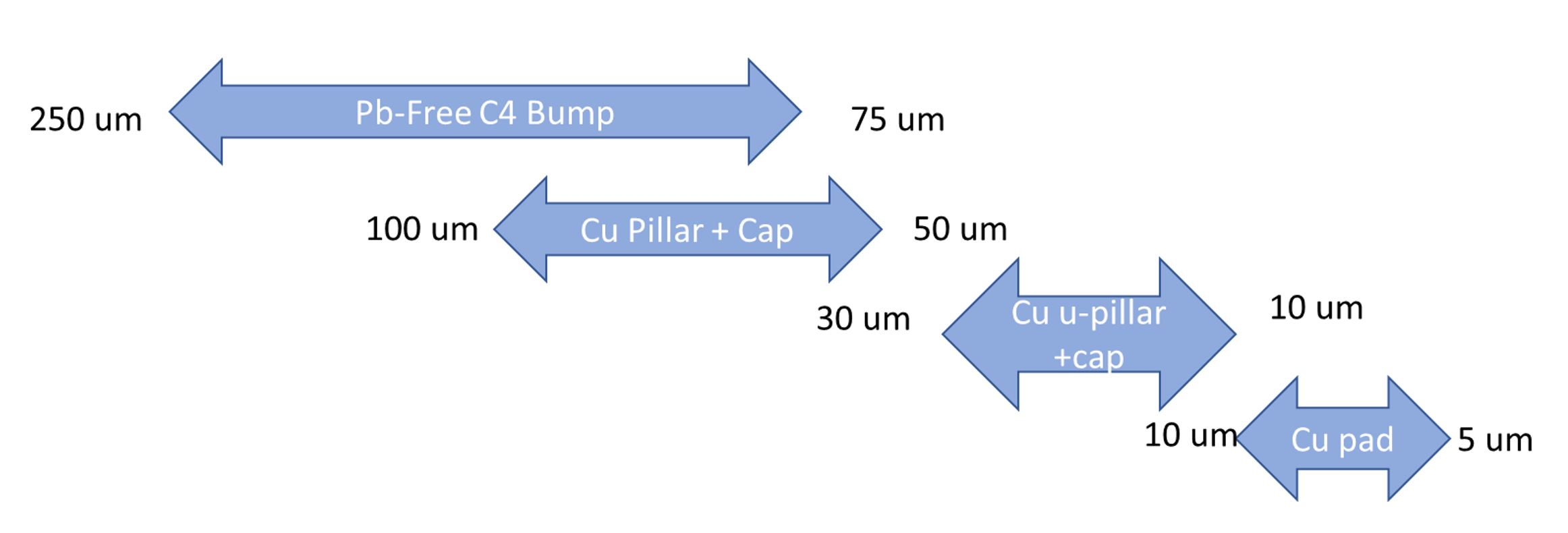

Im Laufe der Zeit entwickelt sich die Roadmap für Flip-Chip-Verbindungen von bleifreien Bumps über Kupfersäulen bis hin zu Kupfer-Mikrobumps. Die Pitchgrößen schrumpfen immer weiter, was wiederum zu Herstellungsherausforderungen beim Bumping und Bonden führt.

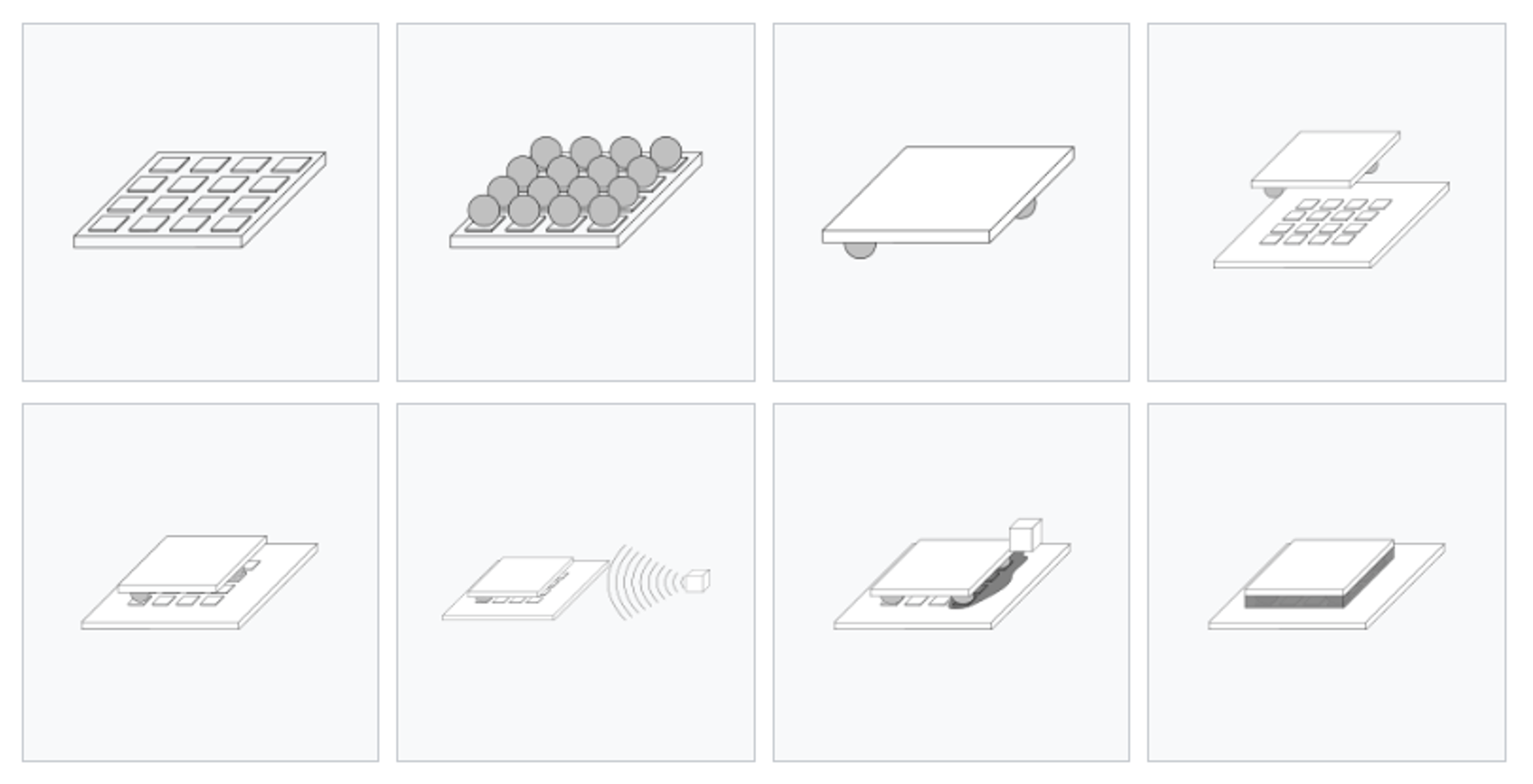

Abb. 1: Tonhöhenbereiche der Flip-Chip-Technologie. Quelle: A. Meixner/Semiconductor Engineering

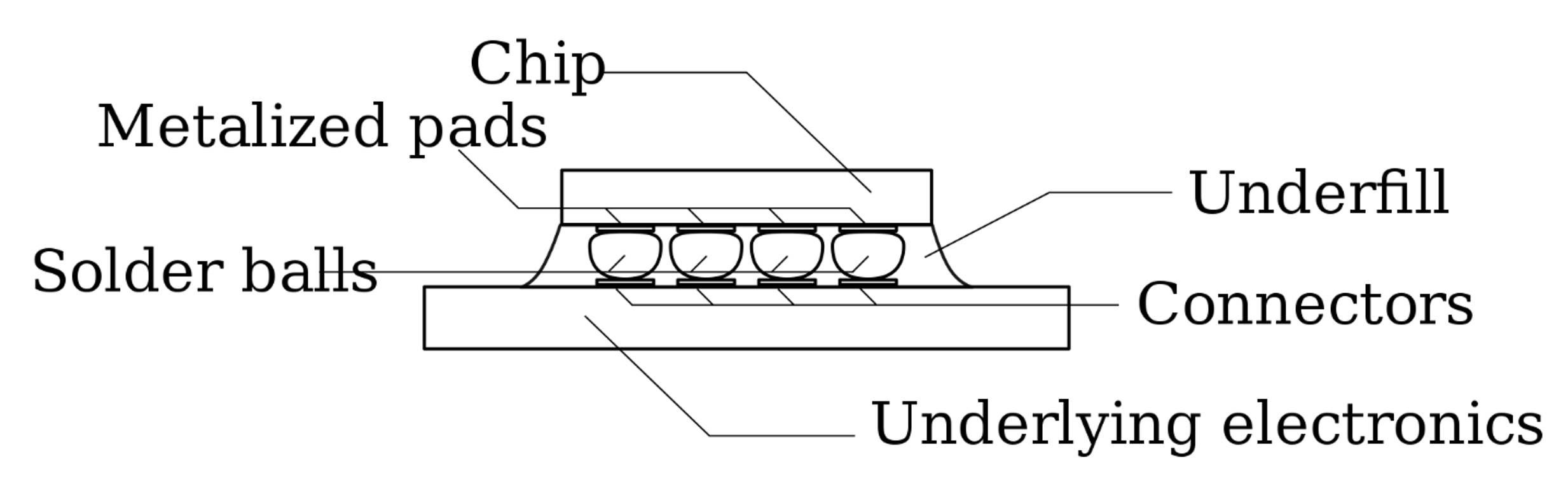

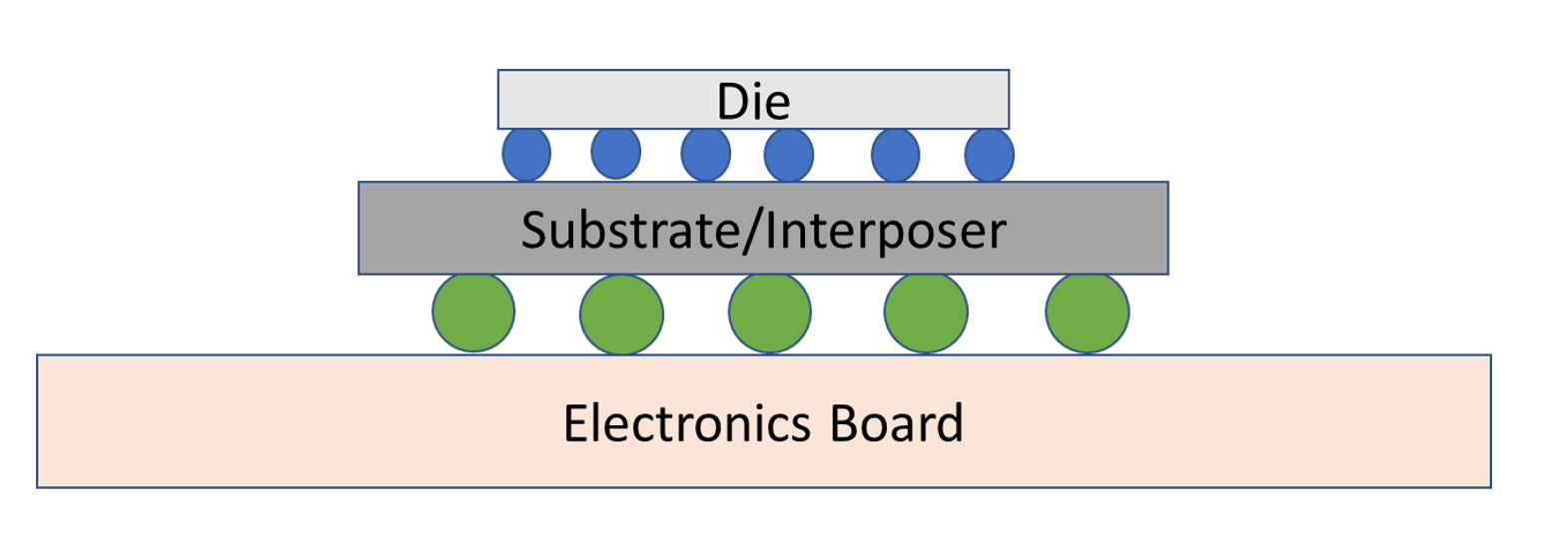

Abb. 2: Flip-Chip-Komponenten. Quelle: Wikipedia

„Im Flip-Chip-Bereich – mit einem Rastermaß von 250 Mikron und darunter – waren es ursprünglich Zinn-Blei-Bumps, und einer der großen Schritte war die bleifreie Lösung. Aber wenn man anfängt, 100 Mikrometer oder weniger zu erreichen, sieht man eher eine Kupfersäule, obwohl es eine Überschneidung gibt, da wir Kupfersäulen bis zu 250 Mikrometer sehen“, sagte Jeff Schaefer, leitender Prozessingenieur bei Promex-Industrien. „Mit dem 250-Mikrometer-Abstand sehen wir Bump-Größen oder Kupfersäulendurchmesser von 130 Mikrometern. Sobald wir den Abstand von 100 Mikrometern erreicht haben, beträgt der Durchmesser 80 Mikrometer. Der kleinste, den ich je gesehen habe, hat einen Abstand von 62.5 Mikrometern und eine Säule von 40 Mikrometern. Ich gehe davon aus, dass wir bald einen 50-Mikrometer-Pitch sehen werden.“

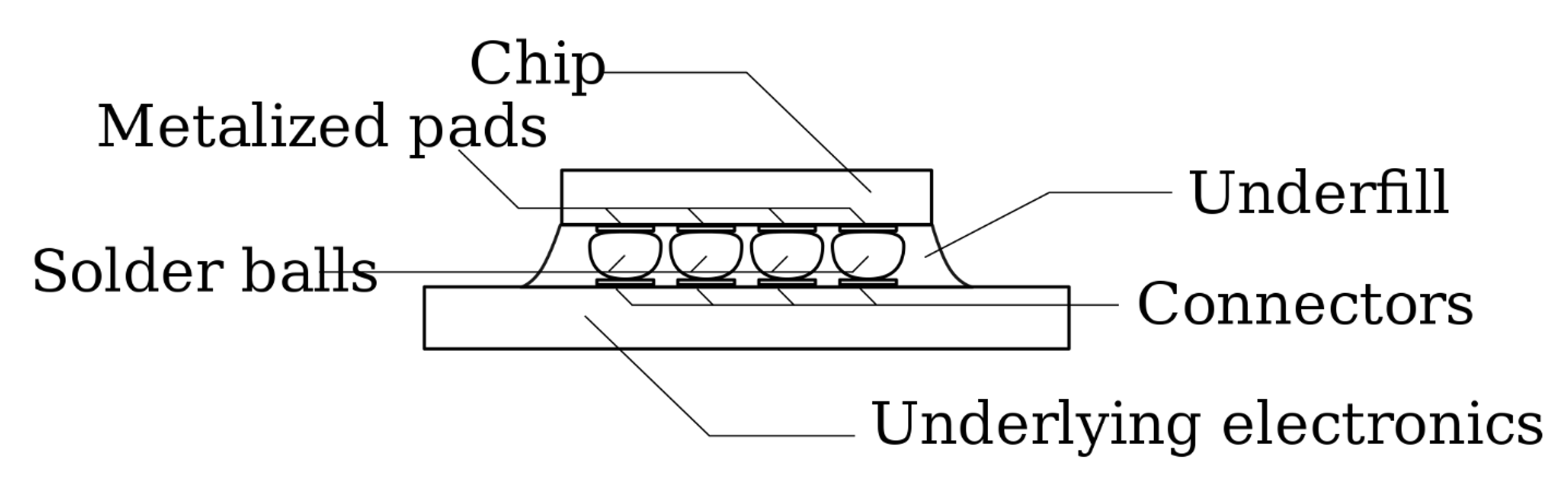

Der grundlegende Flip-Chip-Prozess beginnt nach der Schaltungsherstellung, wenn auf der Chipoberfläche Metallpads für die Verbindung mit den I/Os erzeugt werden. Als nächstes folgt das Wafer-Bumping, bei dem auf jedem Pad eine Lotkugel abgeschieden wird. Der Wafer wird dann in Würfel geschnitten, und diese Chips werden umgedreht und so positioniert, dass die Lotkugeln mit den Substratpads ausgerichtet sind. Die Lotkugeln werden dann geschmolzen/aufgeschmolzen, üblicherweise mit Heißluft, und ein montierter Chip wird mit einem elektrisch isolierenden Klebstoff unterfüllt, üblicherweise unter Verwendung von Kapillarwirkung. [1]

Abb. 3: Flip-Chip-Herstellungsprozess. Quelle: Wikipedia

Der Übergang zu einer Kupfersäule oder einem Mikrobump erfordert die Lithographie, um diese Strukturen zu erzeugen.

„Kupfersäulen werden im Allgemeinen mit einem Rastermaß von weniger als 130 µm verwendet, da es sich bei den Kupfersäulen nicht um kreisförmige Löthöcker handelt, sondern meist um Cu-Stützen mit Lot oben drauf“, sagte Doug Scott, Senior Vice President für Wafer-Level-Packaging bei Amkor-Technologie. „Dadurch können die Kupfer-Pillar-Bumps näher beieinander platziert werden, ohne dass die Gefahr besteht, dass sich das Lot beim Reflow-Löten der Baugruppe miteinander verbindet – im Allgemeinen ~40 µm Cu + ~25 µm.“

Es gibt auch Variationen des Themas. „Microbump, ein gebräuchlicher Begriff für Verbindungen zwischen Silizium und Silizium, unterscheidet sich geringfügig, da der CTE (Wärmeausdehnungskoeffizient) im Allgemeinen derselbe ist“, sagte Mark Gerber, Senior Director für Technik/technisches Marketing bei ASE-Gruppe. „Einige der allgemeinen Designregeln für Kupfersäulen sind dieselben, aber die flache Oberflächentopographie und die spannungsarmen Verbindungen ermöglichen eine Flexibilität der verwendeten Unterfüllung. Dadurch kann auch der individuelle Bump-Pitch gesteuert werden. Heutzutage ist aufgrund der zuvor erwähnten Routing-Überlegungen für das verwendete Wafer-Level- oder Fab-Level-Routing ein 35-µm-Bump-Full-Array-Pitch möglich.“

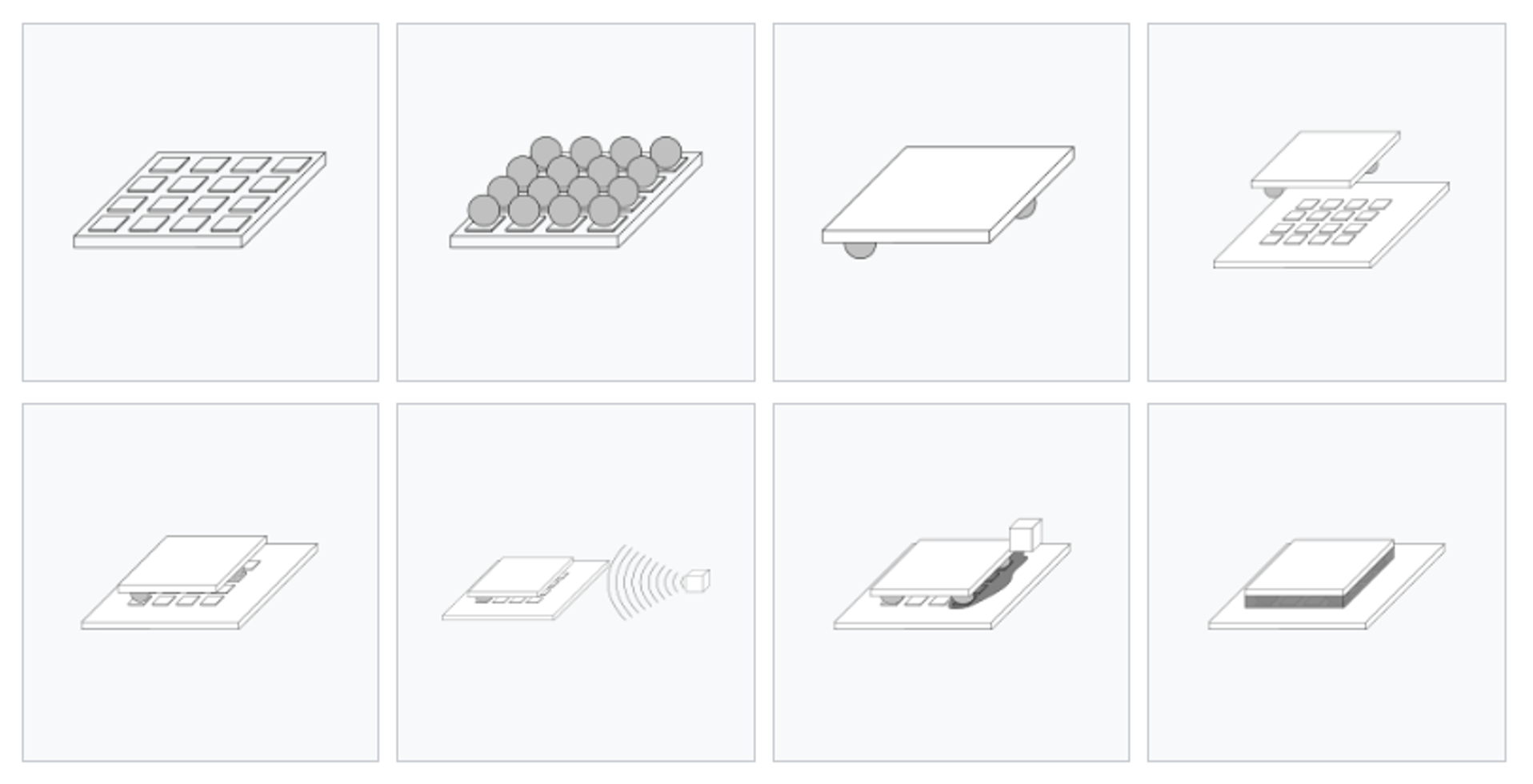

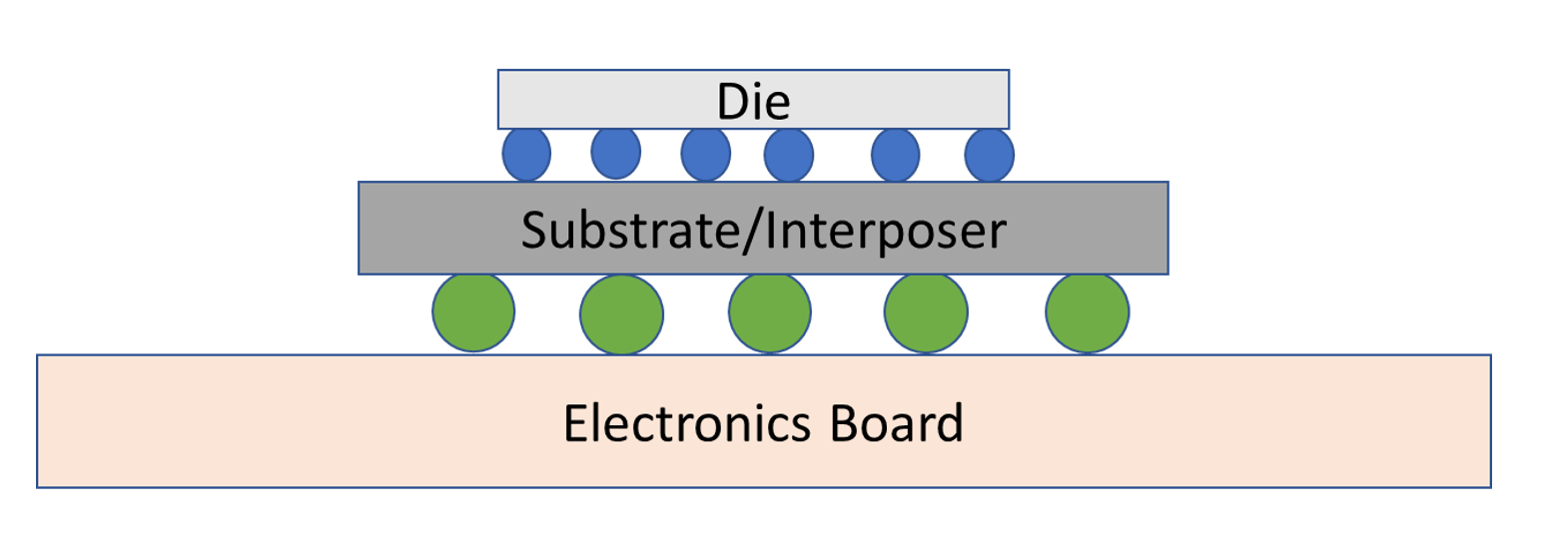

Die Heterogeneous Integration Roadmap [2] beschreibt alle Aspekte des Packaging, einschließlich Die-Substrat-Verbindungen, von Drahtbonds bis hin zu Durchkontaktierungen durch Silizium. Bei Flip-Chip-Gehäusen spielen Die-zu-Substrat-Verbindungen, Substrat-Umverteilungsbereiche und Substrat-zu-Platine-Verbindungen alle eine Rolle bei den Herstellungsgrenzen.

Abb. 4: Konzeptdiagramm der Flip-Chip-Verpackung. Quelle: A. Meixner/Semiconductor Engineering

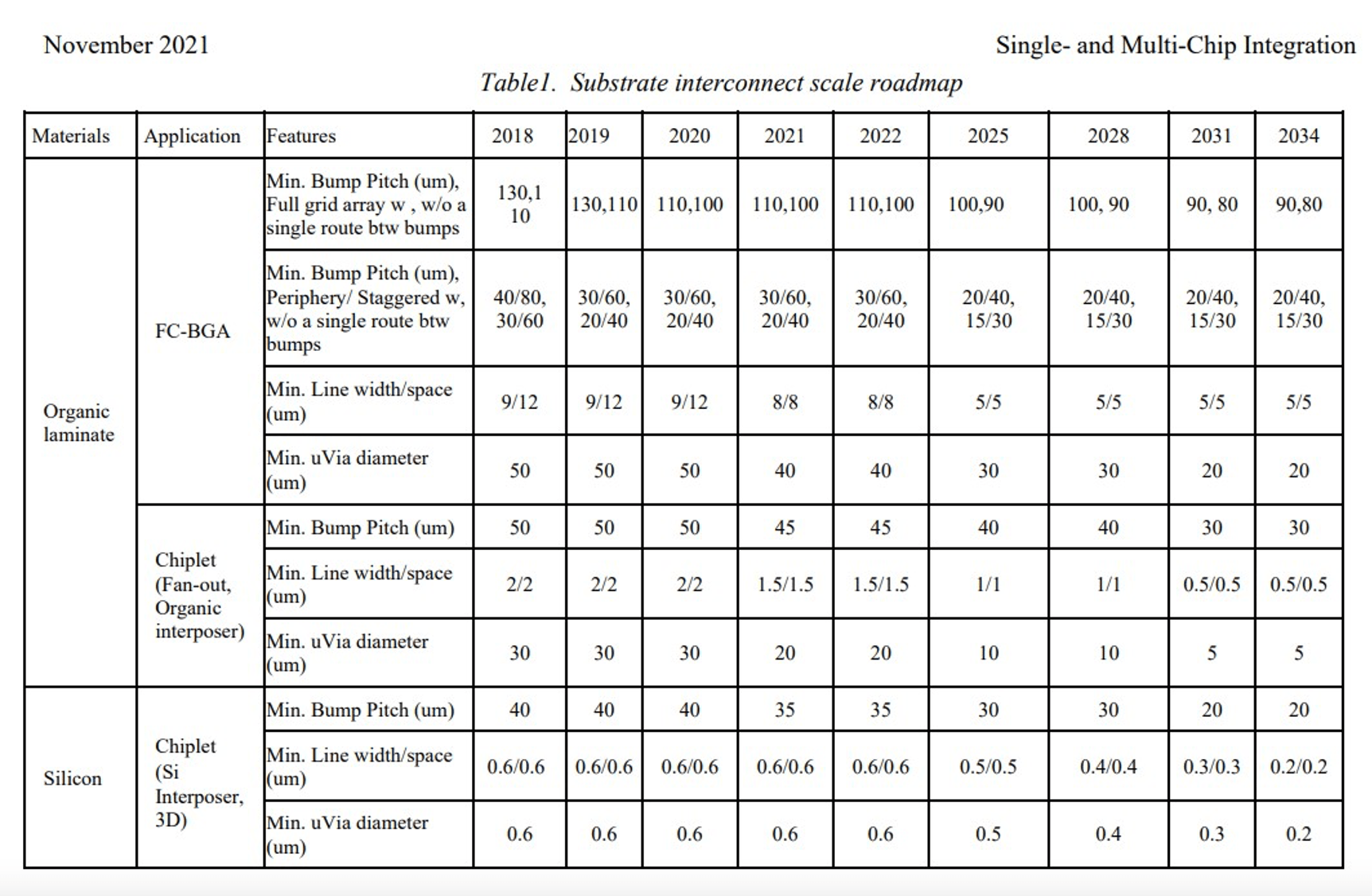

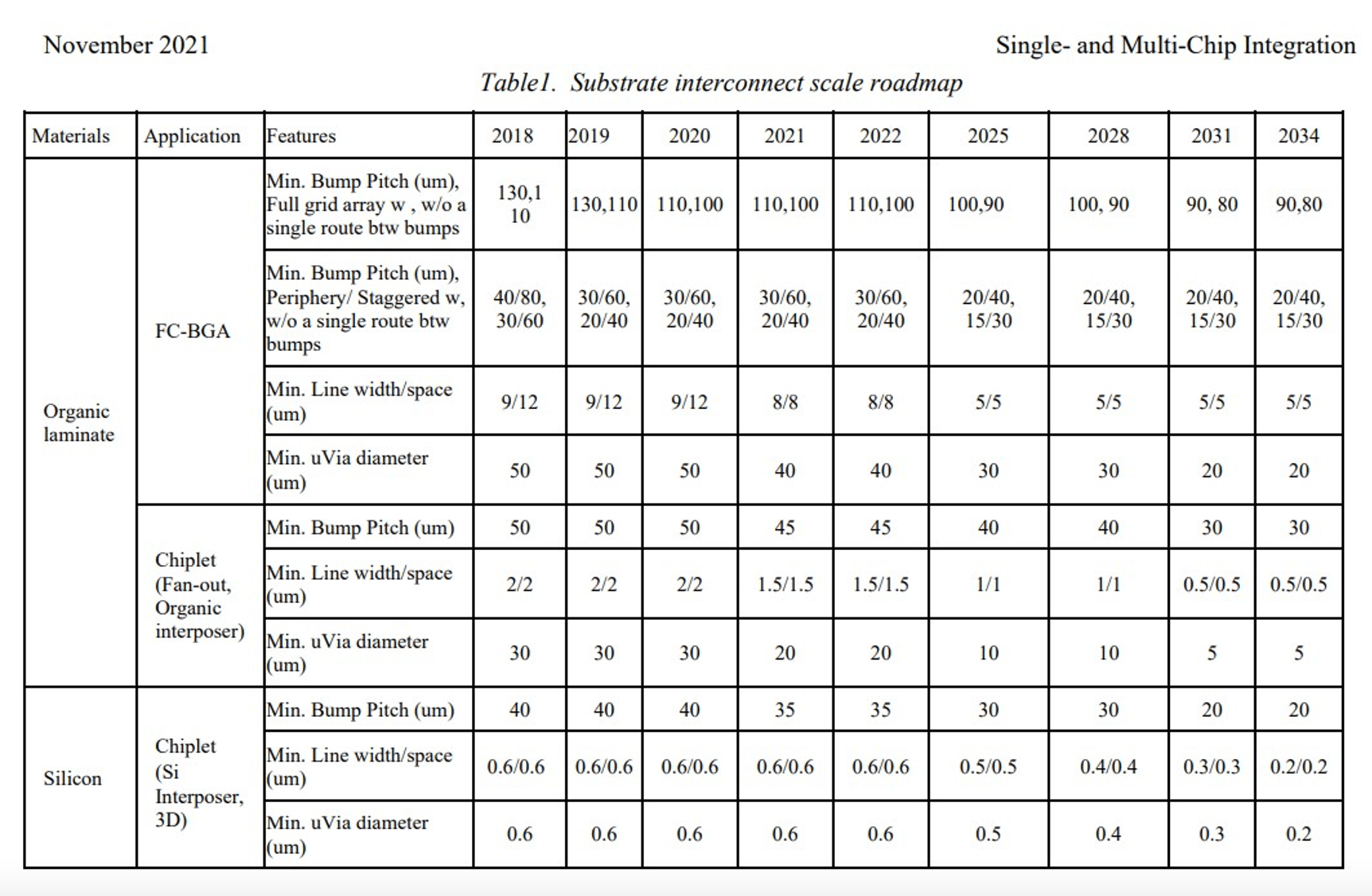

Kapitel 8 der Heterogeneous Integration Roadmap [3] dokumentiert die Landschaft der aktuellen und geplanten Verpackungstechnologie-Pitches. Der Mindestabstand jeder Flip-Chip-Verbindungstechnologie ist in Tabelle 1 von Unterabschnitt 8.7 (Seite 41) erfasst.

![Kapitel 8 der Heterogeneous Integration Roadmap [3] dokumentiert die Landschaft der aktuellen und geplanten Verpackungstechnologie-Pitches. Der Mindestabstand jeder Flip-Chip-Verbindungstechnologie ist in Tabelle 1 von Unterabschnitt 8.7 (Seite 41) erfasst.](https://platoaistream.com/wp-content/uploads/2023/05/challenges-grow-for-creating-smaller-bumps-for-flip-chips-7.png)

![Kapitel 8 der Heterogeneous Integration Roadmap [3] dokumentiert die Landschaft der aktuellen und geplanten Verpackungstechnologie-Pitches. Der Mindestabstand jeder Flip-Chip-Verbindungstechnologie ist in Tabelle 1 von Unterabschnitt 8.7 (Seite 41) erfasst.](https://platoaistream.com/wp-content/uploads/2023/05/challenges-grow-for-creating-smaller-bumps-for-flip-chips-8.png)

Die entsprechende Tabelle für die Substratverbindung (der Teil, der das Gehäuse mit der Platine verbindet) finden Sie in Unterabschnitt 8.8 (Seite 43).

Mit jeder Änderung in der Verbindungstechnologie gehen neue Prozesse und deren Grenzen einher, die Innovation, Ertragsmanagement und Fehlerprüfung vorantreiben.

Technologiegrenzen überschreiten

Die Bumping-Technologie wird anhand von Abstand, Größe, Höhe sowie elektrischen und mechanischen Eigenschaften gemessen. Die thermischen Überlegungen variieren je nach der CTE-Diskrepanz des Materials. Bei größeren Chips und Wafern ist Verzug ein Problem, das durch das Rückschleifen eines Wafers vor dem Anbringen des Chips noch verstärkt wird.

„Es gibt eine Reihe von Treibern für Pitch-Beschränkungen für jeden Verbindungstyp“, sagte Gerber von ASE. „Ausgehend von herkömmlichen Löthöcker-Flip-Chip-Verbindungen wird die Pitch-Fähigkeit durch die Kollapshöhe für die Unterfüllung, den Capture-Pad-Pitch für die Leiterbahnführung, den Capture-Pad-Pitch für das Risiko von Bump-to-Bump-Kurzschlüssen und mehrere andere Pitch-bezogene Empfindlichkeiten bestimmt. Die vormontierte Bump-Höhe hat eine definierte Höhe, aber wie IBM den C4-Begriff – Controlled Collapse Chip Connection – definiert hat, bestimmen der Durchmesser des Löthöckers und die Größe des Capture-Pads die „Zusammenbruch- oder Endhöhe“ der Verbindung. Dies ist der wichtigste Pitch-begrenzende Faktor für die Verwendung von Lothöckern im Zusammenhang mit dem Pitch.“

Die Höhe der Erhebung wird durch das Design, aber auch durch die Verarbeitung bestimmt.

„Bei standardmäßig plattierten Löthöckern und Kupfer-Pillar-Bumps liegen die Bump-Höhen vor der Montage im Allgemeinen bei etwa 70 µm bis 75 µm, mit kollabierten Bump-Höhen nach der Montage bei etwa 50 µm, um X-, Y- und Z-Raum für den Unterfüllungsfluss zwischen den Bumps zu schaffen. Mikrobumps haben viel geringere Bump-Höhen und erfordern die Plattierung von viel weniger Lot. Insbesondere können Mikrohöcker weniger als 10 µm hoch sein, wobei die Cu- und Lothöhe je nach Rastermaß und Endbedarf reduziert wird“, sagte Scott von Amkor. „Standardisierte plattierte Löthöcker werden im Allgemeinen in Abständen von 130 µm bis 250 µm verwendet. Unterhalb von 130 µm gibt es nicht genügend xy-Abstand zwischen den Bumps, wenn man mit einer Bump-Höhe von 70 µm vor der Montage beginnt.“

Die Herstellung von Kupfersäulen erfordert mehr Verarbeitungsschritte als Löthöcker.

„Als wir zur Die-to-Die-Welt übergingen, war die Technologie anders, denn jetzt hat man es mit einem Wafer zu tun und die Planerite sind im Vergleich zu Die-to-Substrat so gut. Zuerst erstellen Sie die Kupfersäule. Auf dem ersten Wafer, der das Lot oder die Kupfersäule erhalten soll, befindet sich zunächst ein Under-Bump-Metall (UBM). Es handelt sich um eine kleine Kappe über der Öffnung, die in das Silikon hineinragt. Dann bauen wir daraus einen Kupferkern und setzen darauf eine Zinnkappe. Dann sieht der Empfangswafer so aus, als hätte er dort ein UBM-Pad, und er ist normalerweise mit einer Nickel-Gold-Beschichtung versehen, so dass er schön und makellos aussieht“, erklärte Schaefer von Promex Industries. Anstelle einer leichten Vertiefung wie bei einem Laminatsubstrat haben Sie also eine leichte Extrusion. Wir haben herausgefunden, dass wir sie tatsächlich nass löten können, ohne dass sich Lötmittel auf dem Pad befindet. So sind sie entworfen und gebaut. Es wirkt fast wie ein Lötzinn und ein Pad, weil es eine kleine Kuppel darstellt und nicht versucht, in ein Loch hineinzudringen.“

Die für die Bildung von Cu-Säulen erforderlichen Fotolithografieschritte unterliegen ebenso wie den Substratdesignregeln Grenzen.

„Für Kupfersäulen, die aus einem Kupferstift und einer Lötkappe an der Spitze bestehen, kann die Höhe des Kupferstifts bis zur Begrenzung einer oder mehrerer Fotolackschichtdicken definiert werden, und wenn Sie den Abstand verringern, ändert sich das Seitenverhältnis des „Das Verhältnis von Pfostenhöhe zu Abstand wird zusammen mit dem Fotolackmaterial und den Möglichkeiten des Bildgebungswerkzeugs zur Einschränkung“, sagte Gerber. „Eine sekundäre Einschränkung für die Kupfersäulenverbindung sind die verwendeten Substratdesignregeln. Für einen feinen Rasterabstand von >110 µm werden zwei Hauptmethoden verwendet: BOT (Bond on Trace) oder ET – Embedded Trace, bei dem die Lötkappe der Kupfersäule anstelle eines herkömmlichen Capture-Pads auf der Leiterbahn platziert wird. Die Größe und Form von Kupfersäulen, einschließlich der oben genannten Einschränkungen, kann die Möglichkeiten und den Fahrplan für eine weitere Verkleinerung der Abstände einschränken. Viele dieser Einschränkungen sind auf die Möglichkeit zurückzuführen, Leiterbahnen zwischen den Säulen auf der Substratseite zu verlegen. Da neue Technologien verfügbar sind, wie z. B. RDL auf Waferebene, werden die Verbindungs-Roadmaps weiter vorangetrieben, jedoch immer noch mit Einschränkungen hinsichtlich des Höhen-/Seitenverhältnisses für Herstellungsprozesse wie Underfill.“

Andere sind sich einig, dass der Underfill-Prozess mit Herausforderungen verbunden ist. „Je kleiner die Unebenheiten werden, desto kleiner werden sie. Mittlerweile wird es immer schwieriger, Unterfüllungen zu finden, unter denen man hindurchkommt. Die Unterfüllungen wurden in der Vergangenheit so konzipiert, dass sie einen Spalt von weniger als 5 Mil erreichen, und jetzt sind sie nur noch 3 Mil, also 75 Mikrometer groß“, sagte Schaefer. „Jetzt sehen wir Lücken von 60 und 25 Mikrometern. Ich bin sicher, dass die Leute an neuen Unterfüllungen arbeiten. Aber es gibt eine Menge Dinge, an denen man arbeiten muss. Zum einen wird es mit zunehmender Feinstaubbildung eher zu einem Schlamm, der das Fließen erschwert. Dies ist eine Hürde, die beseitigt werden muss.“

Ertrag verwalten

Da die Bumping-Technologie immer kleiner wird, eröffnen zusätzliche Verarbeitungsschritte – beispielsweise die Lithographie zur Herstellung von Kupfersäulen – neue Möglichkeiten für Yield-Detektoren. Für einen erfolgreichen Bondprozess sind Partikel, Oberflächenverunreinigungen und die Bildung von Löthöckern problematisch für die Ausbeute. Diese erfordern Prozesskontrollen, Messtechnik und Inspektion.

Eine natürliche Kontaminationskontrolle ist erforderlich. „OSATs der Stufe 1 investieren, um den Grad der Kontaminationsquellen in Fabriken zu reduzieren und damit die Fehlerquote zu senken“, sagte Scott von Amkor. „Pitch trägt nicht zur Defektität bei. Unabhängig von der Tonhöhe bestehen ähnliche Fehlergrade.“

Aber Pitch bringt einige eigene Herausforderungen mit sich. „Da der Abstand kleiner wird und die Unebenheitsgröße kleiner wird, ist das Partikelkontaminationsmanagement sehr wichtig. Für andere Arten von Verbindungen wie Hybrid-Bonding, bei denen die Abstände auf unter 30 µm reduziert werden und der Oberfläche-zu-Oberfläche-Kontakt wichtig ist, ist die Wafer-basierte Reinraumumgebung von entscheidender Bedeutung für die Erträge“, sagte Gerber von ASE.

Auch die Vorbereitung auf den Underfill-Prozess sollte nicht unterschätzt werden.

„Im Allgemeinen wird man bei einem Laminat nach dem Flip-Chip eine Unterfüllung vornehmen“, sagte Schaefer von Promex. „Wir bestimmen, wo wir es platzieren und wie wir es umfließen lassen. Wir reinigen es, um jegliches Flussmittel unter dem Spalt zwischen Chip und Substrat zu entfernen. Dann unterfüllen wir es mit einem fließfähigen Epoxidharz. Es ist so konzipiert, dass es einnässt und keine Hohlräume oder Ähnliches hinterlässt. Aber es gibt eine Herausforderung, wenn wir zu feineren Tonhöhen kommen. Die Unebenheiten werden etwas kürzer und je kürzer die Lücke zwischen dem Chip und dem Substrat wird, desto schwieriger ist die Reinigung. Stellen Sie sich vor, Sie kleben zwei Glasobjektträger zusammen, um zu versuchen, den Schmutz zwischen ihnen herauszubekommen.“

Anforderungen an Messtechnik und Inspektion

Für die Verwaltung der Prozesskontrolle und des Ertrags spielen Mess- und Inspektionswerkzeuge eine wichtige Rolle. „Es gibt auf dem Markt Tools, die zusätzlich zur prozessbegleitenden Querschnittsanalyse, die bei der Einrichtung und in definierten Produktionsintervallen verwendet wird, als Orientierungshilfe für die Verbindungsintegrität dienen können“, sagte Gerber von ASE.

Der Bumping-Prozess und die Bonding-Prozesse weisen jeweils spezifische Eigenschaften auf, die überwacht werden müssen. Bei Unebenheiten konzentriert sich die Messtechnik auf Durchmesser, Höhe und Koplanarität. Kleinere Abstände erfordern eine strengere Kontrolle des Noppendurchmessers und der Höhenkontrolle. In ähnlicher Weise wird das Koplanaritätsfenster kleiner, wenn die Höckerhöhe kleiner wird. Normalerweise ist eine Abweichung von 10 % zulässig. Beispielsweise führt eine Höckerhöhe von 30 µm zu einer zulässigen Abweichung von ±3 µm. Eine Überschreitung dieses Wertes führt zu einer erfolglosen oder schlechten Bindung.

„Das Bonden erfolgt normalerweise mit Massen-Reflow-Öfen“, sagte Mike Kelly, Vizepräsident für Advanced Package and Technology Integration bei Amkor. „Die anfängliche Charakterisierung des Reflow-Prozesses erfolgt mithilfe von Shadow-Moiré zur Quantifizierung des Verzugs während des Reflow-Verfahrens und einer Temperaturkartierung der Öfen, um eine konsistente Temperaturkontrolle des Flip-Chip-Bauteils selbst sicherzustellen. Während des Aufbaus wird die Matrize mechanisch angehoben und überprüft, um eine gute Lotbenetzung sicherzustellen. Außerdem wird Flussmittel normalerweise mit einem „Tauchflussmittel“ aufgetragen, bei dem die Chip-Bumps in dünne, streng kontrollierte Flussmittelreservoirs „eingetaucht“ werden. Die Sichtprüfung dieser Artikel erfolgt stichprobenartig.“

Die zunehmende Automatisierung der Sichtprüfung verringert die Abhängigkeit von Bedienern, die ein Bild betrachten und eine Entscheidung treffen müssen. Der exponentielle Anstieg der Bump-Verbindungen ist ein Treiber. Eine weitere Möglichkeit bieten Änderungen an den Klebeprozessen. Ein selbstausrichtender Lot-Reflow-Prozess ist eine ausgereifte Technologie. Mit dem thermischen Kompressionsbonden, das üblicherweise in modernen Verpackungen verwendet wird, gibt es Zuverlässigkeitsmechanismen, die elektrische Tests bestehen. Dies wiederum veranlasst den Einsatz von Röntgeninspektions- und Messinstrumenten, um die Unebenheiten nach dem Kleben zu betrachten.

„Bei Verpackungen mit geringer Komplexität könnten die Einrichtungen auf einen Bediener und eine manuelle Inspektion verzichten. Für ein Teil mit 100 Unebenheiten ist diese Methode machbar. Bei 1,000 Stößen ist es definitiv eine Belastung. Sobald ein Teil 10,000 Unebenheiten hat, gibt es keine Chance mehr. Wir gehen über diesen Punkt hinaus und müssen zur nächsten Methode übergehen“, bemerkte Frank Chen, Leiter für Anwendungen und Produktmanagement bei Bruker. „Qualität und Komplexität gehen Hand in Hand, denn wenn Sie versuchen, etwas komplexer zu machen, wird Ihr Ertrag beeinträchtigt und es werden neue Werkzeuge erforderlich sein. Unter Werkzeugen versteht man sowohl Prozesswerkzeuge als auch Messwerkzeuge, daher müssen beide parallel weiterentwickelt werden. Aus unseren eigenen Studien wissen wir, dass man nach 1,000 Schlägen anfangen muss zu denken: „Meine manuelle Technik reicht nicht aus und ich brauche etwas Neues.““

Zur Unterstützung der Verpackungsherstellung stehen verschiedene Inspektions- und Messwerkzeuge zur Verfügung.

„Es gibt mehrere Methoden, die zur Prozesskontrolle eingesetzt werden können oder sollten. Erstens die traditionelle 2D-Inspektion (AOI) für eine 100-prozentige Inspektion von Oberflächendefekten pro Prozessablauf (d. h. IQC, OQA, Foto, Reinigung, Beschichtung usw.). Als nächstes kann die 2D-Messtechnik (AOI) zur Kontrolle der Unebenheitsgröße und Durchmesserdimensionierung verwendet werden Kontrolle. Darüber hinaus kann die 3D-Messtechnik (AOI) für die Erfassung von Messinformationen zur Erhebung von Erhebungshöhen/Koplanaritätsmessungen verwendet werden (dies erfolgt typischerweise mit einer auf Lasertriangulation basierenden Technologie)“, sagte Nathan Peng, Produktmarketingmanager bei Auf Innovation. „Darüber hinaus kann die 3D-Messtechnik auf individuelle Höhenmerkmale von Unebenheiten abzielen, die typischerweise mit Weißlicht-Interferometer-Technologie erfasst werden. Außerdem gibt es Methoden zur Erkennung organischer Rückstände auf der Bump-Oberseite, die zu Fehlern bei der Bump-Pad-Verbindung führen können.“

Zusammenfassung

Produkte, die eine höhere Anzahl von Verbindungen erfordern, bestimmen weiterhin die Verbindungs-Roadmap. Jede Flip-Chip-Technologie hat Herstellungsgrenzen, die sich auf Materialeigenschaften, schrumpfende Größen, die Underfill-Technologien herausfordern, und den zunehmenden Einsatz von Lithographie zur Herstellung der Verbindungsstrukturen auswirken. Jede Änderung der Klebeprozesse führt zu einem Anstieg der Mess- und Prüfschritte, um die Ertrags- und Qualitätsziele zu erreichen.

Bibliographie

- https://en.wikipedia.org/wiki/Flip_chip

- https://eps.ieee.org/technology/heterogeneous-integration-roadmap/2021-edition.html

- HIR Kapitel 8 Single-Chip- und Multi-Chip-Integration, https://eps.ieee.org/images/files/HIR_2021/ch08_smcfinal.pdf

Ähnliche Beiträge:

Koplanarität und Inkonsistenzen der Unebenheiten führen zu Ertrags- und Zuverlässigkeitsproblemen

Die anspruchsvollen Verpackungsherausforderungen nehmen zu, da Chips und Packungsgrößen kleiner werden. Unterschiedliche Geräte und Technologien gewinnen an Bedeutung.

Die Bump-Zuverlässigkeit wird durch latente Defekte in Frage gestellt

Automatisierte Lösungen sind in Arbeit, aber ihre Entwicklung wird Zeit brauchen.

Große Veränderungen in den Bereichen Stromversorgung, Materialien und Verbindungen stehen bevor

Wie sich Herstellung und Verpackung in den nächsten Jahrzehnten verändern werden.

- SEO-gestützte Content- und PR-Distribution. Holen Sie sich noch heute Verstärkung.

- PlatoAiStream. Web3-Datenintelligenz. Wissen verstärkt. Hier zugreifen.

- Die Zukunft prägen mit Adryenn Ashley. Hier zugreifen.

- Kaufen und verkaufen Sie Anteile an PRE-IPO-Unternehmen mit PREIPO®. Hier zugreifen.

- Quelle: https://semiengineering.com/challenges-grow-for-creating-smaller-bumps-for-flip-chips/

- :hast

- :Ist

- :nicht

- :Wo

- $UP

- 000

- 1

- 10

- 100

- 250

- 2D

- 3d

- 40

- 7

- 8

- a

- Fähigkeit

- Fähig

- oben

- Erreichen

- Erwerb

- Action

- Handlungen

- berührt das Schneidwerkzeug

- Zusatz

- Zusätzliche

- Fügt

- vorantreiben

- advanced

- Nach der

- voraus

- LUFT

- ausrichten

- Alle

- erlauben

- erlaubt

- entlang

- ebenfalls

- an

- Analyse

- und

- Ein anderer

- jedem

- Anwendungen

- angewandt

- SIND

- Bereich

- Bereiche

- um

- AS

- Aussehen

- Aspekte

- Versammlung

- At

- anhängen

- Automation

- verfügbar

- ein Weg

- Zurück

- Ball

- basic

- Grundlage

- BE

- weil

- wird

- war

- Bevor

- Sein

- unten

- zwischen

- Beyond

- Big

- Tafel

- Anleihe

- Wander- und Outdoorschuhen

- beide

- bauen

- erbaut

- aber

- by

- kam

- CAN

- Kappe

- Fähigkeiten

- Erfassung

- Verursachen

- challenges

- herausgefordert

- Herausforderungen

- Chance

- Übernehmen

- Änderungen

- Kapitel

- Charakteristik

- chen

- Chip

- Pommes frites

- Wahl

- Entscheidungen

- näher

- Zusammenbruch

- zusammengebrochen

- wie die

- kommt

- gemeinsam

- häufig

- verglichen

- Komplex

- Komplexität

- Komponenten

- Computing

- begrifflich

- Hautpflegeprobleme

- Vernetz Dich

- Sich zusammenschliessen

- Verbindung

- Verbindungen

- Connects

- Überlegungen

- konsistent

- Kontakt

- Verunreinigungen

- fortsetzen

- fortgesetzt

- beitragen

- Smartgeräte App

- gesteuert

- Regelung

- Steuerung

- Kupfer

- Kernbereich

- Dazugehörigen

- könnte

- Paar

- erstellen

- erstellt

- Erstellen

- kritischem

- Strom

- Zur Zeit

- technische Daten

- Behandlung

- Jahrzehnte

- Entscheidung

- definiert

- definitiv

- Lieferanten

- Demand

- Dichte

- Abhängig

- hinterlegt

- Design

- entworfen

- Entdeckung

- Bestimmen

- entschlossen

- entwickeln

- entwickelt

- Geräte

- Sterben

- anders

- schwer

- Direktor

- Schmutz

- do

- Unterlagen

- die

- erledigt

- nach unten

- Antrieb

- Fahrer

- Treiber

- zwei

- im

- e

- E & T

- jeder

- entweder

- eingebettet

- ermöglichen

- ermöglicht

- Ende

- Ingenieur

- Entwicklung

- genug

- gewährleisten

- Arbeitsumfeld

- Ausrüstung

- etablierten

- etc

- Äther (ETH)

- entwickelt

- Beispiel

- existieren

- Expansion

- erwarten

- teuer

- erklärt

- exponentiell

- Anlagen

- Faktor

- Fabrik

- Scheitern

- Feige

- Finale

- Finden Sie

- Ende

- Vorname

- Wohnung

- Flexibilität

- Flip

- Fluss

- Fließt

- FLUX

- konzentriert

- Aussichten für

- für Ertrag

- Ausbildung

- gefunden

- für

- weiter

- Außerdem

- Gewinnen

- Lücke

- Lücken

- Allgemeines

- allgemein

- bekommen

- bekommen

- Glas

- Go

- Goes

- gehen

- Gold

- gut

- Mahlen

- Wachsen Sie über sich hinaus

- die Vermittlung von Kompetenzen,

- Griff

- hart

- Haben

- mit

- Höhe

- Höhen

- Hilfe

- High

- Hohe Leistungsfähigkeit

- höher

- historisch

- Loch

- HEISS

- Ultraschall

- Hilfe

- HTML

- HTTPS

- Hybrid

- i

- IBM

- IEEE

- Image

- Bild

- Imaging

- wirkt

- wichtig

- in

- Einschließlich

- Erhöhung

- hat

- zunehmend

- zunehmend

- Krankengymnastik

- Information

- Anfangs-

- Innovation

- beantragen müssen

- Integration

- Integrität

- verbindet

- in

- Investieren

- beteiligen

- IT

- Artikel

- SEINE

- selbst

- Landschaft

- größer

- laser

- Schicht

- führen

- Verlassen

- weniger

- Niveau

- Cholesterinspiegel

- !

- Gefällt mir

- LIMIT

- Einschränkung

- Einschränkungen

- Grenzen

- wenig

- Lang

- aussehen

- aussehen wie

- Los

- Sneaker

- Main

- um

- MACHT

- Management

- Manager

- flächendeckende Gesundheitsprogramme

- manuell

- manuell

- Herstellung

- viele

- Mapping

- Kennzeichen

- Markt

- Marketing

- Ihres Materials

- Materialien

- reifen

- max-width

- Mittel

- mechanisch

- Mechanismen

- Triff

- Treffen

- Memory

- erwähnt

- Metall

- Methode

- Methoden

- Metrologie

- Mikron

- Mikrofon

- Minimum

- Mobil

- überwacht

- mehr

- meist

- schlauer bewegen

- bewegt sich

- viel

- Multi

- Natur

- Need

- erforderlich

- Bedürfnisse

- Neu

- Neue Technologien

- weiter

- schön

- Super

- nicht

- bekannt

- jetzt an

- Anzahl

- of

- on

- einmal

- EINEM

- XNUMXh geöffnet

- Eröffnung

- Operator

- Betreiber

- Entwicklungsmöglichkeiten

- entgegengesetzt

- or

- bio

- ursprünglich

- Andere

- UNSERE

- übrig

- besitzen

- Paket

- Pakete

- Verpackung

- Unterlage

- Seite

- Parallel

- Teil

- Teilchen

- passieren

- Personen

- Säule

- Tonhöhe (Pitch)

- Stellplätze

- Ort

- Plato

- Datenintelligenz von Plato

- PlatoData

- Play

- Points

- Arm

- Beliebt

- beliebte Wahl

- positioniert

- möglich

- Post

- Werkzeuge

- Präsident

- primär

- Vor

- Prozessdefinierung

- anpassen

- Verarbeitung

- Produkt

- Produktmanagement

- Produktion

- Produkte

- projektiert

- immobilien

- die

- geschoben

- setzen

- Qualität

- Bereich

- Verhältnis

- Erreichen

- wirklich

- Empfang

- Veteran

- Reduziert

- reduziert

- Ungeachtet

- bezogene

- Zuverlässigkeit

- Vertrauen

- Entfernt

- erfordern

- falls angefordert

- erfordert

- Die Ergebnisse

- Risiko

- Fahrplan

- Roadmaps

- Rollen

- Zimmer

- Straße

- Routing

- Ohne eine erfahrene Medienplanung zur Festlegung von Regeln und Strategien beschleunigt der programmatische Medieneinkauf einfach die Rate der verschwenderischen Ausgaben.

- Said

- gleich

- Sekundär-

- sehen

- Sehen

- gesehen

- Halbleiter

- Senior

- Setup

- mehrere

- Form

- verschieben

- Short

- sollte

- Seite

- Signal

- Silizium

- ähnlich

- Ähnlich

- da

- Single

- Größe

- Größen

- Slides

- geringfügig

- kleinere

- So

- Lösungen

- einige

- etwas

- Bald

- Quelle

- Quellen

- Raumfahrt

- spezifisch

- speziell

- Standard

- Anfang

- Beginnen Sie

- Shritte

- Kleben

- Immer noch

- Geschichten

- Der Stress

- Es wurden Studien

- erfolgreich

- so

- Support

- Oberfläche

- SVG

- Tabelle

- Nehmen

- Target

- Technologies

- Technologie

- Begriff

- Testen

- als

- zur Verbesserung der Gesundheitsgerechtigkeit

- Das

- Die Landschaft

- ihr

- Sie

- Thema

- dann

- Dort.

- deswegen

- Thermal-

- Diese

- vom Nutzer definierten

- Denken

- fehlen uns die Worte.

- diejenigen

- obwohl?

- dicht

- Zeit

- Tip

- zu

- heute

- gemeinsam

- Werkzeug

- Werkzeuge

- Top

- Spur

- Zugkraft

- traditionell

- versuchen

- WENDE

- XNUMX

- tippe

- Typen

- typisch

- für

- auf

- -

- benutzt

- Verwendung von

- gewöhnlich

- Nutzen

- Vielfalt

- sehr

- Vizepräsident:in

- Anzeigen

- ungültig machen

- wurde

- we

- GUT

- wann

- welche

- Weiß

- ganze

- weit verbreitet

- Wikipedia

- werden wir

- mit

- ohne

- Arbeiten

- arbeiten,

- Werk

- weltweit wie ausgehandelt und gekauft ausgeführt wird.

- X

- Röntgenstrahl

- Ausbeute

- Erträge

- U

- Ihr

- Zephyrnet