In der Terminologie integrierter Schaltkreise ist ein Spannungsabfall der Spannungsabfall, der in einem Schaltkreis auftritt. Dies ist ein bekanntes Phänomen und kann aus folgenden Gründen auftreten. Die Stromversorgung fällt unter den Betriebsbereich, für den ein Chip ausgelegt ist, was zu einem Spannungsabfall führt. Die leitenden Elemente ziehen mehr Strom als vorgesehen, was zu einem Spannungsabfall führt. Manchmal können auch Signalstörungen oder Rauschen im Netzteil zu Spannungsschwankungen führen, die zu einem Spannungsabfall führen.

Droops können den Betrieb eines Schaltkreises beeinträchtigen. Eine dieser Auswirkungen ist eine verringerte Leistung des Chips, die zu längeren Verarbeitungszeiten führt. Im Folgenden sind jedoch einige der schwerwiegenderen und/oder katastrophaleren Auswirkungen aufgeführt. Der Chip könnte mehr Strom ziehen, um das Leistungsniveau aufrechtzuerhalten, was zu einem höheren Stromverbrauch und einer höheren Wärmeableitung führen würde. Dies kann zu einer verkürzten Lebensdauer des Chips und in schweren Fällen aufgrund von Setup- und Hold-Variationen zu einem vollständigen Ausfall des Chips führen. Droops können auch zu Datenbeschädigungen oder Fehlern in der Ausgabe führen. Dies ist ein sehr ernstes Problem für Anwendungen, die auf die Genauigkeit und Zuverlässigkeit des Chips angewiesen sind.

Selbstverständlich wird das Phänomen der Droops bei der Entwicklung von Chips und Systemen ernsthaft berücksichtigt. Die gebräuchlichsten Methoden zur Minderung von Spannungsabfällen sind die Entkopplung der Stromversorgung, die Spannungsregelung, die Schaltungsoptimierung und das Energiemanagement auf Systemebene. Die Bedingungen und die Betriebsumgebung, in der der Chip betrieben wird, werden bei der Entwicklung von Lösungen zur Minderung von Störungen sorgfältig berücksichtigt.

Moderne Probleme

Da SoCs immer komplexer werden, können auch Droop-Probleme recht komplex werden. Das Design eines SoC muss im Hinblick auf Leistung, Strom, Kosten, Formfaktor usw. optimiert werden, zusätzlich zur Optimierung der Droop-Abschwächung. Manchmal können diese Optimierungsziele miteinander konkurrieren und gegenläufig sein und es müssen Kompromisse eingegangen werden. Beispielsweise können SoC-Architekten die Betriebsspannung erhöhen und so einen Spielraum schaffen, um lokale und globale Spannungsabfälle zu umgehen. Dieser Anstieg erhöht jedoch quadratisch die Leistung. Alternativ können Designer ihre Taktgeneration an den Statik anpassen, wodurch die Leistung eine Funktion der Schaltzeit der Taktgeneration wird.

Daher sind große SoCs im Rechenzentrums- und KI-Bereich besonders anfällig für Störungen. Die Arbeitsbelastung der Kunden ist sehr unterschiedlich und dynamisch, was zu erheblichen Schwankungen bei der Schaltaktivität und der Stromaufnahme führt. Natürlich können es sich Systeme nicht leisten, Droop-Probleme unberücksichtigt zu lassen. Die potenzielle Haftung durch ungenaue Ausgabe oder einen katastrophalen Ausfall eines Chips ist für heutige Systeme und Anwendungen zu hoch.

Lokalisierte Droop-Probleme

Anwendungsspezifische Beschleuniger werden häufig zusammen mit Allzweckprozessoren eingesetzt, um die Leistung und Energieeffizienz zu liefern, die in den heutigen anspruchsvollen Computerumgebungen erforderlich sind. Doch diese Beschleuniger sowie die zunehmende Anzahl von Kernen und die asymmetrische Natur der Arbeitslasten erhöhen das Risiko lokaler Spannungseinbrüche. Diese lokalisierten Spannungsabfälle sind das Ergebnis eines plötzlichen Anstiegs der Schaltaktivität und können vorübergehende Störungen und potenzielle Ausfälle im Einsatzmodus verursachen.

Wenn lokale Abweichungen auftreten, können die Auswirkungen durch dynamische Frequenzskalierung abgemildert werden. Dies wird erreicht, indem das Timing einer Schaltung mithilfe einer programmierbaren Uhr angepasst wird. Eine programmierbare Uhr ermöglicht die dynamische Anpassung der Taktfrequenz und des Timings basierend auf den aktuellen Betriebsbedingungen der Schaltung.

Movellus macht es einfach, lokalisierte Erschlaffungen zu beheben

Movellus, ein führender Anbieter digitaler System-IP, hat die Aeonic Generate-Produktfamilie entwickelt, um lokale Störungen zu beheben. Das Movellus Aeonic-Portfolio bietet adaptive Taktungslösungen, die eine schnelle Reaktion auf Abweichungen ermöglichen. Zum Portfolio gehört das adaptive Clocking-System. Die Bausteine werden mit synthetisierbarem Verilog erstellt, was sie von Natur aus flexibel macht. Die Lösungen sind konfigurierbar, scanbar und prozessportabel für eine Vielzahl fortschrittlicher SoC-Anwendungen.

Die Aeonic Generate-Produktfamilie ist zudem deutlich kleiner als herkömmliche analoge Lösungen. Dadurch können Designer das IP mit der erforderlichen Granularität instanziieren, ohne dass es zu nennenswerten Auswirkungen auf den Bereich kommt. Darüber hinaus wird der Aeonic Generate-Bereich mit der Entwicklung hin zu feineren Prozessgeometrien weiter skaliert, was ihn zu einer idealen Lösung für zukünftige Designs macht.

Ein paar Anwendungsfälle

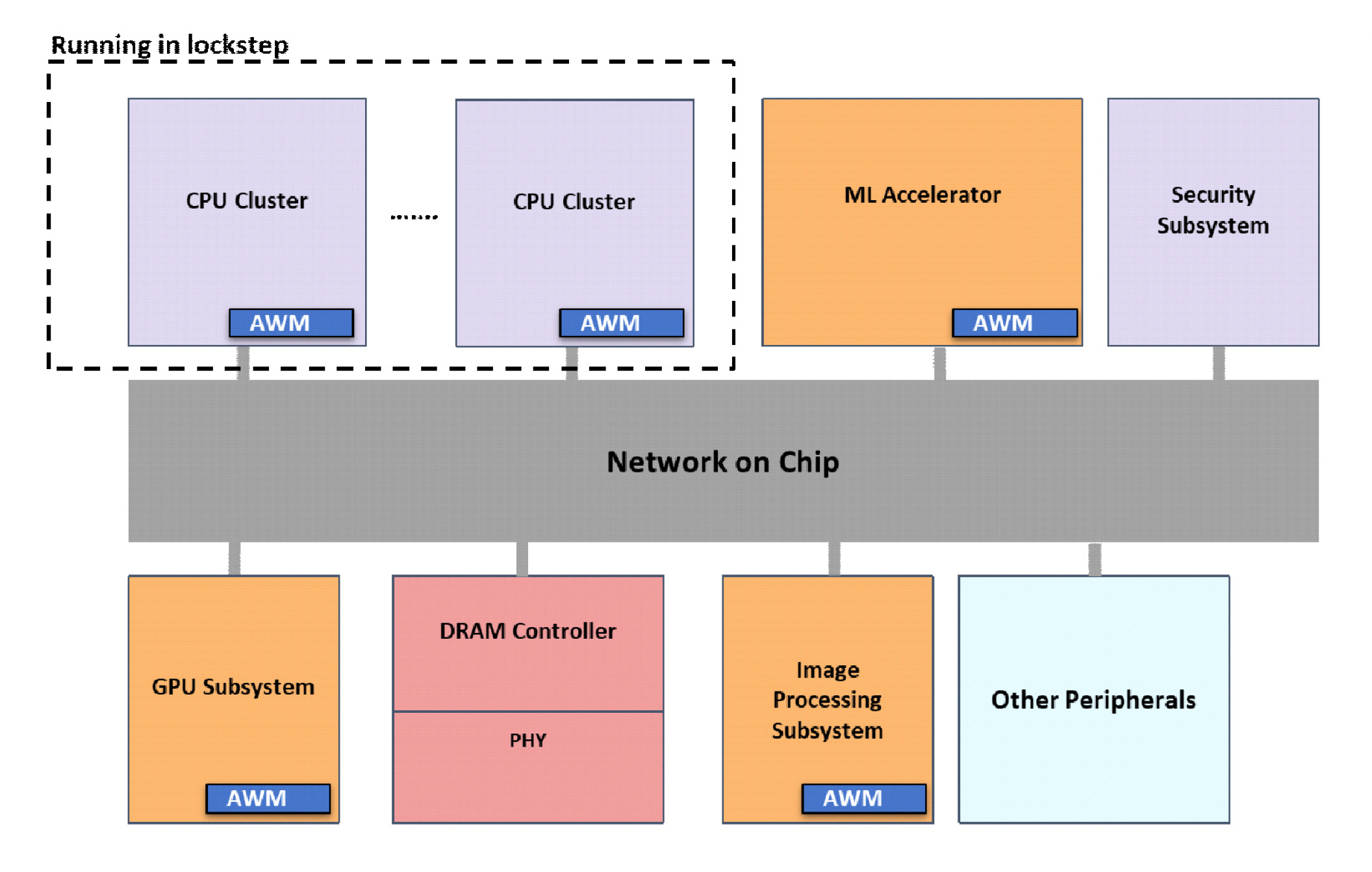

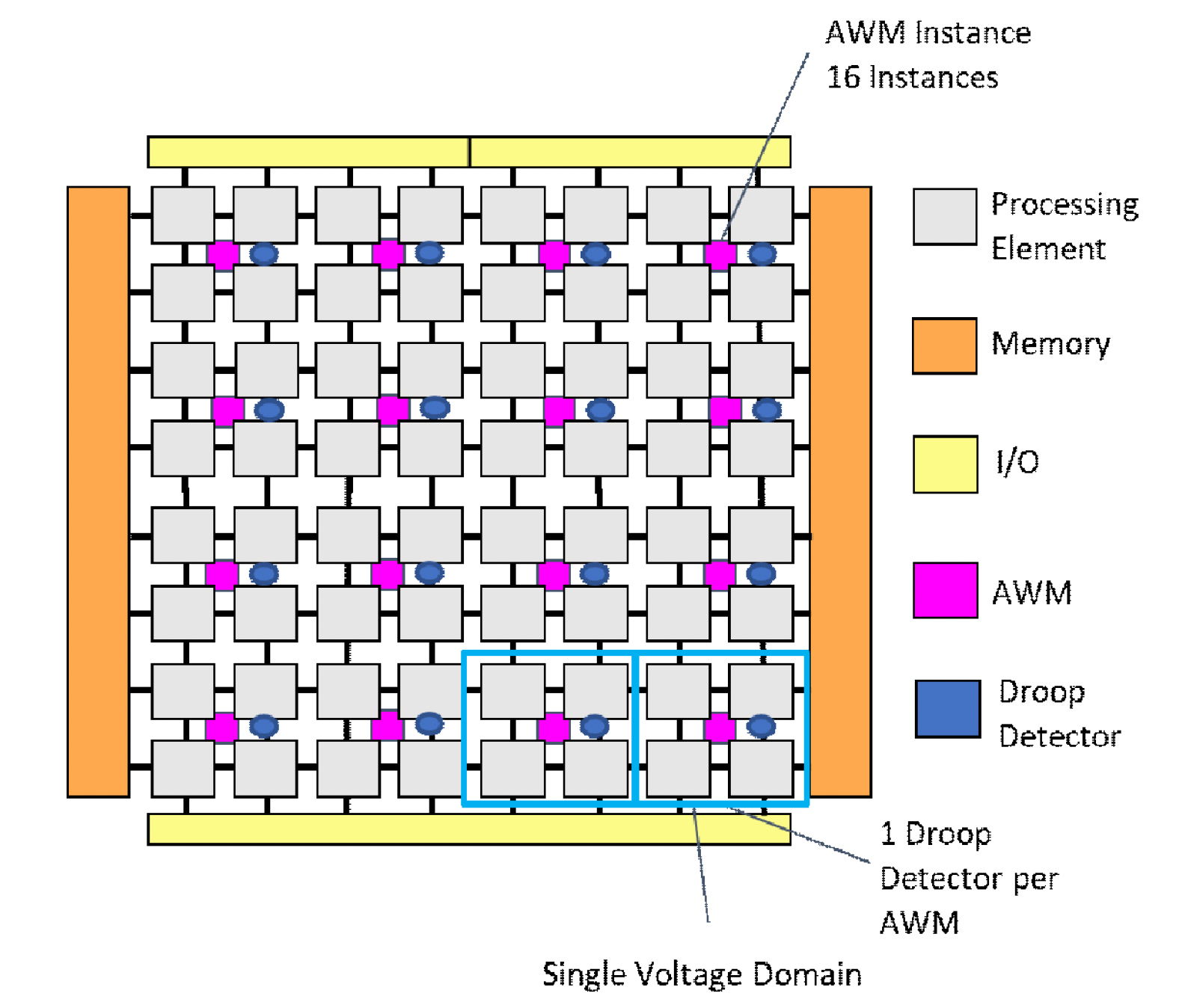

Die folgende Abbildung von Movellus zeigt eine Beispielarchitektur eines ADAS-Prozessors mit der Aeonic Generate AWM-Plattform für lokalisierte Droop-Unterstützung. Ein Architekt würde ein AWM-Modul mit einem anwendungsspezifischen Unterblock oder Beschleuniger koppeln, um auf arbeitslastbedingte lokale Abweichungen innerhalb von fünf Taktzyklen mit störungsfreien und schnellen Frequenzverschiebungen zu reagieren. Dieser Ansatz bietet eine zuverlässige und effiziente Lösung für die Bewältigung der Herausforderungen lokaler Störungen in den Märkten für ADAS, 5G und Rechenzentrumsnetzwerke.

Die folgende Abbildung von Movellus zeigt eine Beispielarchitektur eines Prozessor-SoCs mit Aeonic Generate für lokalisierte Droop-Unterstützung. Ein Architekt würde ein Aeonic Generate AWM-Modul mit einem Statikdetektor für den Prozessorcluster und die zugehörige Spannungsdomäne kombinieren, um schnell auf arbeitslastbedingte lokalisierte Ströme zu reagieren. Dadurch können Entwickler eine lokalisierte und unabhängige Droop-Reaktion liefern, ohne die Leistung benachbarter Prozessorcluster zu beeinträchtigen.

Zusammenfassung

In heterogenen SoCs mit anwendungsspezifischen Beschleunigern kann es zu örtlich begrenzten Spannungseinbrüchen kommen. Diese Störungen können zu Zeitstörungen, vorübergehenden Störungen und Ausfällen im Einsatzmodus in ADAS, Rechenzentrumsnetzwerken und 5G-Anwendungen führen. Systemarchitekten können eine adaptive Taktung implementieren, um auf diese Störungen zu reagieren und die Auswirkungen abzumildern.

Die Movellus™ Aeonic Generate Adaptive Workload Module (AWM)-Familie leistungsstarker IP-Produkte zur Takterzeugung ist Teil der Aeonic Intelligent Clock Network™-Architektur. Weitere Informationen finden Sie im Movellus-Dokument. Aeonic Generate™ AWM-Seite.

Lesen Sie auch:

Vorteile groß angelegter synchroner Taktdomänen in KI-Chipdesigns

Es ist jetzt Zeit für Smart-Clock-Netzwerke

Vorteile bei Leistung, Leistung und Fläche (PPA) durch intelligente Taktnetzwerke

Teile diesen Beitrag über:

- SEO-gestützte Content- und PR-Distribution. Holen Sie sich noch heute Verstärkung.

- Platoblockkette. Web3-Metaverse-Intelligenz. Wissen verstärkt. Hier zugreifen.

- Quelle: https://semiwiki.com/ip/326488-adaptive-clock-technology-for-real-time-droop-response/

- :Ist

- 5G

- a

- Beschleuniger

- Beschleuniger

- Genauigkeit

- erreicht

- Aktivität

- automatisch

- ADAs

- Zusatz

- zusätzlich

- Adresse

- Adressierung

- Bereinigt

- advanced

- AI

- erlaubt

- und

- Anwendungen

- Ansatz

- Architektur

- SIND

- Bereich

- AS

- damit verbundenen

- At

- basierend

- BE

- werden

- unten

- Vorteile

- Blockieren

- Blockiert

- Building

- erbaut

- by

- CAN

- Kann bekommen

- kann keine

- vorsichtig

- Fälle

- katastrophal

- Verursachen

- Center

- Herausforderungen

- Chip

- Pommes frites

- Uhr

- Cluster

- gemeinsam

- konkurrieren

- abschließen

- Komplex

- Berechnen

- Computing

- Bedingungen

- Berücksichtigung

- betrachtet

- Verbrauch

- weiter

- Korruption

- Kosten

- könnte

- Counter

- Paar

- Kurs

- Strom

- Kunde

- Zyklen

- technische Daten

- Data Center

- Datacenter

- Tag

- Übergeben

- anspruchsvoll

- Design

- entworfen

- Designer

- Entwerfen

- Designs

- entwickelt

- digital

- verteilt

- verschieden

- Domain

- Domains

- gezogen

- Drop

- Drops

- dynamisch

- dynamisch

- jeder

- Effizienz

- effizient

- Elemente

- Arbeitsumfeld

- Umgebungen

- Fehler

- etc

- Beispiel

- Scheitern

- Stürze

- Familie

- Abbildung

- flexibel

- Schwankungen

- Folgende

- Aussichten für

- unten stehende Formular

- Frequenz

- für

- Funktion

- Zukunft

- allgemeiner Zweck

- erzeugen

- Generation

- bekommen

- Global

- Go

- Ziele

- passieren

- das passiert

- Haben

- High

- Hohe Leistungsfähigkeit

- HTTPS

- ideal

- Impact der HXNUMXO Observatorien

- Einfluss hat

- implementieren

- in

- ungenau

- Dazu gehören

- Erhöhung

- hat

- Steigert

- zunehmend

- unabhängig

- Information

- integriert

- Integration

- Intelligent

- intrinsisch

- IP

- Problem

- Probleme

- IT

- grosse

- großflächig

- führen

- führenden

- Niveau

- Haftung

- Lebensdauer

- aus einer regionalen

- länger

- gemacht

- halten

- MACHT

- Making

- Management

- Marge

- Märkte

- max-width

- Methoden

- Mildern

- mildernd

- Milderung

- Modulen

- Module

- mehr

- vor allem warme

- schlauer bewegen

- Natur

- Bedürfnisse

- Netzwerk

- Vernetzung

- Lärm

- vor allem

- Anzahl

- of

- Angebote

- on

- EINEM

- die

- Einkauf & Prozesse

- Optimierung

- optimiert

- Optimierung

- Andere

- Möglichkeiten für das Ausgangssignal:

- Teil

- Leistung

- Durchführung

- Phänomen

- Plattform

- Plato

- Datenintelligenz von Plato

- PlatoData

- Mappe

- Post

- Potenzial

- Werkzeuge

- Labor-Stromversorgungen

- Prozessdefinierung

- Verarbeitung

- Prozessor

- Prozessoren

- Produkte

- Versorger

- bietet

- erhöhen

- Angebot

- schnell

- schnell

- Lesen Sie mehr

- Echtzeit

- Gründe

- Reduziert

- Rechtliches

- Zuverlässigkeit

- zuverlässig

- falls angefordert

- Reagieren

- Antwort

- Folge

- was zu

- Rise

- Risiko

- Führen Sie

- Skalieren

- Skalierung

- WASSER

- ernst

- Setup

- schwer

- Schichten

- Konzerte

- Signal

- signifikant

- bedeutend

- kleinere

- smart

- Lösung

- Lösungen

- einige

- Raumfahrt

- so

- plötzlich

- liefern

- Support

- empfänglich

- System

- Systeme und Techniken

- Tandem

- Technologie

- Terminologie

- zur Verbesserung der Gesundheitsgerechtigkeit

- Das

- Die Gegend

- ihr

- Sie

- Diese

- Durch

- Zeit

- mal

- zeitliche Koordinierung

- zu

- heutigen

- auch

- traditionell

- -

- sehr vielfältig

- Stromspannung

- GUT

- bekannt

- welche

- breit

- Große Auswahl

- weit

- werden wir

- mit

- .

- ohne

- würde

- Zephyrnet