I moderne CPU-enhedsdrift er 80% til 90% af energiforbruget og tidsforsinkelser forårsaget af bevægelse af data mellem CPU'en og off-chip-hukommelsen. For at afhjælpe denne ydeevne bekymring tilføjer designere yderligere on-chip hukommelse til deres CPU'er. Traditionelt har SRAM været den mest udbredte on-chip CPU-hukommelsestype. Desværre er SRAM i øjeblikket begrænset til en størrelse på hundredvis af megabyte. Denne hukommelsesbegrænsning på chip kan være utilstrækkelig til førende applikationer.

Fremtidige CPU-applikationer, såsom programmering af AI Language Model og billedbehandling til 8K UHD-video, vil kræve I/O-hukommelsesadgangsbåndbredde i området 10 terabyte/sek. For at opfylde disse båndbreddekrav skal on-chip CPU-hukommelse være større end 1 terabyte i størrelse. Et SRAM-alternativ kan være nødvendigt for at opfylde disse fremtidige krav til on-chip-hukommelse. En mulig løsning på dette problem ville være at bruge Resistive Random Access Memory (ReRAM). [1,2,3]

En ReRAM-enhed er en ikke-flygtig hukommelsescelle, der indeholder memristormaterialer. Disse materialer fungerer som en dielektrisk isolator. Når en tilstrækkelig høj spænding påføres, dannes en ledningsbane. Typiske hukommelsesmaterialer brugt som memristorer inkluderer HfO2, Ta2O5og TiO2. [4] Hukommelsescellens resistive tilstand kan læses ved hjælp af elektroniske kredsløb for at bestemme, om hukommelsescellen er programmeret eller slettet, og dermed identificere hukommelsesbittens tilstand. ReRAM-hukommelsesceller kan stables lodret, ligesom 3D-NAND-arkitektur, for at øge lagertætheden.

I denne artikel, SEMulator3D virtuel fremstilling vil blive brugt til processtifinding og visualisering af potentielle 3D ReRAM-arkitekturer. Vi vil estimere cellemodstanden som en funktion af hukommelsescelleformen sammen med Id-Vg-ydelsen af den indlejrede kanaltransistor i en ReRAM-enhed.

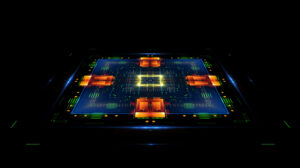

En 3D ReRAM-model er vist i figur 1. Enheden har 64 lag af ordlinjer (WL) med søjler placeret i et sekskantet array. Ordlinjerne er dannet med vekslende lag af metalliske ledere og oxiddielektrikum. Søjlerne ætses gennem WL og derefter aflejres et tyndt lag hukommelsesmateriale på søjlernes sidevægge. Hukommelsesmaterialet fjernes fra bunden og toppen af søjlerne og efterlader kun materialet på søjlens sidevægge. Søjlerne fyldes derefter med ildfast metal og wolfram.

Under array-lagene er kontakter og metalforbindelser til source, drain og gates af gate-all-around felteffekttransistorer (GAA FET). Transistor-drænet forbindes til hukommelsesarray-søjlen og kombineres med WL-kredsløbet for at give funktion til hver hukommelsescelle.

Hukommelsescellen består af to metalelektroder: den metalliske lederordlinje og en ildfast metalelektrode (figur 2). Under virtuel processimulering af denne enhed vil vi bruge procesvariabler til at indstille og nulstille memristoren. En bevidst påført spænding vil skabe mikroskopiske ledende baner kaldet ledende filamenter. Når elektriske signaler med forskellige polariteter påføres, bevæger de ladede ioner inde i memristoren sig for at danne (sætte) eller opløse (nulstille) det ledende filament.

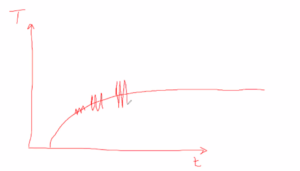

Den ledende filamentmodstand varierer ved forskellige programspændinger. Lavmodstandstilstanden er i området 10k ohm (indstillet), og højmodstandstilstanden er i området 1M ohm (nulstil). [5] Vi udviklede en virtuel model til at demonstrere koblingsmodstandene for en 3D ReRAM-enhed, med resultater vist i figur 3. Den høje resistive tilstand af memristoren er ca. 100 gange højere modstand end den lave resistive tilstand.

Et virtuelt design af eksperimenter (DOE) blev derefter udført for bedre at forstå sammenhængen mellem hukommelsescellens modstandsforhold og størrelsen og formen af hukommelsescellen. Forsøgets variabler var søjle CD, WL tykkelse og memristor tykkelse. Analyse af DOE-resultaterne indikerer, at søjle-CD og tykkelsen af memristoren drev den mest signifikante respons. Figur 4 viser et konturplot af hukommelsescellens modstandsforhold versus disse to variable. Der var en 3X ændring i hukommelsescellemodstanden for høje værdier af søjleradius og memristortykkelse. Forskellene i hukommelsescellens form på tværs af det undersøgte område vil ikke påvirke evnen til at læse memristorens hukommelsestilstande, men kunne påvirke evnen til at skelne programtilstande i en multibit pr. celle enhed.

Memristoren kan programmeres med en strømstyrke < 0.10 uA og en spænding < 0.5V. Disse spændings- og strømindstillinger gør det muligt for memristorer (ReRAM-hukommelse) nemt at integrere som on-chip-hukommelse i avancerede logiske enheder. SEMulator3D-enhedssimulering har tidligere vist, at en GAA FET under-array-transistor skulle være i stand til at drive den spænding og strøm, der kræves af de indstillede og nulstillede tilstande for en memristorhukommelsescelle. [6]

To store problemer ved moderne CPU-enheder er energiforbrug og forsinkelsestid forårsaget af databevægelse mellem CPU'en og off-chip-hukommelsen. Forøgelse af størrelsen af on-chip-hukommelse kan løse disse problemer. I denne undersøgelse har vi brugt SEMulator3D til at undersøge integrationen af et SRAM-alternativ (ReRAM) til CPU til on-chip-hukommelse. Vi brugte en virtuel model til bedre at forstå procestrin og potentielle layoutproblemer for individuelle memristorceller. Vi udførte også undersøgelser for at undersøge memristorens indstillede og nulstillede tilstande og effekten af enhedsdimensioner (hukommelsescelleform og størrelse) på ordlinjemodstand. Vi fremhævede, at ReRAM indbygget hukommelse kan integreres med avanceret logik ved at bruge en GAA pFET transistor elektrisk udgang til at indstille og nulstille memristorcellerne. Disse resultater bekræfter, at Resistive Random Access Memory (ReRAM) er et lovende alternativ til indbygget SRAM-hukommelse til fremtidige logiske applikationer med høj båndbredde.

Referencer

- Lanza, Mario (2014). "En gennemgang af resistiv omskiftning i højk-dielektrik: Et synspunkt på nanoskala ved hjælp af ledende atomkraftmikroskop". Materialer, vol. 7, udgave 3, s. 2155-2182, doi:10.3390/ma7032155.

- N. Sedghi, et al, "The role of nitrogen doping in ALD Ta2O5 and its influence on multilevel cell switching in RRAM", marts 2017, Applied Physics Letters, DOI:10.1063/1.4978033

- Y. Bai, Et Al, "Studie af karakteristika på flere niveauer for 3D Vertical Resistive Switching Memory" Videnskabelige rapporter bind 4, artikelnummer: 5780 (2014)

- Chen, YC, Sarkar, S., Gibbs, JG, Huang, Y., Lee, JC, Lin, CC, & Lin, CH (2022). "Nano spiralformet dobbeltfunktionel resistiv hukommelse til laveffekt tværstangsarrayanvendelse.", ACS Applied Engineering Materials, 1(1), 252-257.

- Y. Wu, et al, "Nanometer-Scale HfOx RRAM", IEEE Electron Device Letters, bind: 34, udgave: 8. august 2013), doi:10.1109/LED.2013.2265404

- V. Sreenivasulu, et al, "Circuit Analysis and Optimization of GAA Nanowire FET Towards Low Power and High Switching", 11. november 2021, Computer Science, doi:10.1007/s12633-022-01777-6.

Brett Lowe

Brett Lowe er leder i halvlederproces- og integrationsteamet hos Coventor, et Lam Research Company. Han har arbejdet med udvikling af halvlederteknologi i mere end 35 år. Han begyndte sin karriere hos Philips Semiconductors, hvor han arbejdede med fremstilling og procesudvikling som procesingeniør inden for fotolitografi, tørætsning og våd proces. Derefter tilbragte han otte år hos Zilog, hvor han arbejdede med enhedsprocesudvikling. Senere kom Brett til Micron Technology, hvor han arbejdede med DRAM og 3D NAND procesudvikling og integration. Hos Coventor er hans fokus på at støtte virksomhedens kunder i deres 3D-halvlederprocesmodellering og teknologiudviklingskrav.

- SEO Powered Content & PR Distribution. Bliv forstærket i dag.

- PlatoData.Network Vertical Generative Ai. Styrk dig selv. Adgang her.

- PlatoAiStream. Web3 intelligens. Viden forstærket. Adgang her.

- PlatoESG. Kulstof, CleanTech, Energi, Miljø, Solenergi, Affaldshåndtering. Adgang her.

- PlatoHealth. Bioteknologiske og kliniske forsøgs intelligens. Adgang her.

- Kilde: https://semiengineering.com/developing-reram-as-next-generation-on-chip-memory-for-machine-learning-image-processing-and-other-advanced-cpu-applications/

- :har

- :er

- :ikke

- :hvor

- 1

- 10

- 100

- 10K

- 11

- 16

- 1M

- 2013

- 2014

- 2017

- 2021

- 2022

- 35 %

- 3d

- 400

- 7

- 75

- 8

- 8k

- a

- evne

- I stand

- adgang

- tværs

- Lov

- tilføje

- Yderligere

- fremskreden

- påvirke

- AI

- AL

- Alle

- Alle indlæg

- lindre

- tillade

- sammen

- også

- alternativ

- an

- analyse

- ,

- Anvendelse

- applikationer

- anvendt

- cirka

- arkitektur

- ER

- områder

- Array

- artikel

- AS

- At

- atomare

- AUGUST

- b

- båndbredde

- BE

- været

- begyndte

- Bedre

- mellem

- Bit

- Sort

- Bund

- brun

- Bundle

- men

- by

- kaldet

- CAN

- Karriere

- forårsagede

- CD

- celle

- Celler

- center

- lave om

- Kanal

- karakteristika

- opladet

- kombinerer

- selskab

- Selskabs

- sammenlignet

- computer

- Datalogi

- Bekymring

- dirigent

- Bekræfte

- forbinder

- består

- forbrug

- kontakter

- indeholder

- Korrelation

- kunne

- CPU

- skabe

- oprettet

- Cross

- Nuværende

- For øjeblikket

- Kunder

- mørk

- data

- forsinkelse

- forsinkelser

- demonstrere

- demonstreret

- tæthed

- deponeret

- Design

- designere

- Bestem

- udviklet

- udvikling

- Udvikling

- enhed

- Enheder

- forskel

- forskelle

- forskellige

- størrelse

- skelne

- vises

- displays

- DOE

- dræne

- tegning

- køre

- tørre

- i løbet af

- E&T

- hver

- nemt

- Edge

- effekt

- otte

- elektronisk

- indlejret

- energi

- Energiforbrug

- ingeniør

- Engineering

- skøn

- Ether (ETH)

- undersøge

- henrettet

- eksperiment

- eksperimenter

- FET

- felt

- Figur

- fyldt

- Fokus

- Til

- Tving

- formular

- dannet

- formularer

- fundet

- fra

- funktion

- fremtiden

- gate

- Gates

- generation

- graf

- større

- Grøn

- Have

- he

- Høj

- højere

- Fremhævet

- hans

- HTTPS

- Huang

- Hundreder

- ID

- identificere

- IEEE

- if

- billede

- in

- omfatter

- Forøg

- stigende

- angiver

- individuel

- indflydelse

- indvendig

- integrere

- integreret

- integration

- ind

- undersøge

- spørgsmål

- ITS

- sluttede

- Lam

- Sprog

- senere

- lag

- lag

- Layout

- førende

- læring

- forlader

- Lee

- til venstre

- ligesom

- Limited

- lin

- logik

- Lav

- maskine

- machine learning

- større

- leder

- Produktion

- Marts

- Mario

- materiale

- materialer

- max-bredde

- Kan..

- Mød

- Hukommelse

- metal

- micron

- model

- modellering

- Moderne

- mere

- mest

- bevæge sig

- bevægelse

- Behov

- behov

- næste

- november

- nummer

- of

- OHM

- on

- ONE

- kun

- drift

- optimering

- or

- Andet

- output

- sti

- stier

- per

- ydeevne

- Philips

- Fysik

- Søjle

- søjler

- lyserød

- placeret

- plato

- Platon Data Intelligence

- PlatoData

- Punkt

- Synspunkt

- mulig

- Indlæg

- potentiale

- magt

- tidligere

- Problem

- problemer

- behandle

- forarbejdning

- Program

- programmerede

- Programmering

- lovende

- give

- tilfældig

- rækkevidde

- forholdet

- Læs

- Rød

- fjernet

- Rapporter

- kræver

- påkrævet

- Krav

- forskning

- Modstand

- svar

- Resultater

- gennemgå

- højre

- roller

- s

- Videnskab

- videnskabelig

- Sektion

- halvleder

- Halvledere

- sæt

- indstillinger

- Shape

- bør

- vist

- side

- signaler

- signifikant

- simulation

- Størrelse

- løsninger

- SOLVE

- Kilde

- brugt

- stablet

- Tilstand

- Stater

- Steps

- opbevaring

- studeret

- undersøgelser

- Studere

- sådan

- Støtte

- hold

- Teknologier

- Teknologiudvikling

- end

- at

- Grafen

- The Source

- Staten

- deres

- derefter

- Der.

- Disse

- denne

- Gennem

- Dermed

- tid

- gange

- timing

- til

- top

- mod

- traditionelt

- to

- typen

- typisk

- under

- forstå

- desværre

- enhed

- brug

- anvendte

- ved brug af

- Værdier

- forskellige

- versus

- lodret

- lodret

- video

- Specifikation

- Virtual

- visualisering

- Spænding

- bind

- vs

- var

- we

- WebP

- var

- hvornår

- mens

- hvid

- bredt

- vilje

- med

- arbejdede

- arbejder

- ville

- wu

- år

- zephyrnet