Designere har mange veje til at differentiere RISC-V-løsninger. Én sti starter i forskellige RISC-V-kernetilpasninger og udvidelser i henhold til specifikationen. En anden fokuserer på at udvælge og samle IP-blokke i et komplet system-on-chip (SoC) design omkring en eller flere RISC-V kerner. En tredje er ved at dukke op: sammenkobling af RISC-V-kerner og andre IP-blokke med en netværk-på-chip (NoC) i stedet for en simpel busstruktur. Og det er ikke kun i den høje ende – parring af RISC-V-kerner med NoC'er besvarer mange SoC-designudfordringer, hvor data skal flyde effektivt i enhver arbejdsbyrde ved hjælp af enhver on-chip-protokol.

Præstationsniveauer ændres med avancerede sammenkoblingsordninger

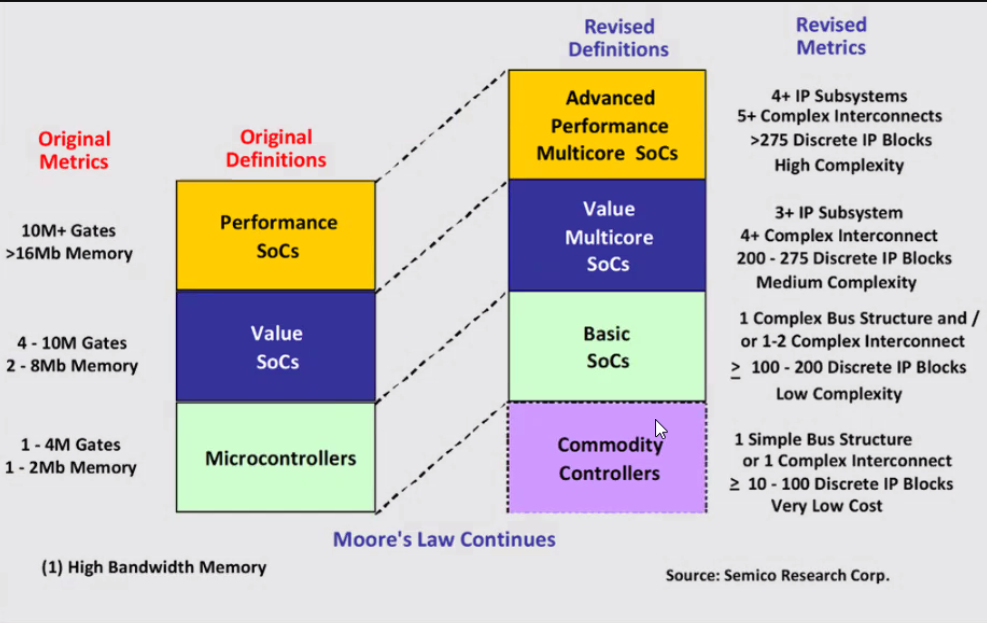

Blot at tælle porte, kerner og perifere blokke beskriver ikke længere ydeevnepotentialet i et SoC-design. Sammenkoblingsskemaer definerer nu linjerne mellem SoC-ydeevneniveauer, ifølge Semico Research, og et nyt niveau er åbnet, hvor sammenkoblinger skifter fra simple busstrukturer til mere sofistikerede ordninger.

Semicos opdaterede definition anerkender tre kræfter, der virker: flerkernedesigners udbredelse, en højere bar for, hvad der betragtes som et komplekst design, og den efterfølgende slørede linje mellem "mikrocontroller" og "SoC." I Semicos seneste opfattelse, tæller begrebet gate som en metrik, da en moderne processorkerne kan trække mange gates med sig. Kompleksitet bliver en funktion af sammenkoblinger, der varierer med undersystemer og forskellige IP-blokke.

SoC-præstationsniveauer, billede udlånt af Semico Research Corp.

Hvor en simpel bus vil gøre det, sandsynligvis en del med en enkelt processorkerne og lav-duty-cycle periferiudstyr, der ikke konstant kæmper om bussen, ser Semico et råvarecontroller-niveau. Alt over det bliver en SoC, formentlig med i det mindste nogle perifere enheder, der kæmper for on-chip båndbredde og opmærksomhed fra processorkernen(erne). Højere SoC-niveauer har flere kerner og flere IP-undersystemer, hver med tunet sammenkoblingsteknologi.

NoC'er opfanger flere protokoller og undersystemer

RISC-V har hurtigt rykket op på disse præstationsniveauer, efterhånden som mere kraftfulde kerner dukker op, med ikke mindre anvendelighed i den nederste ende af Semico-skalaen. Imidlertid kan RISC-V-designere have mindre erfaring med komplekse sammenkoblingsordninger set i de højere niveauer. "TileLink kan være den første tanke for RISC-V-interconnect, men det kan være svært at bruge i mere komplekse scenarier," siger Frank Schirrmeister, VP for løsninger og forretningsudvikling for Arteris.

En NoCs superkraft er dens evne til at forbinde undersystemer ved hjælp af forskellige protokoller, og SoC-designere vil sandsynligvis løbe ind i flere protokoller med selv moderat kompleksitet. AXI udjævnede vilkårene for simple IP-blokforbindelser. Multicore-løsninger med co-processing-blokke kræver cache-kohærens, hvilket giver anledning til CHI-protokollen. I/O-hukommelsesdeling hjalp med at forme den hurtigere CXL-forbindelse. "Når det er tid til at co-optimere databehandling og transport med forskellige undersystemer og protokoller i spil, er en NoC en bedre løsning," fortsætter Schirrmeister.

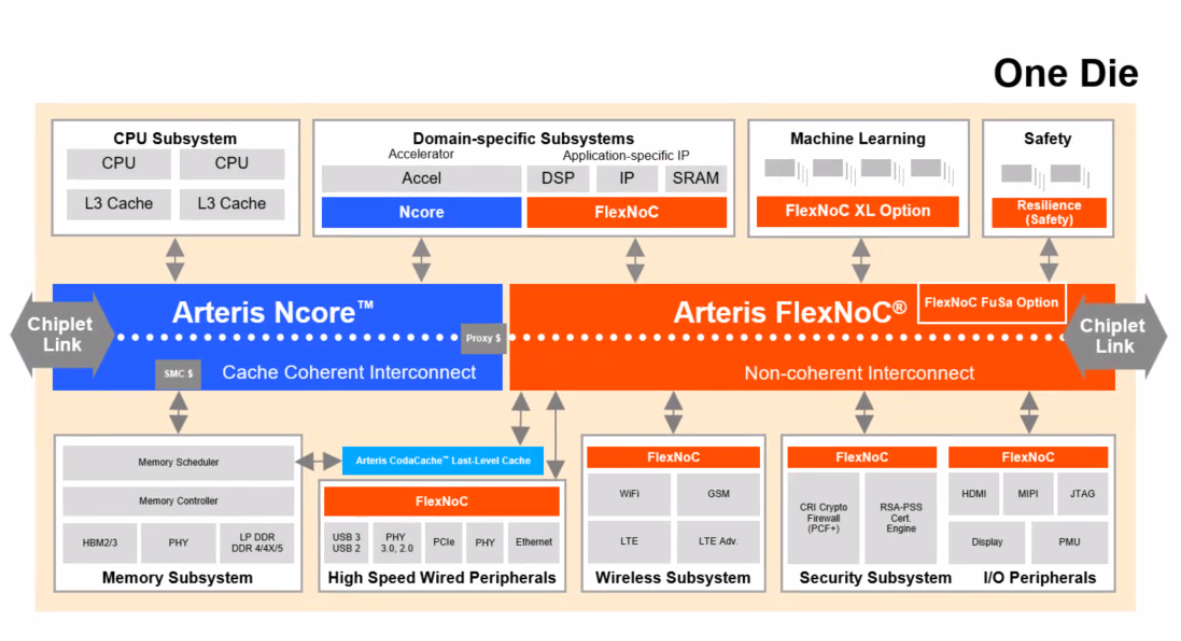

Hvordan kan parring af RISC-V-kerner med NoC'er se ud? Arteris kunde Tenstorrent giver et indblik i mulighederne. Deres seneste fokus er at skabe en genanvendelig chiplet, der kombinerer RISC-V-kerner, maskinlæringsacceleration IP og standardudstyr, der findes i mange edge AI-applikationer. I skala kunne en enkelt-matrice-implementering se ud som det følgende diagram, ved at bruge den Arteris Ncore cache-kohærente interconnect og flere segmenter af Arteris FlexNoC ikke-kohærent interconnect.

billede udlånt af Arteris

En Smart Memory Controller (SMC) giver en højtydende, server-grade hukommelsesforbindelse i hukommelsesintensive applikationer. Det unavngivne "chiplet-link" kunne være UCIe, en relativt ny specifikation, der er optimeret til strammere chiplet-integration. Når nye undersystemforbindelser opstår, er tilpasning af en sektion af NoC mere overskuelig end at rive hele chip-dækkende struktur op.

Parring af RISC-V-kerner med NoC'er sænker risiko og time-to-market

Hvis det diagram ser komplekst ud, og givet, er de fleste RISC-V-applikationer måske ikke så komplekse lige nu, så overvej dette: chiplets driver allerede integrationen meget højere. Dagens avancerede RISC-V multicore-del vil være næste års værdi SoC, efterhånden som innovationen tager fart.

Arteris Ncore og Arteris FlexNoC udviklingsværktøjer udsender RTL til implementering, hvilket giver flere fordele. Fysisk NoC-estimering er ligetil i en EDA-arbejdsgang. NoC-parameterjusteringer, såsom antallet af pipeline-trin, er også et par klik væk i EDA-værktøjer. Ændringerne nævnt ovenfor for tilføjelse af en undersystemprotokol kan også let udføres. "I den høje ende får brugerne øjeblikkelig adgang til vores NoC-ekspertise," siger Schirrmeister. "I den lave ende er vores værktøjer nemme at bruge til førstegangssucces og giver en vækstvej for mere ambitiøse fremtidige projekter med komplekse forbindelser."

Parring af RISC-V-kerner med NoC'er sænker risikoen for, at endnu en IP-blok kommer ind i et design og udløser en bølge af interconnect-redesign på tværs af chippen. Det reducerer også time-to-market for komplekse SoC-designs sammenlignet med gør-det-selv sammenkoblingsstrukturer. Vi har ikke diskuteret de andre fordele ved NoC'er her, såsom båndbredde og strømstyring, men argumentet for NoC'er i RISC-V-design er stærkt, bare i betragtning af en forskelligartet protokolmix.

Besøg Arteris hjemmeside for mere information om NoC'er og andre produkter.

Del dette opslag via:

- SEO Powered Content & PR Distribution. Bliv forstærket i dag.

- PlatoData.Network Vertical Generative Ai. Styrk dig selv. Adgang her.

- PlatoAiStream. Web3 intelligens. Viden forstærket. Adgang her.

- PlatoESG. Kulstof, CleanTech, Energi, Miljø, Solenergi, Affaldshåndtering. Adgang her.

- PlatoHealth. Bioteknologiske og kliniske forsøgs intelligens. Adgang her.

- Kilde: https://semiwiki.com/ip/arteris/336086-pairing-risc-v-cores-with-nocs-ties-soc-protocols-together/

- :har

- :er

- :ikke

- :hvor

- $OP

- a

- evne

- over

- acceleration

- adgang

- gennemført

- Ifølge

- tværs

- tilføje

- justeringer

- fremskreden

- fordele

- AI

- allerede

- også

- ambitiøst

- an

- ,

- En anden

- svar

- enhver

- noget

- vises

- applikationer

- ER

- omkring

- AS

- At

- opmærksomhed

- væk

- båndbredde

- Bar

- BE

- bliver

- fordele

- Bedre

- mellem

- Bloker

- Blocks

- bus

- virksomhed

- forretningsudvikling

- men

- CAN

- tilfælde

- udfordringer

- lave om

- skiftende

- chip

- kombinerer

- råvare

- sammenlignet

- fuldføre

- komplekse

- kompleksitet

- Compute

- Tilslut

- tilslutning

- Tilslutninger

- Overvej

- betragtes

- Overvejer

- fortsætter

- kontinuerligt

- controller

- Core

- krop

- kunne

- tælle

- Oprettelse af

- kunde

- data

- definere

- definition

- Efterspørgsel

- Design

- designere

- designs

- Udvikling

- udviklingsværktøjer

- forskellige

- svært

- drøftet

- forskelligartede

- do

- kørsel

- hver

- let

- Edge

- effektivt

- emerge

- smergel

- ende

- indtastning

- Hele

- Endog

- erfaring

- ekspertise

- udvidelser

- hurtigere

- få

- felt

- kampene

- Fornavn

- flow

- Fokus

- fokuserer

- efter

- Til

- Forces

- fundet

- frank

- fra

- funktion

- fremtiden

- Gevinst

- Gates

- Give

- glimt

- bevilget

- Vækst

- Have

- hjulpet

- link.

- Høj

- Høj ydeevne

- højere

- Men

- HTTPS

- billede

- umiddelbar

- implementering

- in

- oplysninger

- Innovation

- i stedet

- integration

- sammenkobling

- sammenkobler

- ind

- IP

- IT

- ITS

- lige

- seneste

- lanceringer

- mindst

- mindre

- ligesom

- Sandsynlig

- Line (linje)

- linjer

- længere

- Se

- ligner

- UDSEENDE

- Lav

- lavere

- ledelse

- mange

- max-bredde

- Kan..

- kan være

- Hukommelse

- nævnte

- metrisk

- blande

- moderat

- Moderne

- Modifikationer

- mere

- mest

- flyttet

- meget

- flere

- skal

- Ny

- næste

- ingen

- Begreb

- nu

- nummer

- of

- on

- ONE

- åbnet

- optimeret

- or

- Andet

- vores

- output

- Tempo

- parring

- parameter

- del

- sti

- per

- ydeevne

- perifere

- periferiudstyr

- fysisk

- pick

- picks

- pipeline

- plato

- Platon Data Intelligence

- PlatoData

- Leg

- spiller

- muligheder

- Indlæg

- potentiale

- magt

- vigtigste

- Processor

- Produkter

- projekter

- protokol

- protokoller

- give

- giver

- leverer

- hurtigt

- let

- nylige

- anerkender

- redesign

- reducerer

- relativt

- forskning

- genanvendelige

- højre

- Ripple

- Rise

- Risiko

- Kør

- s

- siger

- Scale

- scenarier

- ordninger

- Sektion

- set

- Sees

- segmenter

- udvælgelse

- flere

- Shape

- deling

- Simpelt

- siden

- enkelt

- Smart

- løsninger

- Løsninger

- nogle

- sofistikeret

- specifikation

- etaper

- standard

- ligetil

- stærk

- struktur

- strukturer

- efterfølgende

- succes

- sådan

- supermagt

- Teknologier

- end

- at

- deres

- Disse

- Tredje

- denne

- tænkte

- tre

- tier

- Slips

- strammere

- tid

- til

- nutidens

- sammen

- værktøjer

- transportere

- udløsning

- UNAVNT

- opdateret

- brug

- brugere

- ved brug af

- værdi

- forskellige

- Varierende

- via

- Specifikation

- vp

- we

- Hjemmeside

- Hvad

- Hvad er

- hvornår

- vilje

- med

- Arbejde

- workflow

- zephyrnet