Det årlige International Electron Devices Meeting (IEDM) fandt sted i sidste måned. En af præsentationerne på det korte kursus var af Matthew Metz fra Intel med titlen Nye materialesystemer til videreførelse af Moores lov. I bund og grund var dette et kig på nogle af mulighederne for, hvad der kommer efter, at silicium løber tør for damp.

![]()

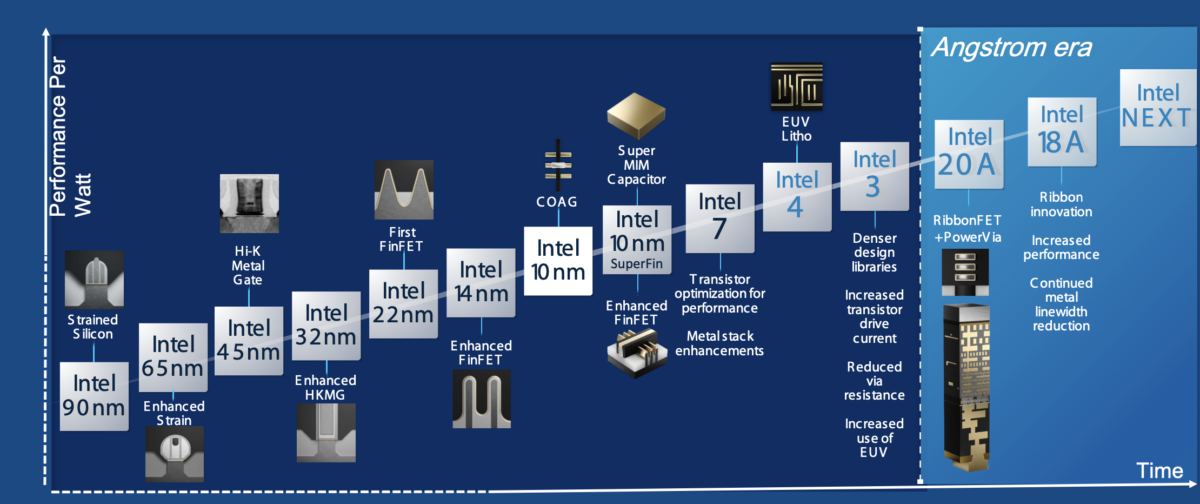

Matthew startede med et kig på, hvordan transistoren har ændret verden og især de materialeinnovationer, der har drevet Intels egen proceskøreplan gennem årtier. Tilbage ved 90nm havde vi anstrengt silicium, efterfulgt af HiK metal gate. Intel var den første til at markedsføre med FinFET (selvom den dengang kaldte det TriGate). Hos Intel 4 blev EUV litografi først introduceret.

![]()

Som du sikkert ved, laver Intel teknologisk udvikling af 5 processer på 4 år, hvilket naturligvis er aggressivt, men tilsyneladende stadig er på sporet. Intel 20A bliver den første proces med gate-all-around (GAA), som Intel kalder ribbonFET. Intel har også en aggressiv avanceret pakke-køreplan, men det vil jeg springe over, da fokus for foredraget var, hvad vi vil sætte på waferne i fremtiden, ikke hvordan vi vil sætte dem sammen.

![]()

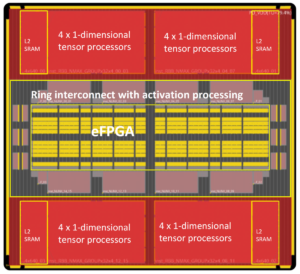

Intel er ikke alene om at gå efter gate-all-around. I løbet af de sidste par år på konferencer som IEDM har alle de store producenter og forskningsorganisationer offentliggjort en eller anden version af nanosheet gate-all-around resultater. Se tværsnittene ovenfor.

Den næste store innovation, der er planlagt, er komplementær FET eller CFET, med n-transistorer over p-transistorer. Faktisk var dette næsten temaet for dette års IEDM med mange mennesker, der annoncerede forskellige innovationer i fremstillingen af CFET for at få en 1.5X til 2X områdeskalering.

![]()

En anden innovation, som Intel forfølger (sammen med alle andre) er bagside strømforsyningsnetværk (bagside PDN) sammen med det, Intel kalder PowerVia. Disse teknologier gør det muligt at adskille signaler og strøm og ikke længere interferere med hinanden, som det historisk har været tilfældet, da al sammenkoblingen var på forsiden (vel, den eneste side indtil for nylig).

Den største udfordring er strømvæggen. Det er meget svært at få mere end 100W pr. kvadratcentimeter køling. Der er forskellige muligheder for at forbedre tingene:

- Konventionelle MOSFET-forbedringer

- Silicium germanium (SiGe) nanobånd

- Ge eller InGaAs nanobånd

- Tunnel FET'er

- Dirac FET'er (grafen og 2D)

- Negativ kapacitans NCFET

- In-memory compute med FerroTunnel Junction eller FerroFET

![]()

Der er mange attraktioner ved at lave 2D-materialer i stedet for at holde sig til 3D. Men der er store udfordringer med at finde gode materialer. Jeg er sikker på, at du har hørt om kulstof nanorør (CNT), men på trods af tiltrækningen har der ikke været nogen reel fremgang i udfordringen med at fremstille disse pålideligt i ti år. Grafen er 2D, men har ingen båndgab, hvilket gør bygning af switches til en udfordring. Fosforen er flygtigt ved høj temperatur, hvilket gør fremstilling af en komplet transistor umulig.

![]()

Den mest attraktive løsning synes at være udvikling af overgangsmetal dichalcogenider eller TMD. Jeg indrømmer, at det var første gang, jeg havde hørt om disse, i det mindste under dette navn. Det er en af de mere lovende tilgange ved at bruge 2D-materialer. TMD er et enkelt monolag, der giver god gate-kontrol, så der er lavere effekt. De har bedre mobilitet end silicium, så god ydeevne. Også et stort båndgab så begrænset kilde-dræn-tunneling.

Matthew gik ind i ret mange detaljer om udfordringerne og løfterne ved at fremstille TMD 2-lags transistorer, især voksende 2D enkeltlags transistorer, og hvordan man kontakter dem. For kontanter til n-transistoren synes de mest attraktive materialer at være antimon (Sb) og vismut (Bi). For p-transistoren, ruthenium (Ru).

![]()

Det sidste afsnit var et kig på nedskalering af strømkrav og avanceret switching, især de magneto-elektriske spin-orbital (MESO) enheder. Omskiftning kan foretages ved omkring 0.1V med tilsvarende effektreduktion.

Matthews konklusion er, at det arbejde, der foregår hos Intel med TMD, viser lovende for fortsat CMOS-skalering, og MESO-enheder har meget løfte om drastisk strømreduktion. Men dette er forholdsvis tidlig forskning, og der er stadig meget arbejde at gøre for at gøre en af disse teknologier til en praktisk realitet.

Læs også:

2024 Big Race er TSMC N2 og Intel 18A

IEDM Buzz – Intel forhåndsviser ny vertikal transistor-skaleringsinnovation

Intel indleder en ny æra med avanceret emballage med glasunderlag

Del dette opslag via:

- SEO Powered Content & PR Distribution. Bliv forstærket i dag.

- PlatoData.Network Vertical Generative Ai. Styrk dig selv. Adgang her.

- PlatoAiStream. Web3 intelligens. Viden forstærket. Adgang her.

- PlatoESG. Kulstof, CleanTech, Energi, Miljø, Solenergi, Affaldshåndtering. Adgang her.

- PlatoHealth. Bioteknologiske og kliniske forsøgs intelligens. Adgang her.

- Kilde: https://semiwiki.com/semiconductor-manufacturers/340336-iedm-what-comes-after-silicon/

- :har

- :er

- :ikke

- 01

- 1

- 14

- 15 %

- 2024

- 27

- 29

- 2D

- 2D-materialer

- 30

- 3d

- 40

- 50

- 53

- 58

- 8

- a

- Om

- over

- fremme

- fremskreden

- Efter

- aggressive

- Alle

- tillade

- næsten

- alene

- sammen

- også

- Skønt

- am

- an

- ,

- Annoncerer

- årligt

- tilgange

- ER

- OMRÅDE

- omkring

- AS

- At

- attraktion

- attraktioner

- attraktivt

- tilbage

- BE

- været

- Bedre

- Big

- Største

- Bygning

- men

- by

- kaldet

- Opkald

- CAN

- kulstof

- nanorør af kulstof

- tilfælde

- udfordre

- udfordringer

- ændret

- kommer

- forholdsvis

- komplementære

- fuldføre

- Compute

- konklusion

- konferencer

- kontakt

- fortsatte

- Tilsvarende

- Par

- kursus

- Cross

- årtier

- levering

- Trods

- detail

- Udvikling

- Enheder

- svært

- gør

- færdig

- ned

- drevet

- hver

- Tidligt

- enten

- andet

- Era

- Essensen

- alle

- Faktisk

- FET

- finde

- Fornavn

- første gang

- Fokus

- efterfulgt

- Til

- forsiden

- fremtiden

- gate

- få

- Give

- glas

- gå

- godt

- Graphene

- Dyrkning

- havde

- Have

- hørt

- Høj

- historisk

- Hvordan

- How To

- HTTPS

- i

- umuligt

- Forbedre

- in

- Innovation

- innovationer

- i stedet

- Intel

- blande

- internationalt

- ind

- introduceret

- IT

- Kend

- stor

- Efternavn

- Lov

- lag

- mindst

- ligesom

- Limited

- længere

- Se

- Lot

- lavere

- større

- lave

- Making

- Producenter

- Produktion

- mange

- mange mennesker

- Marked

- materialer

- matthew

- max-bredde

- møde

- metal

- mobilitet

- Måned

- mere

- mest

- navn

- netværk

- Ny

- næste

- ingen

- of

- on

- ONE

- kun

- or

- organisationer

- Andet

- ud

- i løbet af

- egen

- emballage

- særlig

- Mennesker

- per

- ydeevne

- Place

- planlagt

- plato

- Platon Data Intelligence

- PlatoData

- muligheder

- Indlæg

- magt

- Praktisk

- Præsentationer

- Previews

- sandsynligvis

- behandle

- Processer

- løfte

- Promises

- lovende

- offentliggjort

- Fortsat

- sætte

- helt

- Løb

- Læs

- ægte

- Reality

- for nylig

- reduktion

- Krav

- forskning

- Resultater

- køreplan

- RU

- løber

- skalering

- Skærm

- Sektion

- sektioner

- se

- synes

- synes

- Kort

- shot

- Shows

- side

- signaler

- Silicon

- siden

- enkelt

- So

- løsninger

- nogle

- firkant

- påbegyndt

- Damp

- stikning

- Stadig

- sikker

- Systemer

- Tal

- Teknologier

- Teknologier

- Teknologiudvikling

- ti

- end

- at

- Fremtiden

- verdenen

- Them

- tema

- derefter

- Der.

- Disse

- de

- ting

- denne

- tid

- titlen

- til

- sammen

- tog

- spor

- overgang

- tsmc

- under

- indtil

- betjentene

- ved brug af

- forskellige

- udgave

- lodret

- meget

- via

- flygtige

- Væglampe

- var

- we

- GODT

- gik

- Hvad

- hvornår

- som

- vilje

- med

- Arbejde

- world

- år

- dig

- zephyrnet