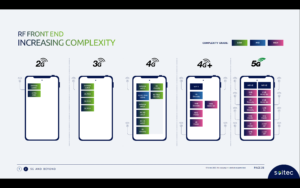

I marchen til mere dygtige, hurtigere, mindre og lavere strømsystemer gav Moores lov software en gratis tur i over 30 år eller deromkring udelukkende på halvlederprocesudvikling. Compute-hardware leverede forbedret ydeevne/areal/effektmålinger hvert år, hvilket tillod software at udvide i kompleksitet og levere mere kapacitet uden ulemper. Så blev de lette sejre mindre lette. Mere avancerede processer fortsatte med at levere højere gate-antal pr. arealenhed, men gevinster i ydeevne og effekt begyndte at flade ud. Siden vores forventninger til innovation ikke stoppede, er fremskridt i hardwarearkitekturen blevet vigtigere for at tage fat.

Drivere til at øge core-count

Et tidligt skridt i denne retning brugte multi-core CPU'er til at accelerere den samlede gennemstrømning ved at tråde eller virtualisere en blanding af samtidige opgaver på tværs af kerner, hvilket reducerede strømmen efter behov ved at køre i tomgang eller slukke for inaktive kerner. Multi-core er standard i dag, og en tendens i mange-kerne (endnu flere CPU'er på en chip) er allerede tydelig i server-instansmuligheder, der er tilgængelige i cloud-platforme fra AWS, Azure, Alibaba og andre.

Multi-/many-core arkitekturer er et skridt fremad, men parallelitet gennem CPU-klynger er grovkornet og har sine egne ydeevne- og effektgrænser, takket være Amdahls lov. Arkitekturer blev mere heterogene og tilføjede acceleratorer til billede, lyd og andre specialiserede behov. AI-acceleratorer har også skubbet finkornet parallelisme og flyttet til systoliske arrays og andre domænespecifikke teknikker. Hvilket fungerede ret godt, indtil ChatGPT dukkede op med 175 milliarder parametre med GPT-3, der udviklede sig til GPT-4 med 100 billioner parametre – størrelsesordener mere komplekse end nutidens AI-systemer – hvilket tvinger endnu mere specialiserede accelerationsfunktioner i AI-acceleratorer.

På en anden front integreres multisensorsystemer i bilapplikationer nu i enkelte SoC'er for forbedret miljøbevidsthed og forbedret PPA. Her afhænger nye niveauer af autonomi i bilindustrien af sammensmeltning af input fra flere sensortyper inden for en enkelt enhed, i undersystemer, der replikerer med 2X, 4X eller 8X.

Ifølge Michał Siwinski (CMO hos Arteris) tyder stikprøver over en måneds diskussioner med flere designteams på tværs af en bred vifte af applikationer, at disse teams aktivt henvender sig til højere kernetal for at nå kapacitets-, ydeevne- og kraftmål. Han fortæller mig, at de også ser denne tendens accelerere. Procesfremskridt hjælper stadig med SoC-gatetællinger, men ansvaret for at opfylde ydeevne- og magtmål er nu fast i hænderne på arkitekterne.

Flere kerner, mere sammenkobling

Flere kerner på en chip indebærer flere dataforbindelser mellem disse kerner. Inden for en accelerator mellem nabobehandlingselementer, til lokal cache, til acceleratorer til sparsom matrix og anden specialiseret håndtering. Tilføj hierarkisk forbindelse mellem acceleratorbrikker og busser på systemniveau. Tilføj tilslutning til on-chip vægtlagring, dekompression, udsendelse, indsamling og re-komprimering. Tilføj HBM-forbindelse til fungerende cache. Tilføj en fusionsmotor om nødvendigt.

Den CPU-baserede kontrolklynge skal oprette forbindelse til hvert af disse replikerede undersystemer og til alle de sædvanlige funktioner - codecs, hukommelsesstyring, sikkerhedsø og root of trust, hvis det er relevant, UCIe, hvis det er en multi-chiplet-implementering, PCIe til I/O med høj båndbredde , og Ethernet eller fiber til netværk.

Det er en masse sammenkobling med direkte konsekvenser for produkters salgbarhed. I processer under 16nm bidrager NoC-infrastruktur nu med 10-12% i areal. Endnu vigtigere, som kommunikationsmotorvejen mellem kerner, kan den have betydelig indflydelse på ydeevne og kraft. Der er reel fare for, at en suboptimal implementering vil sløse med forventet arkitekturydeevne og effektgevinster, eller endnu værre, resultere i adskillige re-design-loops, der konvergerer. Men at finde en god implementering i en kompleks SoC-gulvplan afhænger stadig af langsomme trial-and-error-optimeringer i allerede stramme designplaner. Vi er nødt til at tage springet til fysisk bevidst NoC-design, for at garantere fuld ydeevne og kraftunderstøttelse fra komplekse NoC-hierarkier, og vi er nødt til at gøre disse optimeringer hurtigere.

Fysisk bevidste NoC-design holder Moores lov på sporet

Moores lov er måske ikke død, men fremskridt i ydeevne og kraft i dag kommer fra arkitektur og NoC-sammenkobling snarere end fra processen. Arkitektur skubber flere acceleratorkerner, flere acceleratorer inden for acceleratorer og mere delsystemreplikering på chip. Alt sammen øger kompleksiteten af on-chip interconnect. Efterhånden som design øger kerneantallet og går over til procesgeometrier ved 16nm og derunder, kan de talrige NoC-forbindelser, der spænder over SoC'en og dets undersystemer, kun understøtte det fulde potentiale af disse komplekse designs, hvis de implementeres optimalt mod fysiske begrænsninger og tidsbegrænsninger - gennem fysisk bevidste netværk på chip design.

Hvis du også bekymrer dig om disse tendenser, vil du måske lære mere om Arteris FlexNoC 5 IP-teknologi HER.

Del dette opslag via:

- SEO Powered Content & PR Distribution. Bliv forstærket i dag.

- Platoblokkæde. Web3 Metaverse Intelligence. Viden forstærket. Adgang her.

- Kilde: https://semiwiki.com/artificial-intelligence/326727-interconnect-under-the-spotlight-as-core-counts-accelerate/

- :er

- $OP

- 100

- a

- Om

- fremskynde

- accelererende

- acceleration

- accelerator

- acceleratorer

- tværs

- aktivt

- fremskreden

- fremskridt

- mod

- AI

- AI-systemer

- Alibaba

- Alle

- tillade

- allerede

- ,

- dukkede

- applikationer

- passende

- arkitektur

- ER

- OMRÅDE

- AS

- At

- lyd

- automotive

- til rådighed

- bevidsthed

- AWS

- Azure

- båndbredde

- BE

- bliver

- jf. nedenstående

- mellem

- Billion

- udsende

- Busser

- by

- cache

- CAN

- stand

- ChatGPT

- chip

- Cloud

- Cluster

- CMO

- Kom

- Kommunikation

- komplekse

- kompleksitet

- Compute

- konkurrent

- Tilslut

- Tilslutninger

- Connectivity

- Konsekvenser

- begrænsninger

- fortsatte

- kontrol

- Converge

- Core

- CPU

- FARE

- data

- døde

- levere

- leveret

- afhænger

- Design

- designs

- enhed

- forskellige

- direkte

- retning

- diskussioner

- ned

- ulemper

- hver

- Tidligt

- elementer

- Engine (Motor)

- Miljø

- Endog

- Hver

- evolution

- udviklende

- Udvid

- forventninger

- forventet

- hurtigere

- Funktionalitet

- finde

- fast

- Til

- Videresend

- Gratis

- fra

- forsiden

- fuld

- funktioner

- fusion

- gevinster

- Mål

- godt

- garanti

- Håndtering

- hænder

- Hardware

- Have

- hjælpe

- link.

- Høj

- højere

- Hovedvej

- HTTPS

- billede

- KIMOs Succeshistorier

- implementering

- implementeret

- vigtigt

- forbedret

- in

- inaktive

- Forøg

- stigende

- Infrastruktur

- Innovation

- instans

- Integration

- IP

- ø

- IT

- ITS

- hoppe

- Lov

- LÆR

- Niveau

- niveauer

- grænser

- lokale

- Lot

- lave

- ledelse

- Marts

- Matrix

- max-bredde

- Mød

- møde

- Hukommelse

- Metrics

- måske

- Måned

- mere

- bevæge sig

- flytning

- flere

- Behov

- behov

- behov

- netværk

- netværk

- Ny

- talrige

- of

- on

- Indstillinger

- ordrer

- Andet

- Andre

- egen

- parametre

- ydeevne

- fysisk

- Fysisk

- Platforme

- plato

- Platon Data Intelligence

- PlatoData

- Indlæg

- potentiale

- magt

- strømforsyning

- smuk

- behandle

- Processer

- forarbejdning

- Produkt

- rent

- skubbet

- Pushing

- rækkevidde

- hellere

- ægte

- reducere

- replikeres

- replikation

- ansvar

- resultere

- Ride

- rod

- Sikkerhed

- halvleder

- signifikant

- siden

- enkelt

- slæk

- langsom

- mindre

- So

- Software

- sparsom matrix

- specialiserede

- Spotlight

- standard

- påbegyndt

- Trin

- Stadig

- Stands

- opbevaring

- foreslår

- support

- systemet

- Systemer

- opgaver

- hold

- teknikker

- Teknologier

- fortæller

- at

- Disse

- Gennem

- kapacitet

- timing

- til

- i dag

- nutidens

- I alt

- Trend

- Tendenser

- trillion

- Stol

- Drejning

- typer

- under

- enhed

- via

- vægt

- GODT

- som

- bred

- Bred rækkevidde

- vilje

- Vinder

- med

- inden for

- arbejder

- år

- år

- zephyrnet