I integreret kredsløbsterminologi er et fald det spændingsfald, der sker i et kredsløb. Dette er et velkendt fænomen og kan ske på grund af følgende årsager. Strømforsyningen falder under det driftsområde, som en chip er designet til, hvilket resulterer i et fald. Der trækkes mere strøm af de ledende elementer, end de er designet til, hvilket resulterer i et fald. Nogle gange kan signalinterferens eller støj på strømforsyningen også forårsage spændingsudsving, hvilket resulterer i et fald.

Nedhæng kan påvirke driften af et kredsløb. Reduceret ydeevne af chippen, hvilket fører til længere behandlingstider er en sådan påvirkning. Men det følgende er nogle af de mere alvorlige og/eller katastrofale konsekvenser. Chippen kunne trække mere strøm for at opretholde ydelsesniveauet, hvilket fører til øget strømforbrug og varmeafledning. Dette kan føre til reduceret levetid af chippen og i alvorlige tilfælde en fuldstændig svigt af chippen på grund af variationer i opsætning og hold. Droops kan også forårsage datakorruption eller fejl i outputtet. Dette er et meget alvorligt problem for applikationer, der afhænger af chippens nøjagtighed og pålidelighed.

Fænomenet droops tages naturligvis alvorligt i betragtning ved design af chips og systemer. De mest almindelige metoder til at afbøde fald er strømforsyningsafkobling, spændingsregulering, kredsløbsoptimering og strømstyring på systemniveau. Betingelserne og det driftsmiljø, som chippen vil fungere i, overvejes nøje, når der designes løsninger, der begrænser fald.

Nutidens problemer

Efterhånden som SoC'er bliver mere komplekse, kan hængeproblemer også blive ret komplekse. En SoC's design skal optimeres til ydeevne, effekt, pris, formfaktor osv. foruden at optimere til at reducere fald. Nogle gange kan disse optimeringsmål konkurrere med hinanden og løbe i modstrid, og der skal foretages afvejninger. For eksempel kan SoC-arkitekter hæve driftsspændingen og tilføje margen for at omgå lokalt og globalt fald, men denne stigning øger effekten kvadratisk. Alternativt kan designere få deres urgenerering til at tilpasse sig til at falde, hvilket gør ydeevnen til en funktion af urgenereringens skiftetid.

Som følge heraf er store SoC'er i datacenterets computer- og AI-plads særligt modtagelige for fald. Kundernes arbejdsbyrder er meget forskelligartede og dynamiske, hvilket fører til betydelige udsving i skifteaktivitet og strømtræk. Selvfølgelig har systemer ikke råd til at lade hængende problemer forsvinde. Den potentielle erstatningsansvar fra unøjagtige output eller katastrofale fejl på en chip er for høj for nutidens systemer og applikationer.

Lokaliserede Droop-problemer

Applikationsspecifikke acceleratorer bruges i vid udstrækning sammen med processorer til generelle formål for at levere den ydeevne og strømeffektivitet, der kræves i nutidens krævende computermiljøer. Men disse acceleratorer samt det stigende antal kerner og den asymmetriske karakter af arbejdsbelastninger øger risikoen for lokale spændingsfald. Disse lokale spændingsfald er et resultat af pludselig stigning i koblingsaktivitet og kan forårsage forbigående fejl og potentielle mission-mode fejl.

Når lokaliseret fald opstår, kan påvirkningen afbødes gennem dynamisk frekvensskalering. Dette opnås ved at justere timingen af et kredsløb ved hjælp af et programmerbart ur. Et programmerbart ur gør det muligt at justere clockfrekvensen og timingen dynamisk baseret på kredsløbets aktuelle driftsbetingelser.

Movellus gør det nemt at adressere lokaliserede fald

Movellus, en førende digital system-IP-udbyder, har udviklet Aeonic Generate-serien af produkter til at adressere lokaliserede fald. Movellus Aeonic-porteføljen tilbyder adaptive clocking-løsninger, der leverer hurtig droop-respons. Porteføljen inkluderer det adaptive clocking-system. Byggeklodserne er bygget med syntetiserbar Verilog, hvilket gør dem iboende fleksible. Løsningerne er konfigurerbare, scanbare og proces-portable til en lang række avancerede SoC-applikationer.

Aeonic Generate-familien af produkter er også væsentligt mindre end traditionelle analoge løsninger. Som et resultat kan designere instansiere IP'en med den krævede granularitet uden nogen væsentlig indvirkning på området. Derudover, efterhånden som designs flytter til finere procesgeometrier, fortsætter Aeonic Generate-området med at skalere, hvilket gør det til en ideel løsning til fremtidige designs.

Et par brugssager

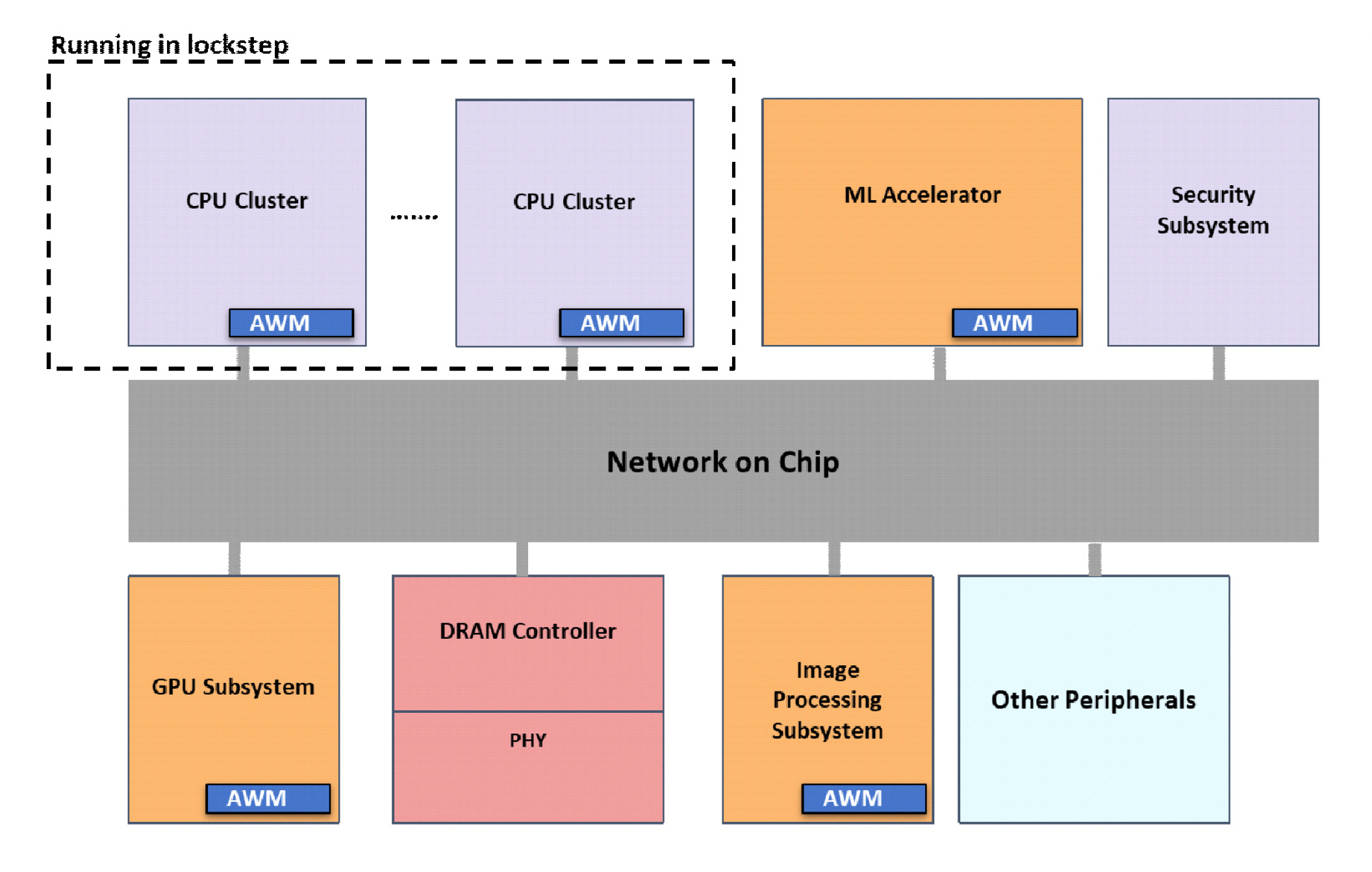

Følgende figur fra Movellus viser et eksempel på arkitektur af en ADAS-processor med Aeonic Generate AWM-platformen til lokaliseret droop-understøttelse. En arkitekt vil parre et AWM-modul med en applikationsspecifik underblok eller accelerator for at reagere på arbejdsbelastningsdrevne lokaliserede fald inden for fem clock-cyklusser med fejlfrie og hurtige frekvensskift. Denne tilgang giver en pålidelig og effektiv løsning til at tackle udfordringerne med lokaliserede fald på ADAS-, 5G- og datacenternetværksmarkederne.

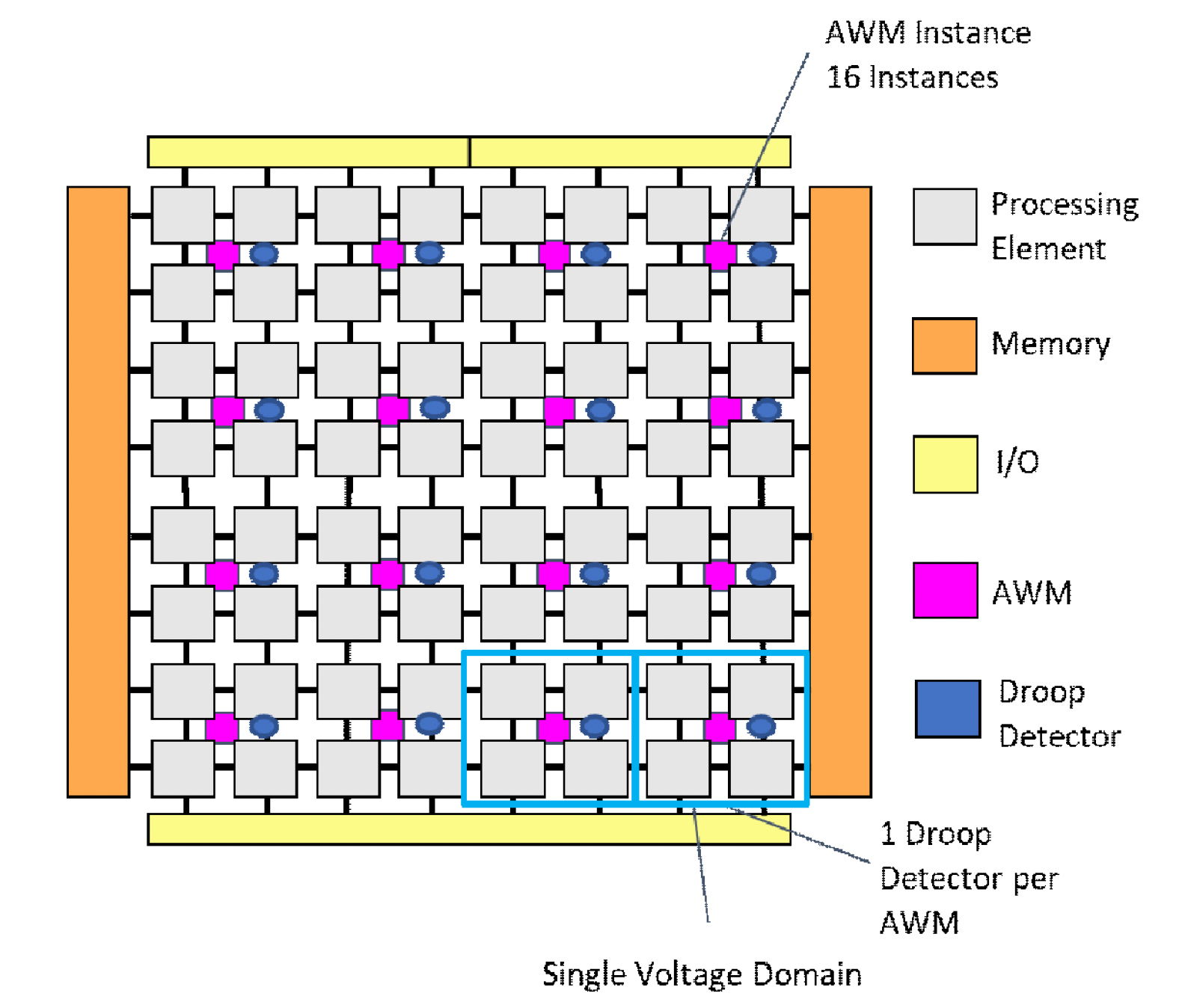

Følgende figur fra Movellus viser et eksempel på arkitektur af et hav af processor SoC med Aeonic Generate til lokaliseret droop-understøttelse. En arkitekt ville parre et Aeonic Generate AWM-modul med en droop-detektor til processorklyngen og tilhørende spændingsdomæne for hurtigt at reagere på arbejdsbelastningsdrevne lokaliserede droops. Dette giver designere mulighed for at levere lokaliseret og uafhængig droop-respons uden at ændre ydeevnen af tilstødende processorklynger.

Resumé

Lokaliserede spændingsfald kan forekomme i heterogene SoC'er, der indeholder applikationsspecifikke acceleratorer. Disse fald kan føre til timing-fejl, forbigående fejl og mission-mode-fejl i ADAS, datacenternetværk og 5G-applikationer. Systemarkitekter kan implementere adaptiv clocking for at reagere på disse fald og afbøde påvirkningen.

Movellus™ Aeonic Generate Adaptive Workload Module (AWM)-familien af højtydende urgenererings-IP-produkter er en del af Aeonic Intelligent Clock Network™-arkitekturen. For mere information, se Movellus' Aeonic Generate™ AWM-side.

Læs også:

Fordele ved synkrone urdomæner i stor skala i AI-chipdesign

Det er nu tid til Smart Clock Networks

Ydeevne, kraft og område (PPA) fordele gennem intelligente urnetværk

Del dette opslag via:- SEO Powered Content & PR Distribution. Bliv forstærket i dag.

- Platoblokkæde. Web3 Metaverse Intelligence. Viden forstærket. Adgang her.

- Kilde: https://semiwiki.com/ip/326488-adaptive-clock-technology-for-real-time-droop-response/

- :er

- 5G

- a

- accelerator

- acceleratorer

- nøjagtighed

- opnået

- aktivitet

- tilpasse

- ADA'er

- Desuden

- Derudover

- adresse

- adressering

- Justeret

- fremskreden

- AI

- tillader

- ,

- applikationer

- tilgang

- arkitektur

- ER

- OMRÅDE

- AS

- forbundet

- At

- baseret

- BE

- bliver

- jf. nedenstående

- fordele

- Bloker

- Blocks

- Bygning

- bygget

- by

- CAN

- Kan få

- kan ikke

- omhyggeligt

- tilfælde

- katastrofale

- Årsag

- center

- udfordringer

- chip

- Chips

- ur

- Cluster

- Fælles

- konkurrere

- fuldføre

- komplekse

- Compute

- computing

- betingelser

- overvejelse

- betragtes

- forbrug

- fortsætter

- Korruption

- Koste

- kunne

- Counter

- Par

- kursus

- Nuværende

- kunde

- cykler

- data

- Data Center

- Datacenter

- dag

- levere

- krævende

- Design

- konstrueret

- designere

- designe

- designs

- udviklet

- digital

- distribueret

- forskelligartede

- domæne

- Domæner

- trukket

- Drop

- Drops

- dynamisk

- dynamisk

- hver

- effektivitet

- effektiv

- elementer

- Miljø

- miljøer

- fejl

- etc.

- eksempel

- Manglende

- Falls

- familie

- Figur

- fleksibel

- udsving

- efter

- Til

- formular

- Frekvens

- fra

- funktion

- fremtiden

- generelle formål

- generere

- generation

- få

- Global

- Go

- Mål

- ske

- sker

- Have

- Høj

- Høj ydeevne

- hold

- HTTPS

- ideal

- KIMOs Succeshistorier

- Påvirkninger

- gennemføre

- in

- forkert

- omfatter

- Forøg

- øget

- Stigninger

- stigende

- uafhængig

- oplysninger

- integreret

- integration

- Intelligent

- uløseligt

- IP

- spørgsmål

- spørgsmål

- IT

- stor

- storstilet

- føre

- førende

- Niveau

- ansvar

- Livet

- lokale

- længere

- lavet

- vedligeholde

- maerker

- Making

- ledelse

- Margin

- Markeder

- max-bredde

- metoder

- afbøde

- formildende

- afbødning

- modul

- Moduler

- mere

- mest

- bevæge sig

- Natur

- behov

- netværk

- netværk

- Støj

- især

- nummer

- of

- Tilbud

- on

- ONE

- drift

- Produktion

- optimering

- optimeret

- optimering

- Andet

- output

- del

- ydeevne

- udfører

- fænomen

- perron

- plato

- Platon Data Intelligence

- PlatoData

- portefølje

- Indlæg

- potentiale

- magt

- Strømforsyning

- behandle

- forarbejdning

- Processor

- processorer

- Produkter

- udbyder

- giver

- rejse

- rækkevidde

- hurtige

- hurtigt

- Læs

- realtid

- årsager

- Reduceret

- Regulering

- pålidelighed

- pålidelig

- påkrævet

- Svar

- svar

- resultere

- resulterer

- Rise

- Risiko

- Kør

- Scale

- skalering

- HAV

- alvorlig

- setup

- svær

- Skift

- Shows

- Signal

- signifikant

- betydeligt

- mindre

- Smart

- løsninger

- Løsninger

- nogle

- Space

- sådan

- pludselige

- forsyne

- support

- modtagelig

- systemet

- Systemer

- Tandem

- Teknologier

- terminologi

- at

- Området

- deres

- Them

- Disse

- Gennem

- tid

- gange

- timing

- til

- nutidens

- også

- traditionelle

- brug

- meget forskelligartet

- via

- Spænding

- GODT

- Kendt

- som

- bred

- Bred rækkevidde

- bredt

- vilje

- med

- inden for

- uden

- ville

- zephyrnet