IEDM 2023-এ, Naoto Horiguchi CFETs এবং মিডল অফ লাইন ইন্টিগ্রেশনের উপর উপস্থাপন করেছে। আমি এই কাজ সম্পর্কে নাওটোর সাথে কথা বলার সুযোগ পেয়েছি এবং এই লেখাটি IEDM এ তার উপস্থাপনা এবং আমাদের ফলো আপ আলোচনার উপর ভিত্তি করে। আমি সর্বদা নাওটোর সাথে কথা বলা উপভোগ করি, তিনি যুক্তি প্রযুক্তির বিকাশের অন্যতম নেতা, প্রযুক্তিটি সহজে বোঝার উপায়ে ব্যাখ্যা করেন এবং প্রতিক্রিয়াশীল এবং কাজ করা সহজ।

কেন আমরা CFETs প্রয়োজন

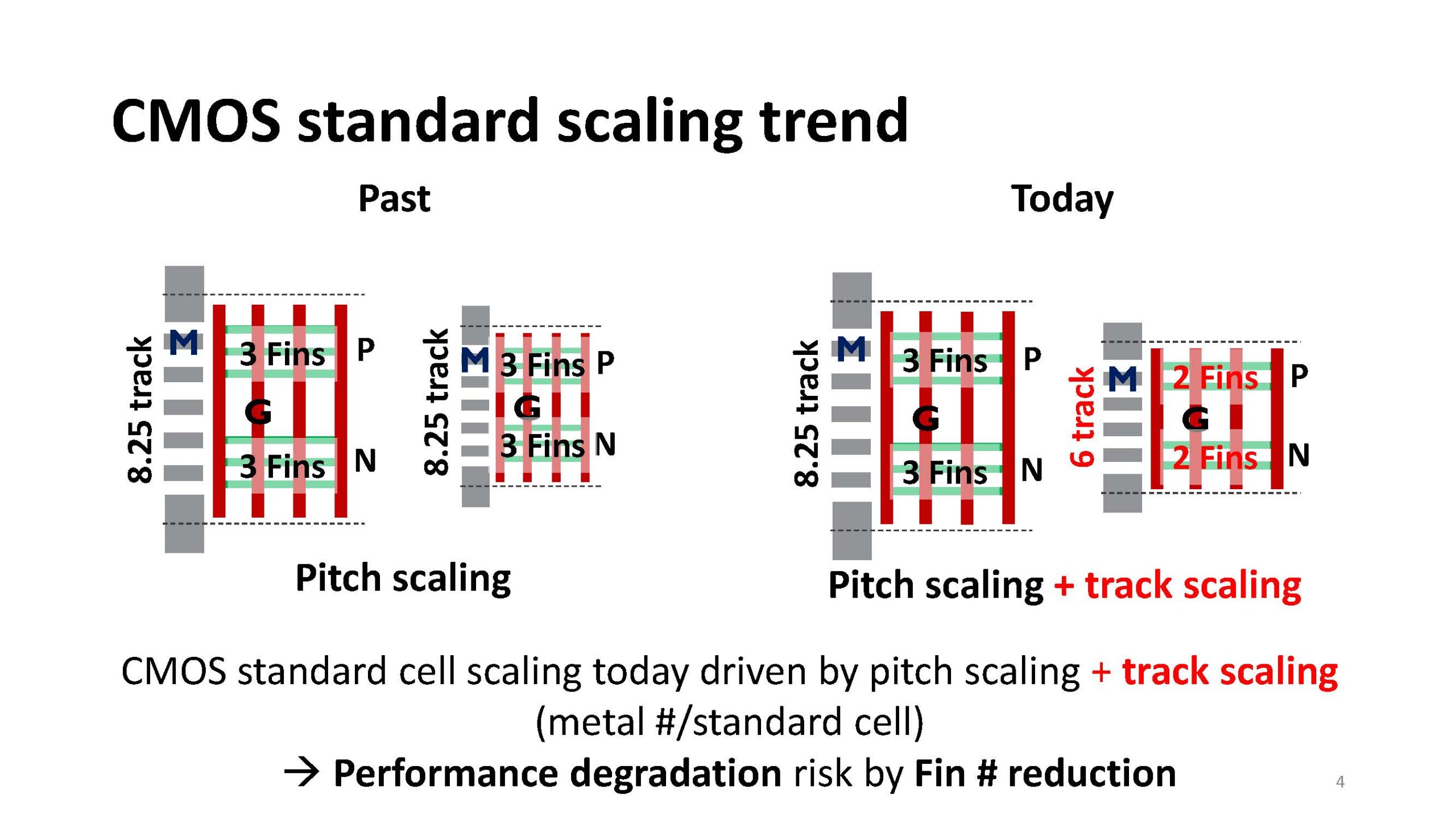

যেহেতু CMOS স্কেলিং বিশুদ্ধভাবে পিচ ভিত্তিক স্কেলিং থেকে পিচ প্লাস ট্র্যাক-ভিত্তিক স্কেলিংয়ে রূপান্তরিত হয়েছে, তাই ফিন জনসংখ্যা প্রয়োজনীয় হয়ে উঠেছে, চিত্র 1 দেখুন। আপনি যতবার পাখনার সংখ্যা কম করেন ততবার কর্মক্ষমতা হ্রাস পায়।

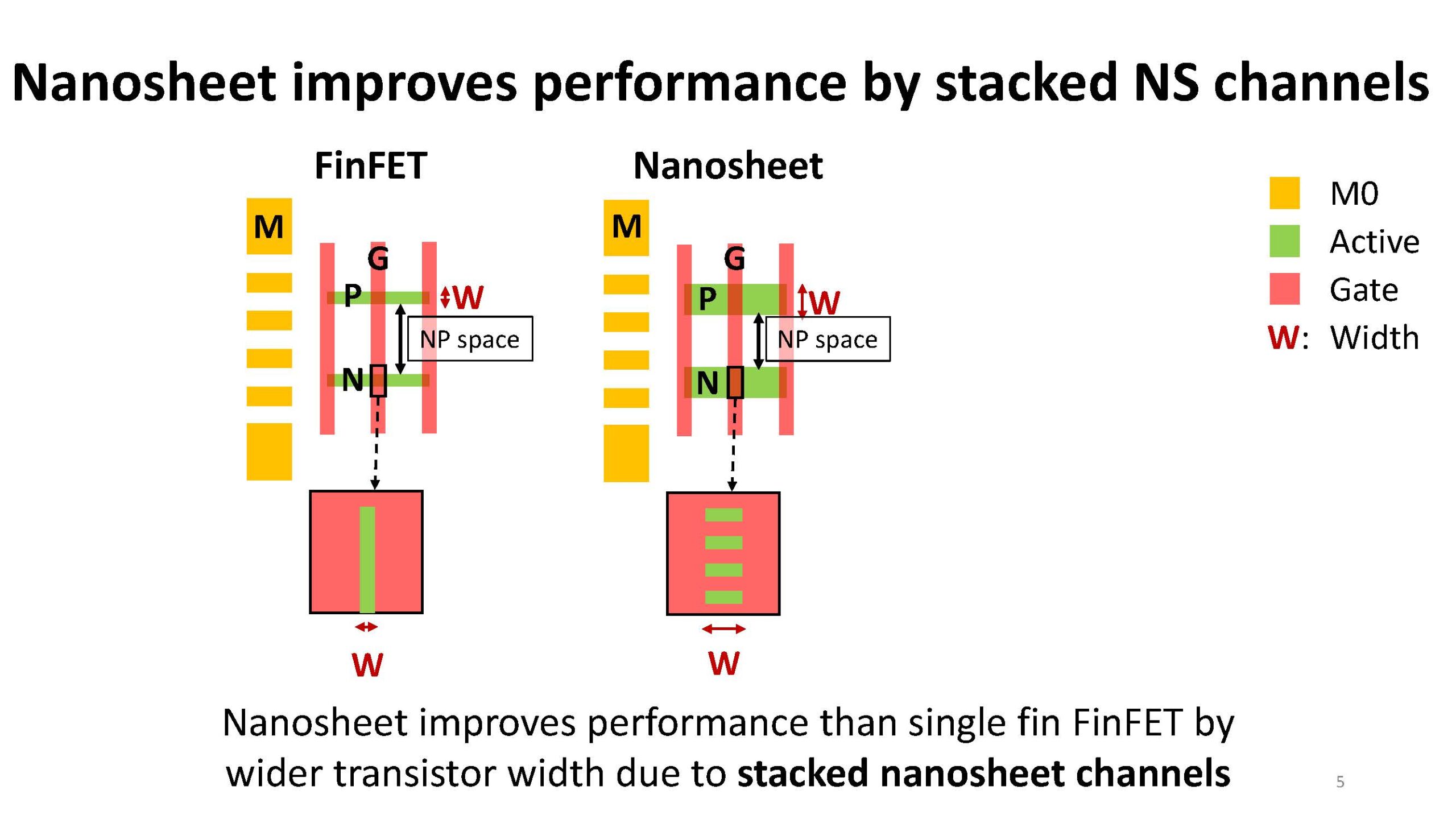

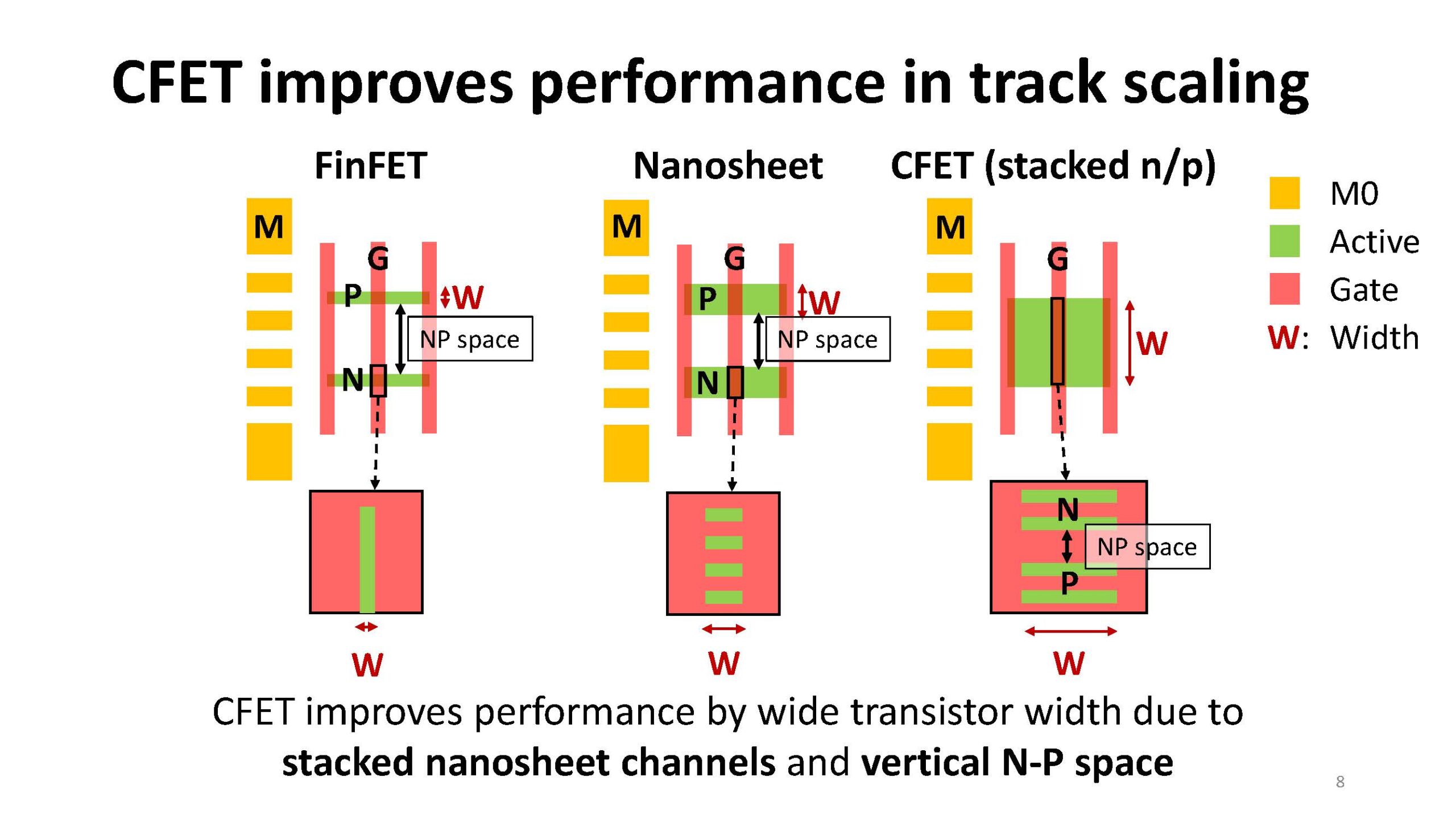

FinFEts থেকে স্ট্যাক করা H এ সরানোর মাধ্যমেঅরাইজন্টাল ন্যানোশিট (HNS) কর্মক্ষমতা আরও বৃহত্তর ন্যানোশিট স্ট্যাক এবং একাধিক ন্যানোশিট উল্লম্বভাবে স্ট্যাকিং দ্বারা উন্নত/পুনরুদ্ধার করা যেতে পারে, চিত্র 2 দেখুন।

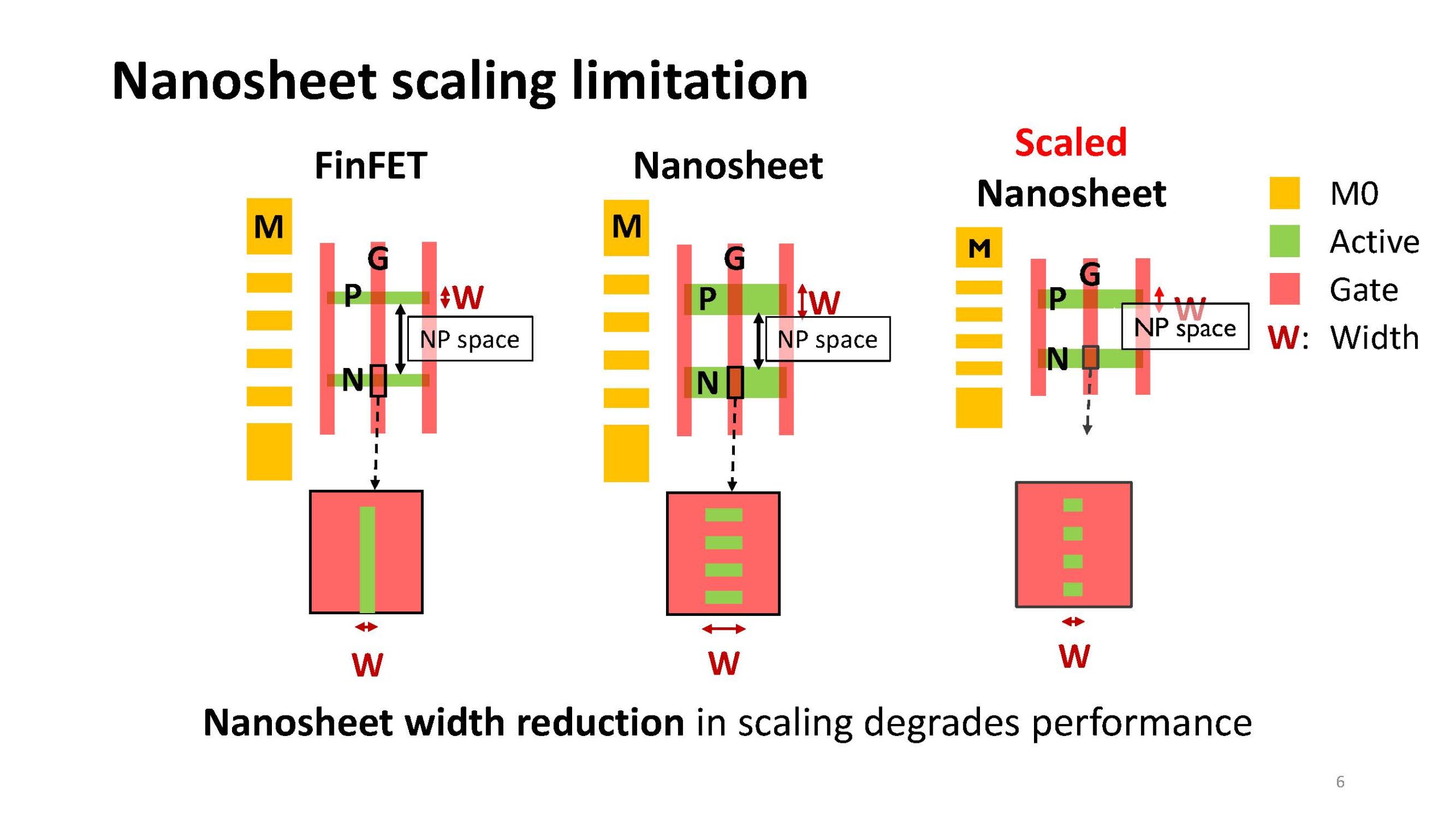

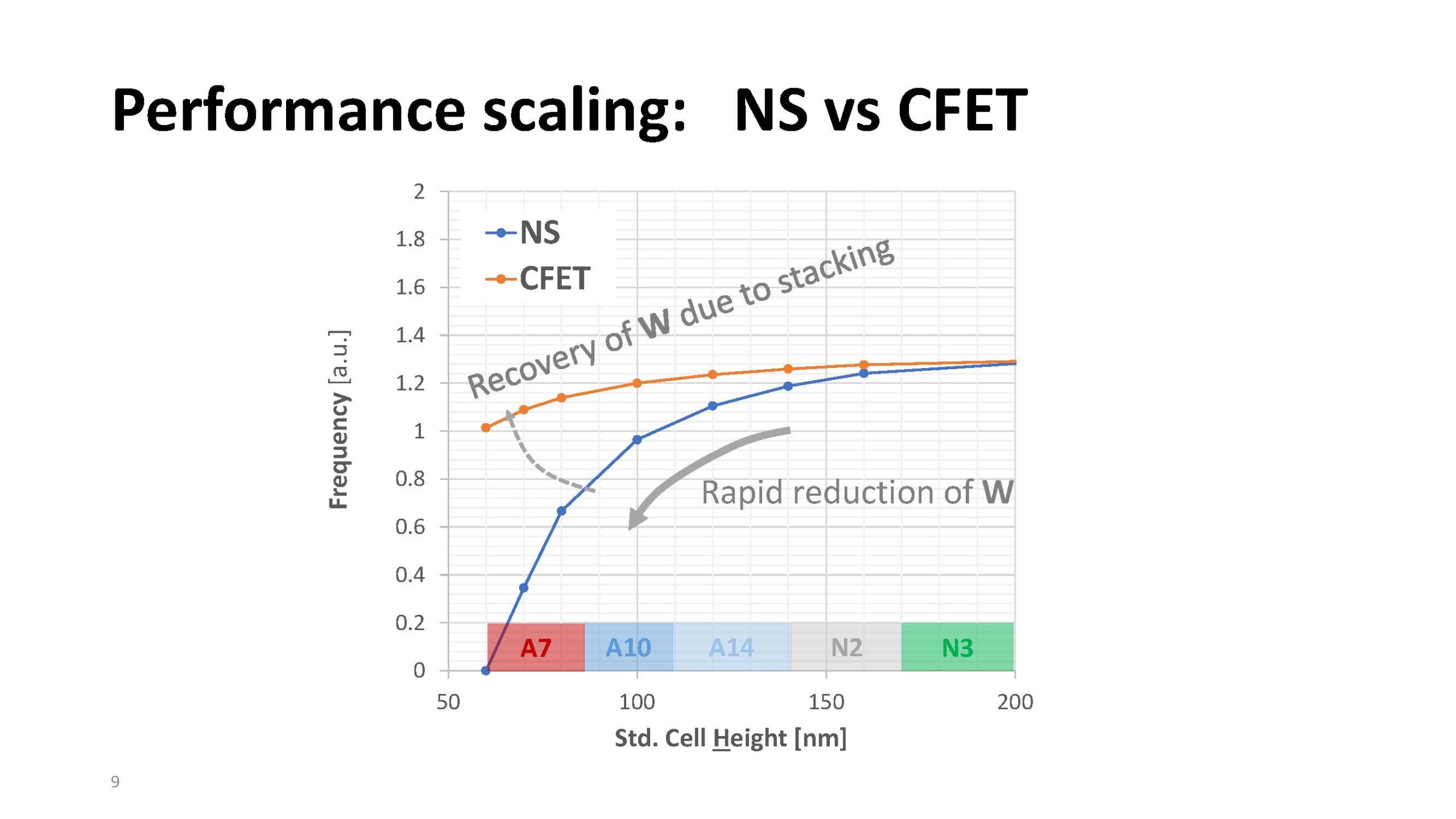

কিন্তু আমরা যেমন FinFET-এর সাথে দেখেছি ন্যানোশিট স্কেলিং শেষ পর্যন্ত কর্মক্ষমতা হ্রাস করে, চিত্র 3 দেখুন।

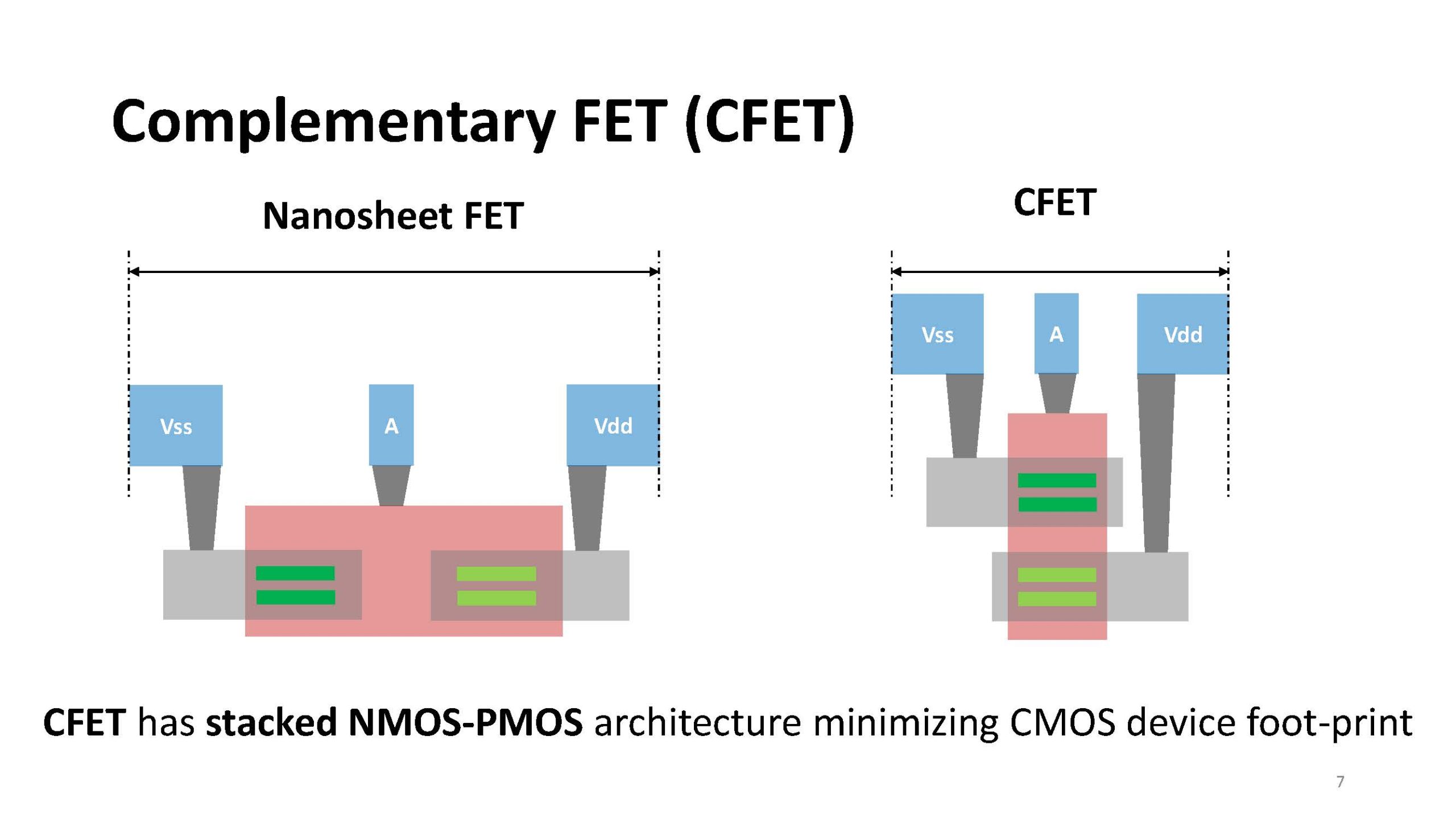

CFETs (পরিপূরক FET) nFET এবং pFET স্ট্যাক করে, চিত্র 4 দেখুন।

CFETগুলি আবার স্কেলিং সীমাবদ্ধতাগুলি পুনরায় সেট করে কারণ nFET এবং pFET স্ট্যাক করা হয় এবং ডিভাইসগুলির মধ্যে np ব্যবধান অনুভূমিক পরিবর্তে উল্লম্ব হয়ে যায়, এটি আরও বিস্তৃত শীটগুলিকে সক্ষম করে, চিত্র 5 দেখুন৷

চিত্র 6 এইচএনএস এবং সিএফইটি পারফরম্যান্সের তুলনা উপস্থাপন করে বনাম সেলের উচ্চতা সিএফইটি সুবিধা হাইলাইট করে।

মনোলিথিক বনাম অনুক্রমিক CFET

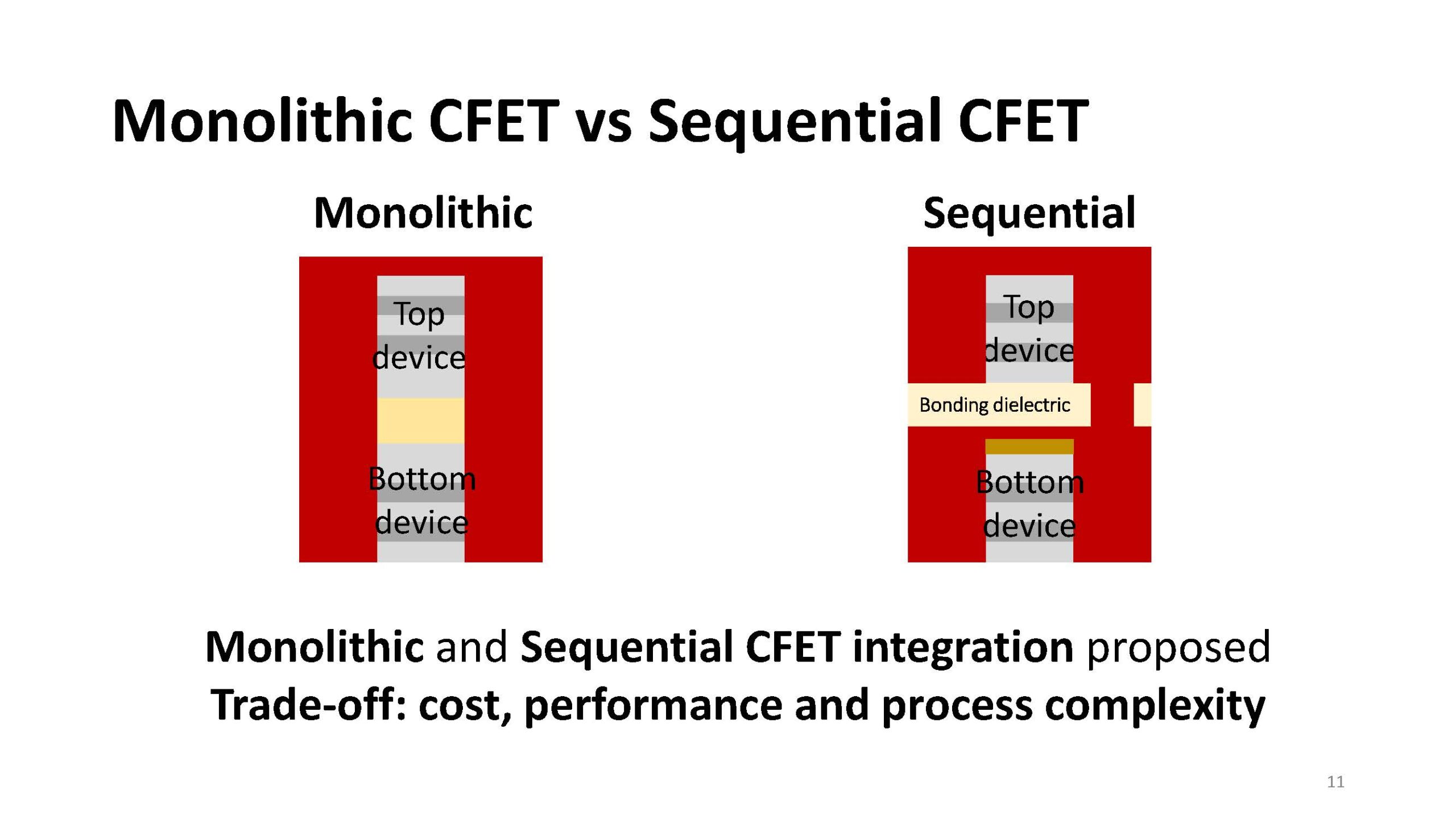

CFET তৈরিতে দুটি মৌলিকভাবে ভিন্ন পদ্ধতি রয়েছে। একচেটিয়া প্রবাহে সিএফইটিগুলি একটি অবিচ্ছিন্ন প্রক্রিয়া প্রবাহে একটি ওয়েফারের উপর তৈরি করা হয়। একটি অনুক্রমিক প্রবাহে নীচের ডিভাইসটি একটি ওয়েফারে তৈরি করা হয়, তারপরে একটি দ্বিতীয় ওয়েফারটি প্রথম ওয়েফারের সাথে বন্ধন করা হয় এবং উপরের যন্ত্রটি দ্বিতীয় ওয়েফারে তৈরি করা হয়।

একটি অনুক্রমিক প্রবাহে দুটি ডিভাইসের মধ্যে একটি বন্ধন অস্তরক উপস্থিত থাকে, চিত্র 7 দেখুন।

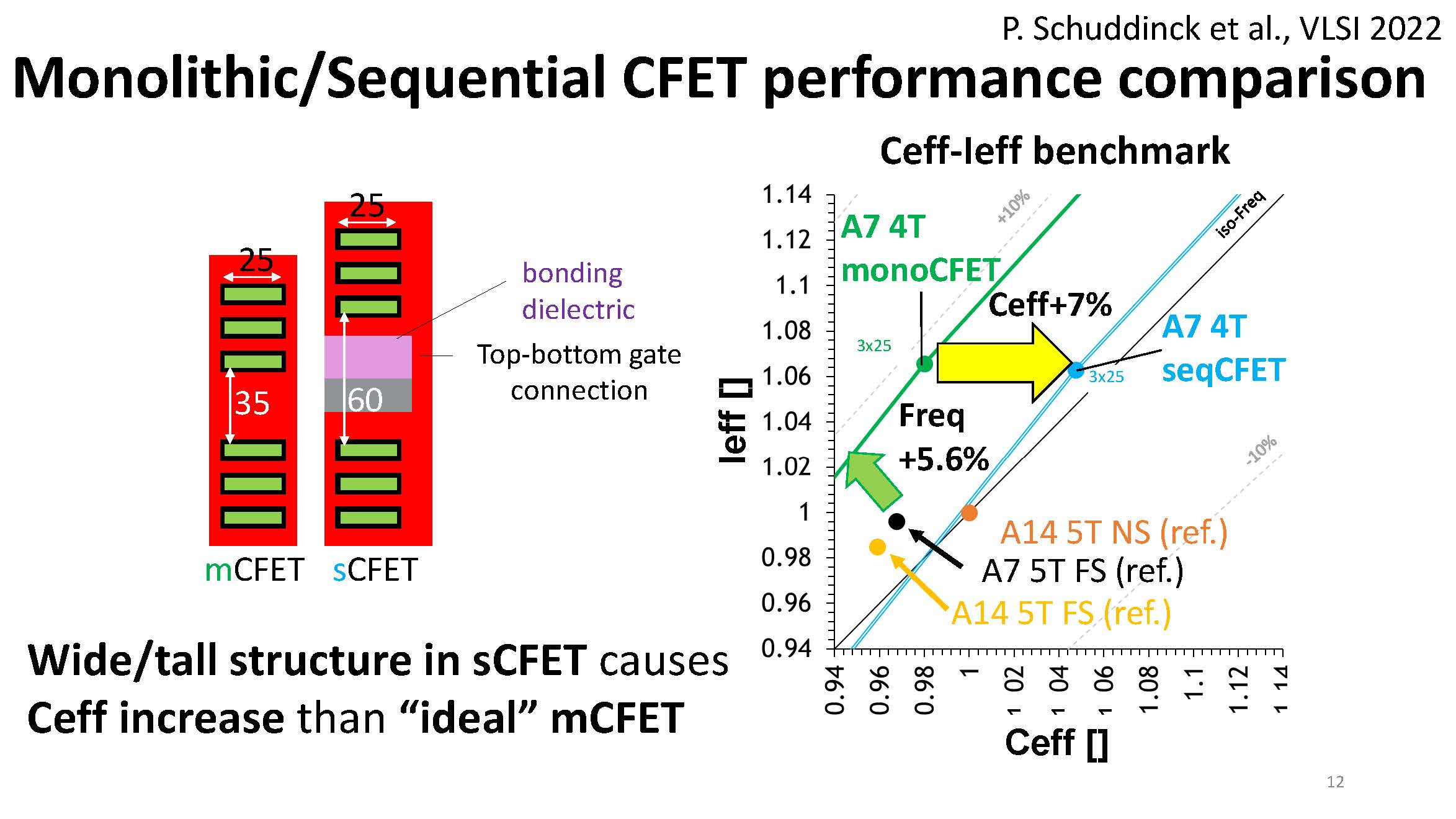

বন্ডিং ডাইইলেক্ট্রিকের কারণে কাঠামোটি লম্বা এবং উচ্চ ক্যাপাসিট্যান্স অবনমিত কর্মক্ষমতা রয়েছে, চিত্র 8 দেখুন।

একশিলা CFET-এর তুলনায় অনুক্রমিক CFETs তৈরি করা বেশি ব্যয়বহুল এবং এর মধ্যে এবং কর্মক্ষমতার অবনতির মধ্যে দেখা যাচ্ছে যে শিল্পটি একচেটিয়া CFET-এর উপর দৃষ্টি নিবদ্ধ করেছে।

মনোলিথিক CFET প্রক্রিয়াকরণ

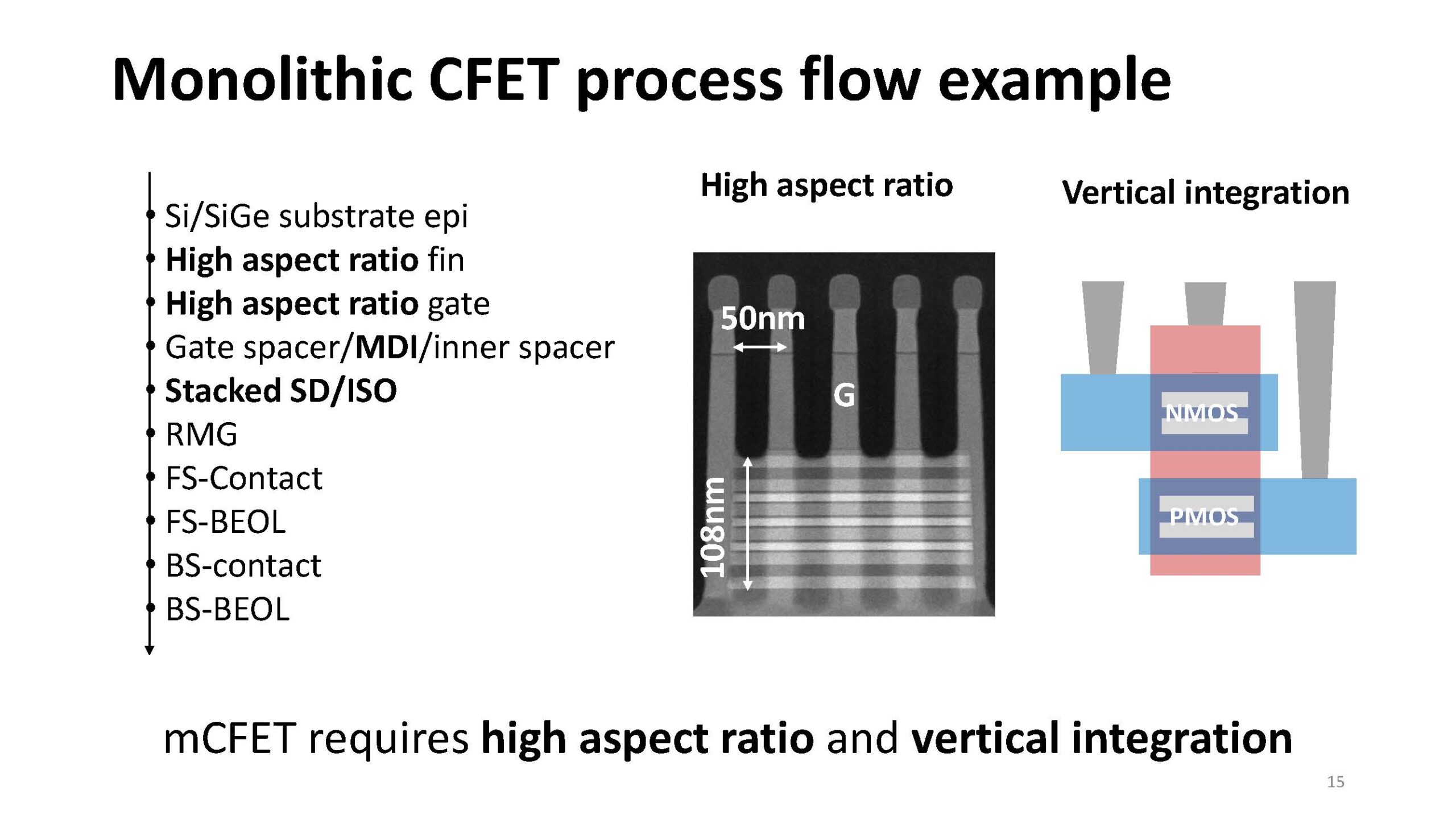

একচেটিয়া CFET প্রক্রিয়া চিত্র 9 এ চিত্রিত করা হয়েছে।

সাহসী পদক্ষেপগুলি বিশেষভাবে চ্যালেঞ্জিং:

- অনুভূমিক ন্যানোশিট স্ট্যাকগুলি (পাখনা) ইতিমধ্যেই উচ্চ আকৃতির অনুপাত, তারপরে একটি CFET তৈরি করার জন্য আপনি উচ্চতা দ্বিগুণের চেয়ে বেশি মাঝামাঝি একটি অপেক্ষাকৃত পুরু স্তর দিয়ে একে অপরের উপরে nFET এবং pFET স্ট্যাকগুলি স্ট্যাক করুন৷

- গেট গঠনটি পূর্ববর্তী পয়েন্টে বর্ণিত হিসাবে উচ্চ আকৃতির অনুপাতও।

- এপিটাক্সিয়াল উত্স/ড্রেনগুলি অবশ্যই একে অপরের থেকে উল্লম্বভাবে বিচ্ছিন্ন হতে হবে।

- স্পষ্টভাবে বলা হয়নি, নীচের ডিভাইসের উৎস/ড্রেনটি বানোয়াট এবং তারপর উপরের ডিভাইসের শীর্ষ উৎস/ড্রেনটি তৈরি করা হয়েছে। উপরের ডিভাইসের তাপ প্রক্রিয়াকরণ এবং পরবর্তী পদক্ষেপগুলি অবশ্যই কম তাপমাত্রায় করা উচিত যাতে নীচের ডিভাইসটি অবনমিত না হয়।

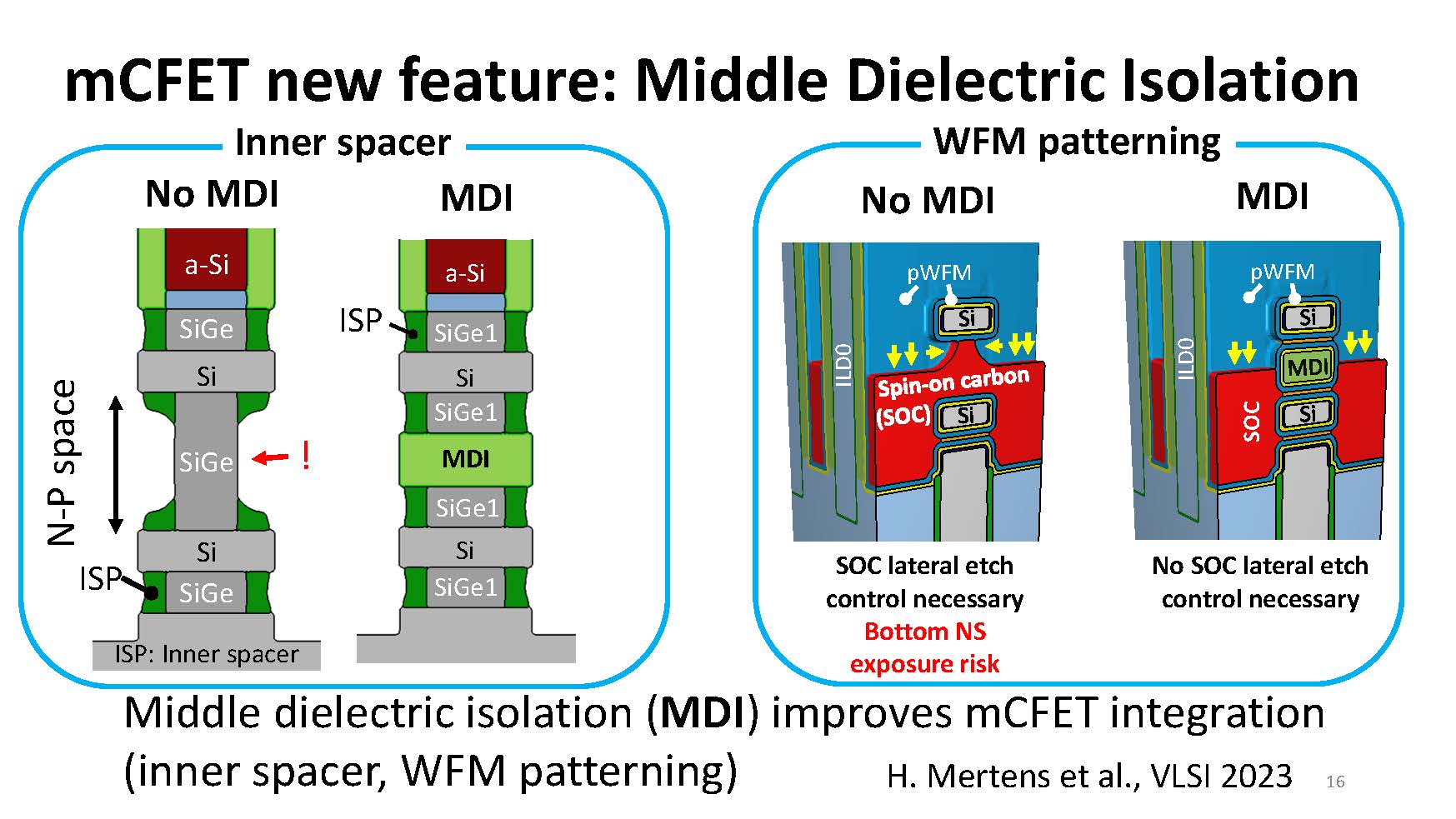

এই উপস্থাপনার একটি বিশেষ আকর্ষণীয় অংশ ছিল মধ্য ডাইলেক্ট্রিক আইসোলেশন (MDI) অংশ, আমি আগে এই সমস্যাটি দেখিনি। MDI অভ্যন্তরীণ স্পেসার এবং ওয়ার্ক ফাংশন উপাদান (WFM) প্যাটার্নিং প্রমাণ করে।

চিত্র 10 অভ্যন্তরীণ স্পেসার গঠন (বাম দিকে) এবং WFM প্যাটার্নিং (ডান দিকে) উপর MDI প্রভাবকে চিত্রিত করে।

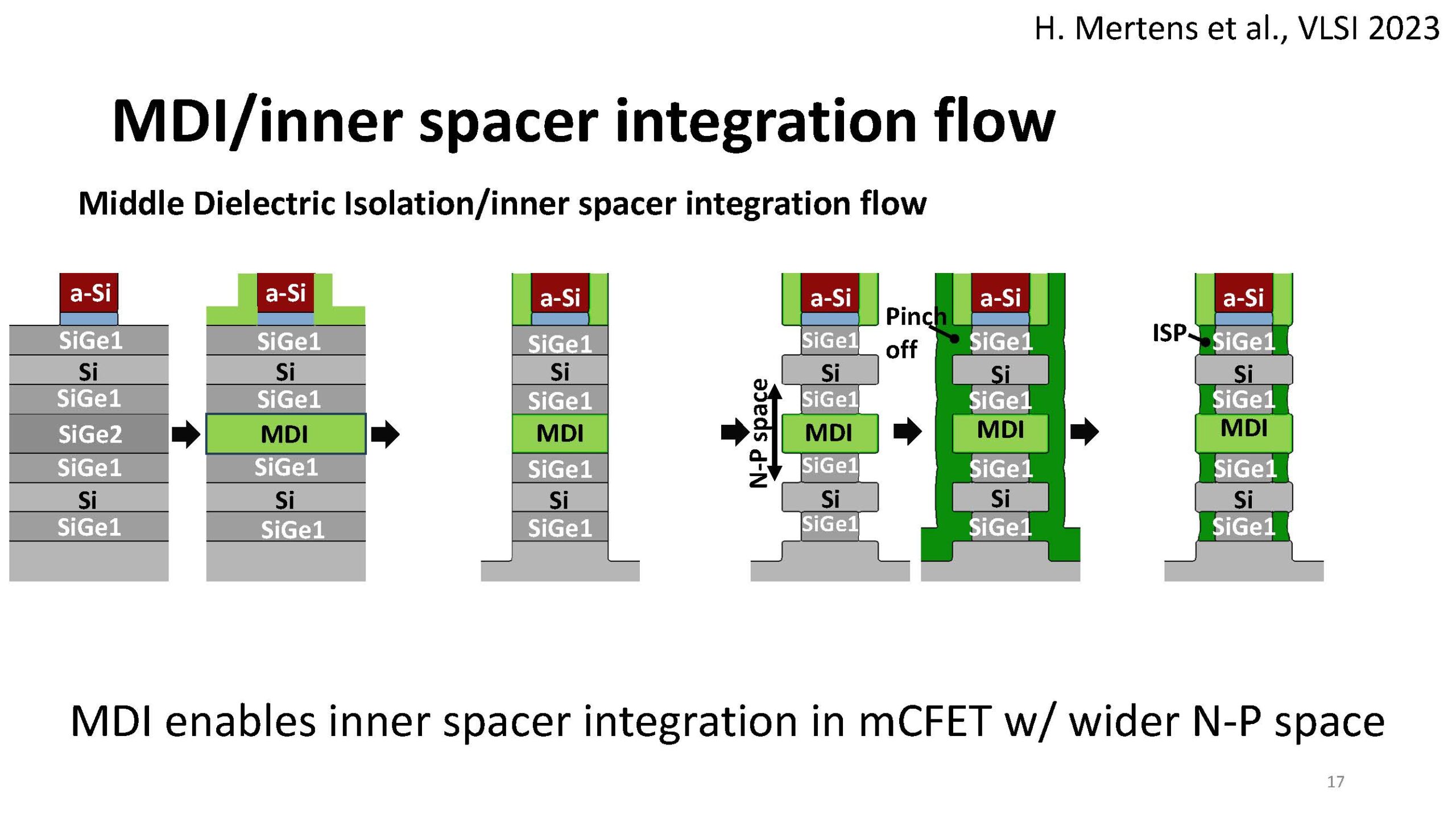

চিত্র 11 এমডিআই একীকরণ প্রবাহ চিত্রিত করে।

MDI সংহত করার মাধ্যমে nFET এবং pFET-এর মধ্যে উল্লম্ব ব্যবধান বৃদ্ধি করা যেতে পারে অভ্যন্তরীণ স্পেসারের গঠনকে প্রভাবিত না করে।

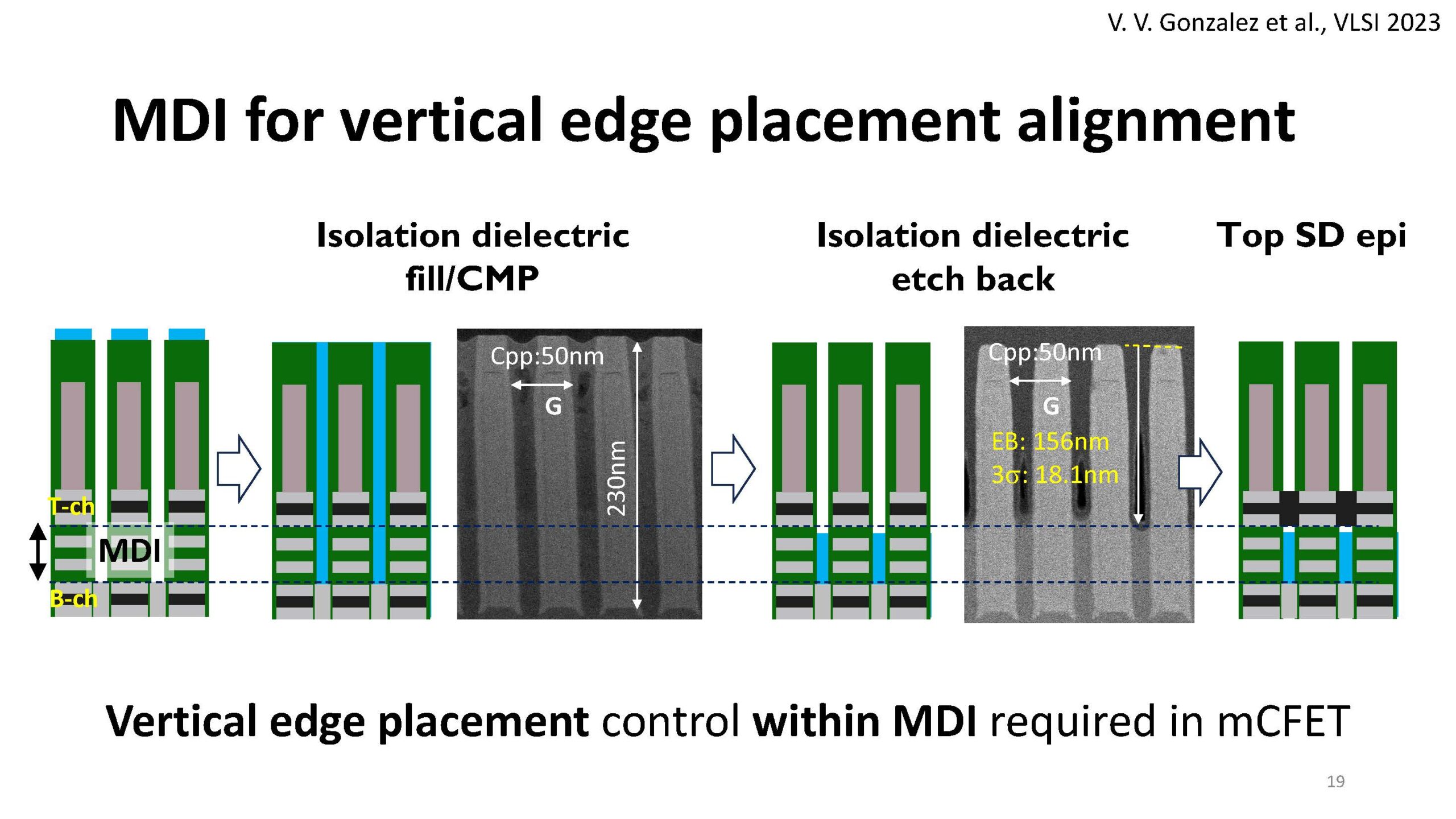

পূর্বে উল্লিখিত নীচের ডিভাইসের উৎস/ড্রেনটি বানোয়াট এবং তারপর উপরের ডিভাইসের উৎস/ড্রেনটি বানোয়াট। নীচের উৎস/ড্রেন গঠনের পর, উৎস/ড্রেন এপিটাক্সিয়াল গঠনের জন্য উপরের যন্ত্রটিকে উন্মুক্ত করার জন্য একটি বিচ্ছিন্ন ডাইলেক্ট্রিক জমা করা হয় এবং পিছনে খোদাই করা হয়। আইসোলেশন এচ ব্যাককে এমডিআই উচ্চতা দিয়ে নিয়ন্ত্রণ করতে হবে, চিত্র 12 দেখুন।

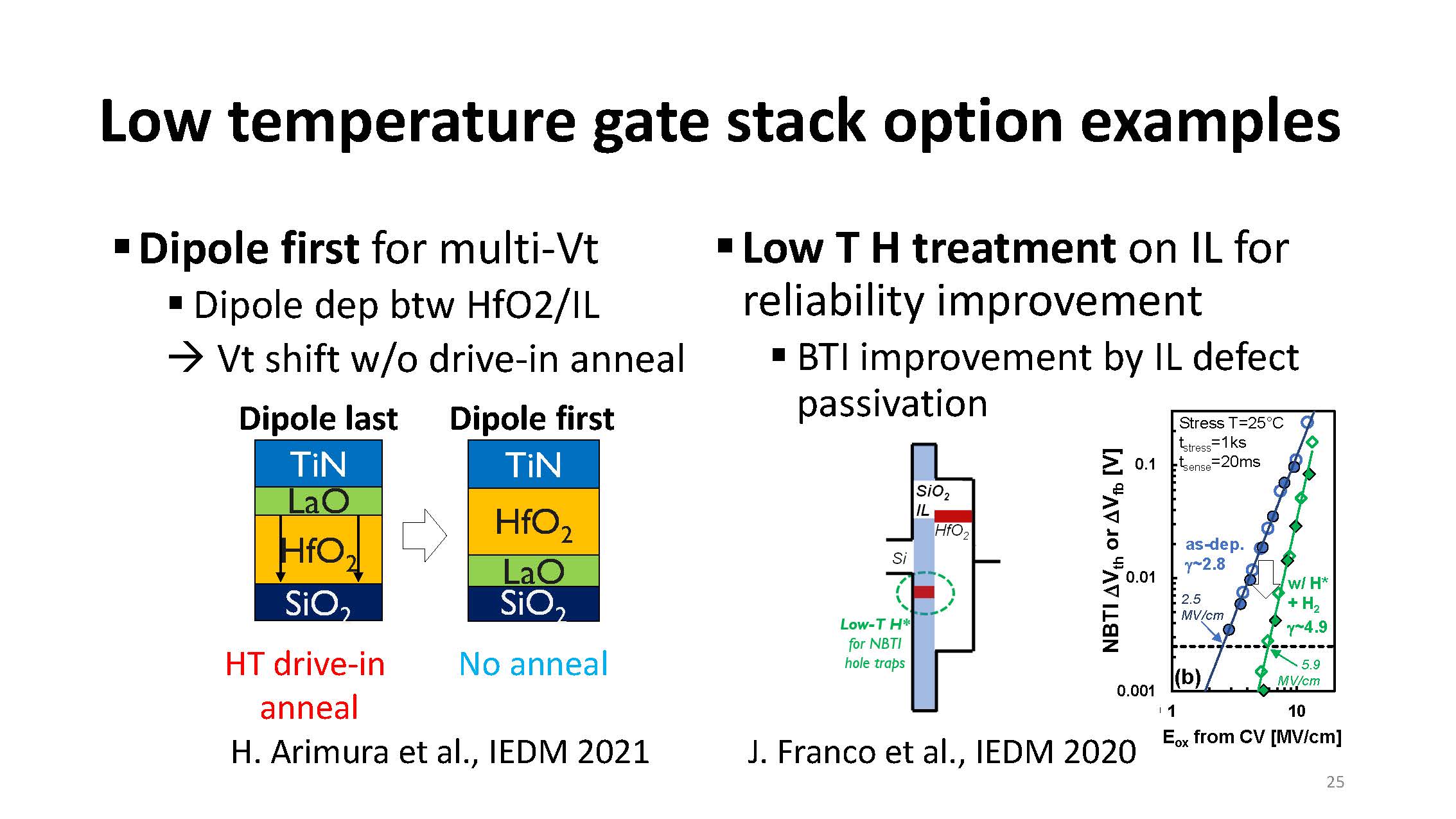

ডিভাইসের কর্মক্ষমতার তাপীয় অবক্ষয় কমানোর জন্য ডাইপোল ফার্স্ট প্রসেসিং সহ নতুন WFM বিকল্প এবং কোনো অ্যানিল এবং নিম্ন তাপমাত্রার আন্তঃস্তর গঠন প্রক্রিয়ার প্রয়োজন নেই, চিত্র 13 দেখুন।

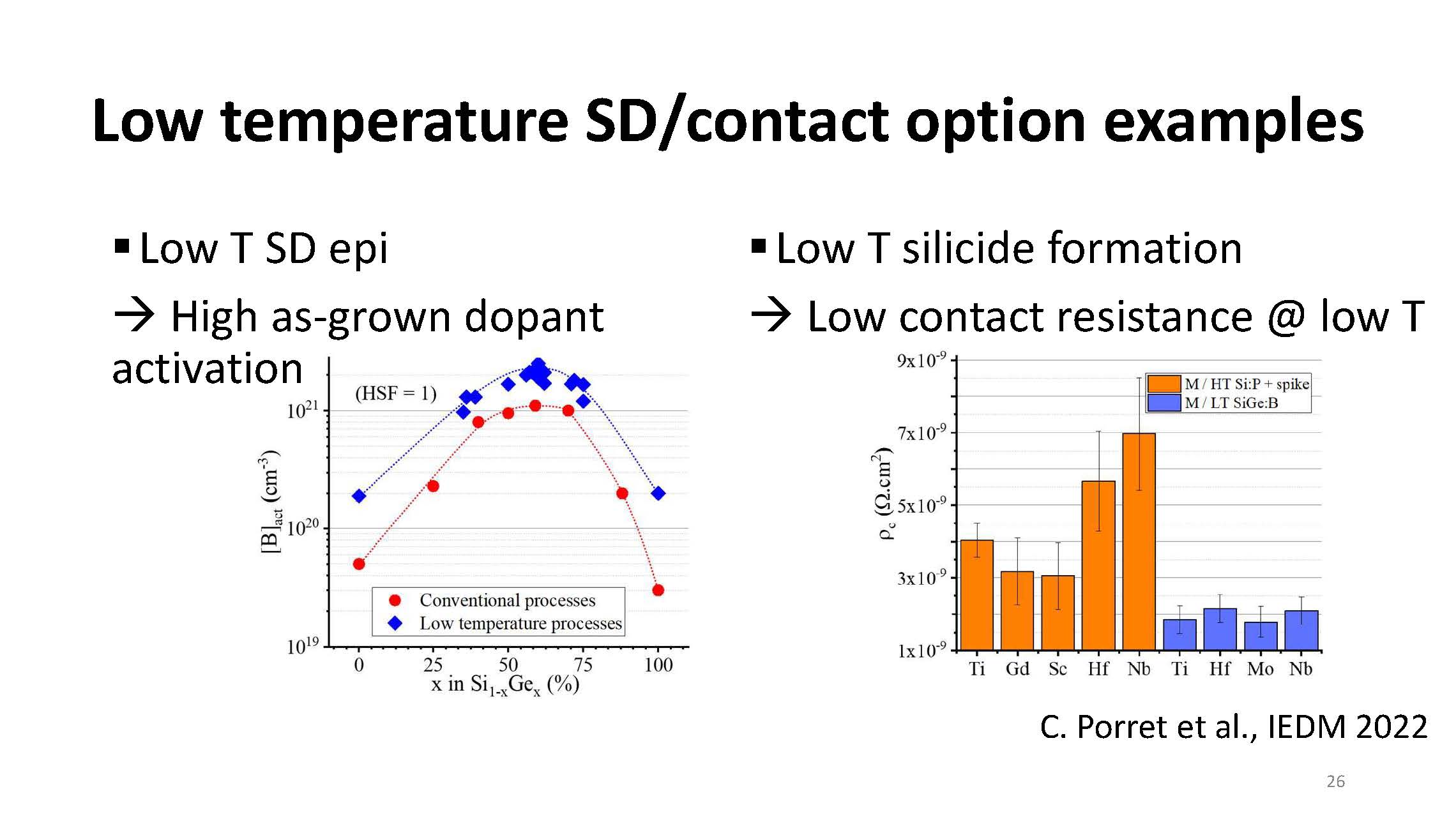

নিম্ন তাপমাত্রার উৎস/ড্রেন বৃদ্ধি এবং যোগাযোগ গঠনের জন্য নিম্ন তাপমাত্রার সিলিসাইডেরও প্রয়োজন, চিত্র 14 দেখুন।

নিম্ন তাপমাত্রার সিলিসাইড নীচের যন্ত্রের পিছনের দিকে সরাসরি যোগাযোগের জন্য বিশেষভাবে গুরুত্বপূর্ণ হবে। CFET ইন্টারকানেক্টের জন্য নিচের এবং উপরের ডিভাইসের সাথে যোগাযোগের প্রয়োজন হয় এবং পিছনের দিকে পাওয়ার ডেলিভারির আবির্ভাবের সাথে সাথে উপরের ডিভাইসের সাথে সামনের দিকের ইন্টারকানেক্ট স্ট্যাক থেকে যোগাযোগ করা হবে এবং নীচের ডিভাইসটি পিছনের দিক থেকে যোগাযোগ করা হবে। Molybdenum (Mo) এবং Niobium (Nb) pFET এর জন্য প্রতিশ্রুতিবদ্ধ এবং Scandium (Sc) nFET-এর জন্য প্রতিশ্রুতিবদ্ধ, যদিও SC ALD এর সাথে জমা করা কঠিন।

লাইন ইন্টারকানেক্টের পিছনে এবং মাঝখানে

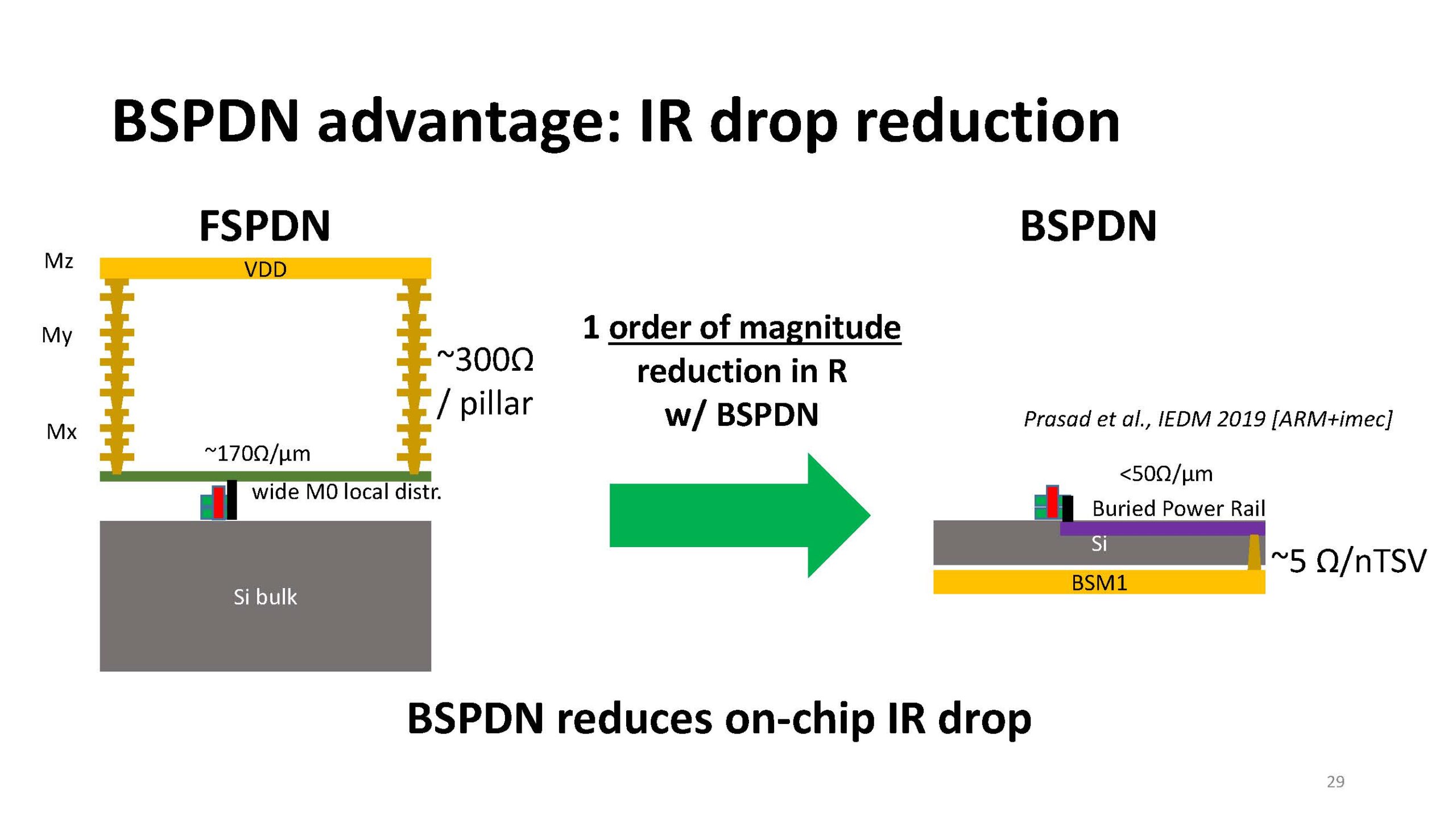

যেমনটা আগেও লিখেছি এখানে ব্যাক সাইড পাওয়ার ডেলিভারি নেটওয়ার্ক (BSPDN) এই বছর ইন্টেল এবং স্যামসাং এবং TSMC দ্বারা 2026 সালে প্রবর্তন করা হবে বলে আশা করা হচ্ছে। ফ্রন্টসাইড সিগন্যাল কানেকশন এবং ব্যাকসাইড পাওয়ার কানেকশনে আন্তঃসংযোগ বিভক্ত করা হলে IR ড্রপ (বিদ্যুতের ক্ষতি) একটি ক্রম অনুসারে কমে যায়, চিত্র দেখুন 15।

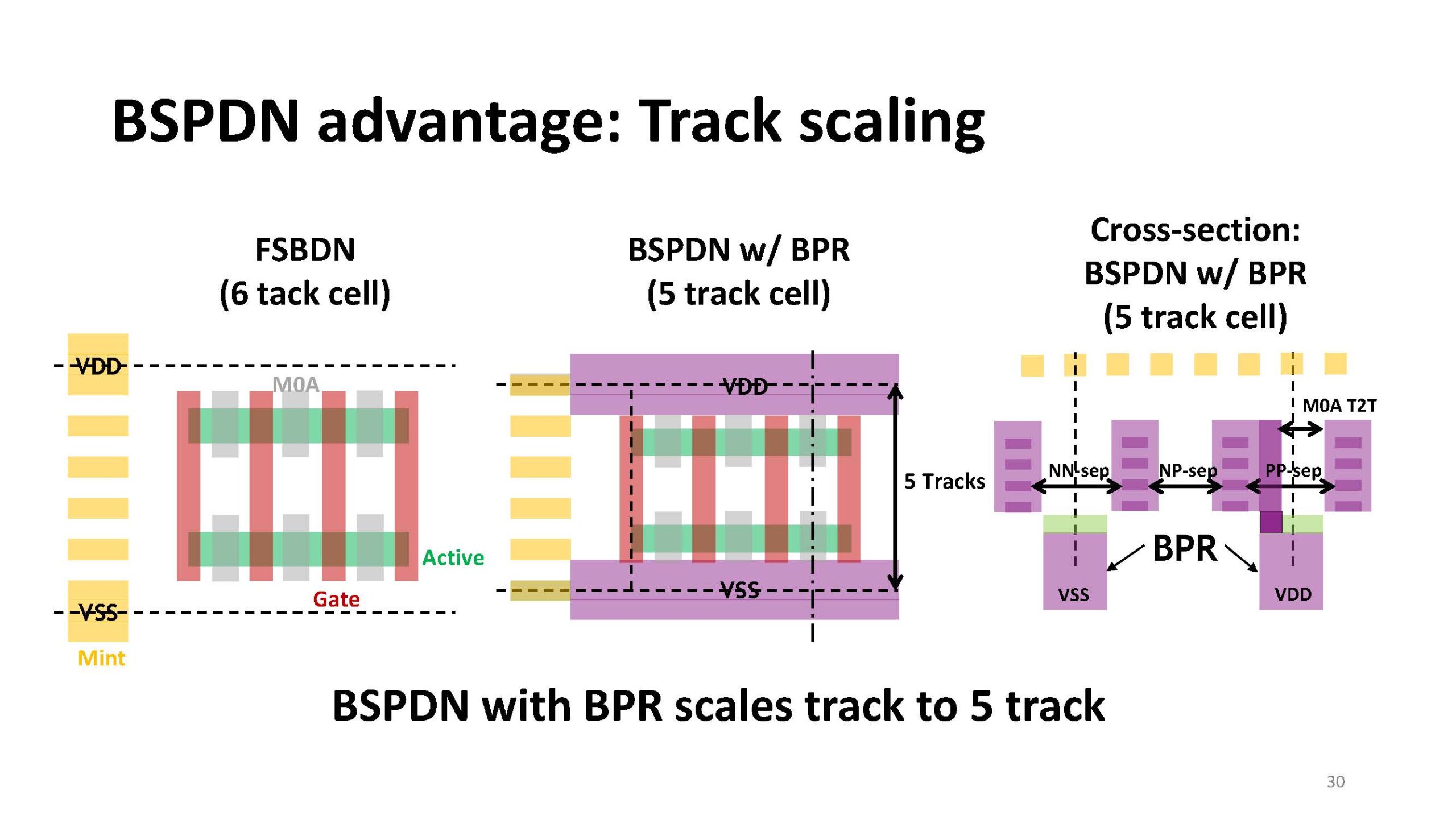

BSPDN একটি 6-ট্র্যাক থেকে 5-ট্র্যাক কক্ষে হ্রাসকে সমর্থন করে ট্র্যাক স্কেলিংকেও উন্নত করে, চিত্র 16 দেখুন।

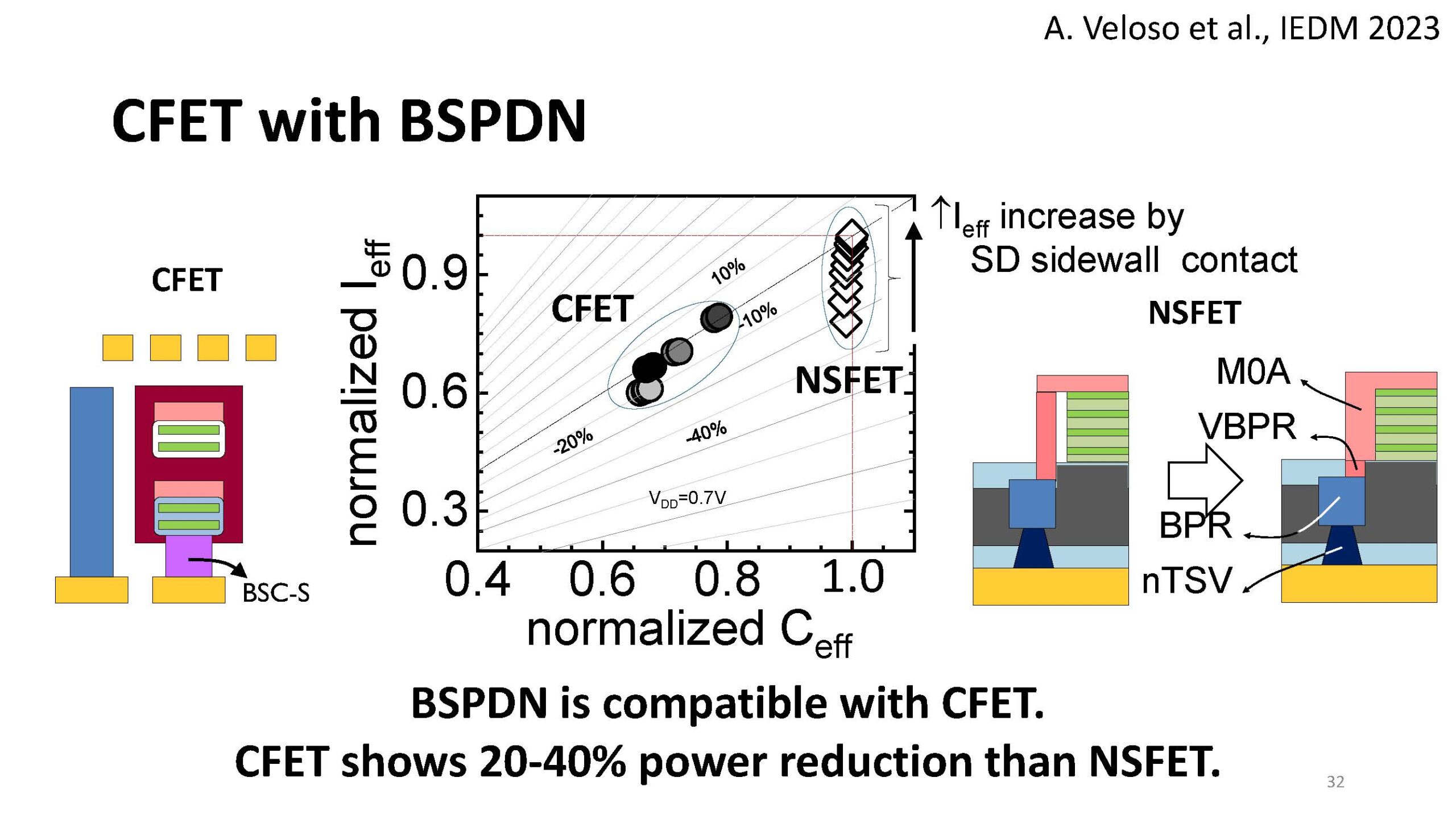

CFET-এর সাথে BSPDN-এর ইন্টিগ্রেশন 20% থেকে 40% পাওয়ার কমিয়ে দিতে পারে বনাম অনুভূমিক স্ট্যাকড ন্যানোশিট (HNS), চিত্র 17 দেখুন।

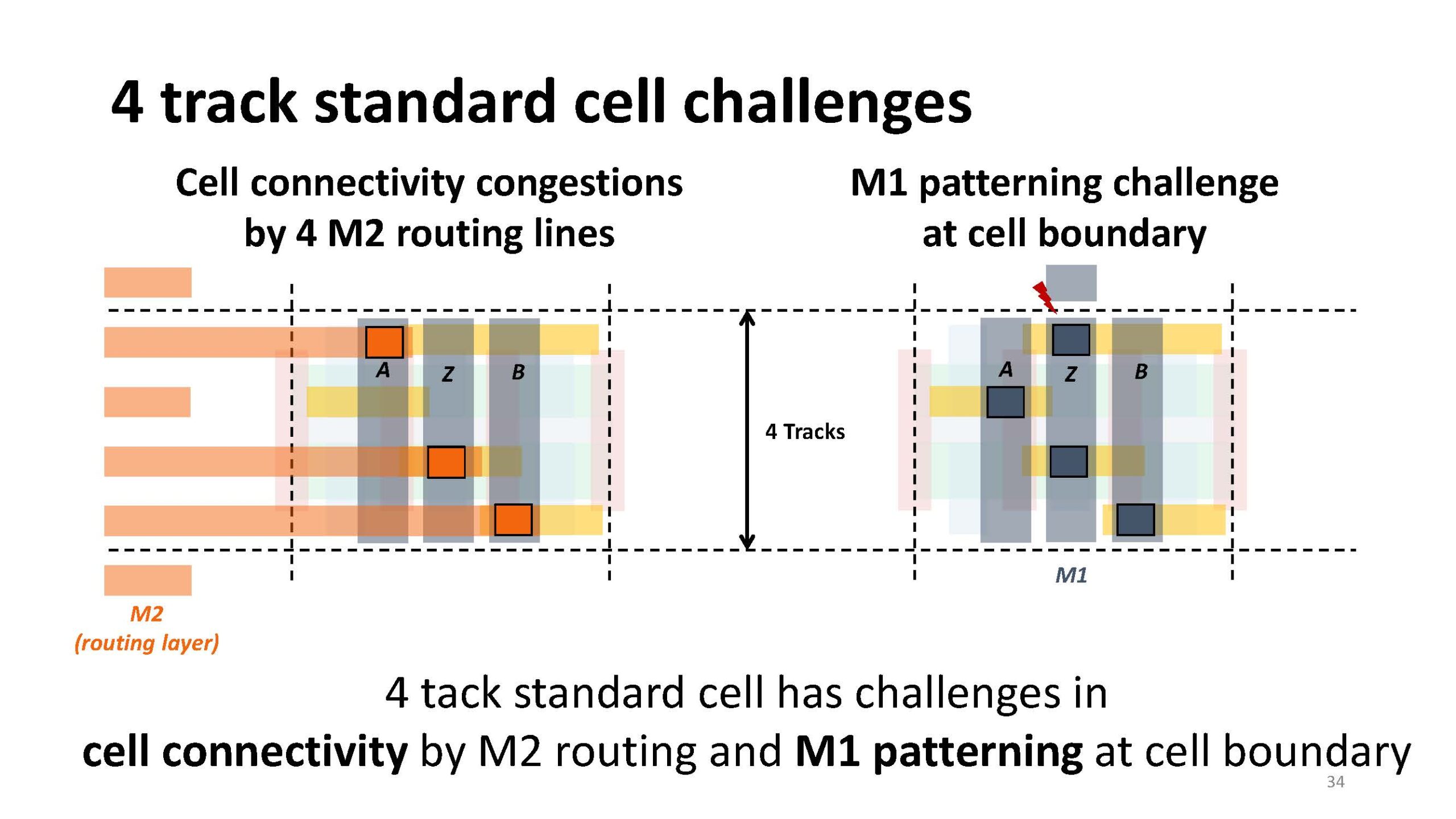

একটি 5-ট্র্যাক সেল অতিক্রম করে 4-ট্র্যাক সেল আন্তঃসংযোগের চ্যালেঞ্জগুলি অতিক্রম করতে হবে, চিত্র 18 দেখুন।

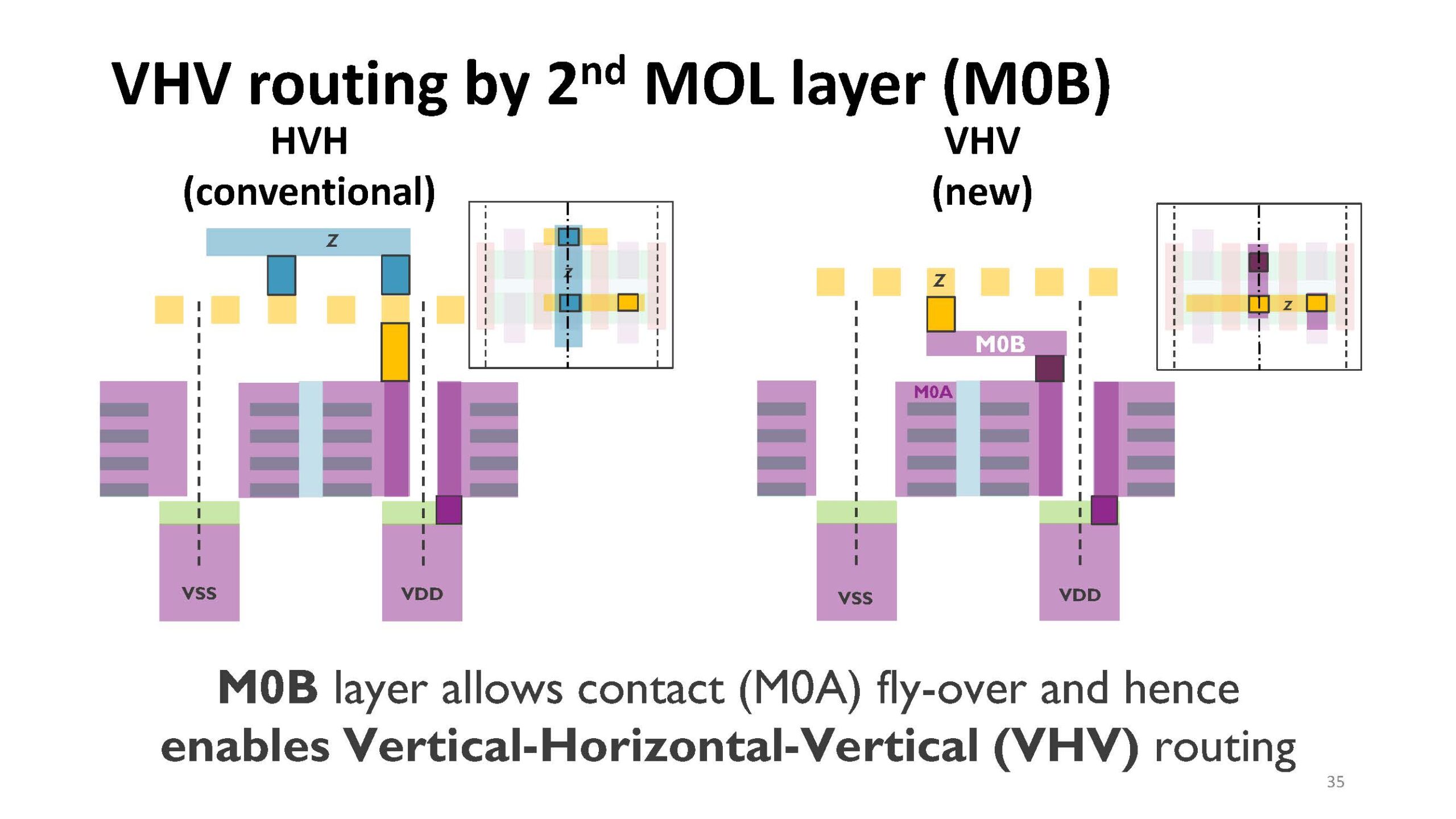

অতিরিক্ত মিডল অফ লাইন (MOL) স্তর সহ উল্লম্ব-অনুভূমিক-উল্লম্ব বিন্যাস 4-ট্র্যাক কোষ সক্রিয় করতে পারে, চিত্র 19 দেখুন।

আমি এর আগে এই এলাকায় ইমেকের কাজ সম্পর্কে লিখেছি এখানে তাই আমি সেই তথ্যের পুনরাবৃত্তি করব না।

আমি নাওটোকে জিজ্ঞাসা করলাম একটি 4-ট্র্যাক সেল ছাড়িয়ে 3-ট্র্যাকের ঘরে যেতে কী লাগবে, তিনি উত্তর দিয়েছিলেন যে ইমেক এখন সেই অপ্টিমাইজেশানে কাজ করছে, এতে এমওএল স্তরগুলি এবং সম্ভবত উপরের থেকে নীচের সংযোগের পাশের প্রয়োজন হতে পারে। ডিভাইস যা স্ট্যান্ডার্ড সেল লেআউটকে প্রভাবিত করবে।

আমি নাওটোকেও জিজ্ঞেস করলাম যখন সে ভেবেছিল যে আমরা হয়তো CFETs বাস্তবায়িত দেখতে পাব এবং সে বলল সম্ভবত A10 লজিক জেনারেশন বা A7 জেনারেশন।

লেখকরা নোট করেছেন, ইন্টেল, স্যামসাং এবং টিএসএমসি সকলেই এই বছর IEDM-তে CFET-এর উপর কাজ প্রকাশ করেছে এবং Intel এবং TSMC উভয়ের কাছে প্রযুক্তি বিকল্প মানচিত্র রয়েছে যা ফিনএফইটিগুলিকে HNS এবং তারপরে CFET-কে পথ দেখায়৷

উপসংহার

এইচএনএস-এর পর পরবর্তী প্রজন্মের বিকল্প হিসেবে সিএফইটি-র উন্নয়নে ইমেক চমৎকার অগ্রগতি প্রদর্শন করে চলেছে। এই কাজের ডিভাইসে ইন্টিগ্রেশন বিকল্পগুলির পাশাপাশি BSPDN এবং MOL বিকল্পগুলি সমস্ত বর্ণনা করা হয়েছে।

এছাড়াও পড়ুন:

IEDM 2023 - মডেলিং 300mm Wafer Fab কার্বন নির্গমন

এর মাধ্যমে এই পোস্টটি ভাগ করুন:

- এসইও চালিত বিষয়বস্তু এবং পিআর বিতরণ। আজই পরিবর্ধিত পান।

- PlatoData.Network উল্লম্ব জেনারেটিভ Ai. নিজেকে ক্ষমতায়িত করুন। এখানে প্রবেশ করুন.

- প্লেটোএআইস্ট্রিম। Web3 ইন্টেলিজেন্স। জ্ঞান প্রসারিত. এখানে প্রবেশ করুন.

- প্লেটোইএসজি। কার্বন, ক্লিনটেক, শক্তি, পরিবেশ সৌর, বর্জ্য ব্যবস্থাপনা. এখানে প্রবেশ করুন.

- প্লেটো হেলথ। বায়োটেক এবং ক্লিনিক্যাল ট্রায়াল ইন্টেলিজেন্স। এখানে প্রবেশ করুন.

- উত্স: https://semiwiki.com/semiconductor-services/340811-iedm-2023-imec-cfet/

- : আছে

- : হয়

- :না

- $ ইউপি

- 06

- 07

- 08

- 09

- 1

- 10

- 11

- 12

- 13

- 14

- 15%

- 16

- 17

- 19

- 2023

- 2026

- 25

- 26

- 29

- 30

- 32

- 35%

- 7

- 8

- 9

- a

- সম্পর্কে

- যোগ

- অতিরিক্ত

- সুবিধা

- আবির্ভাব

- পর

- আবার

- সব

- ইতিমধ্যে

- এছাড়াও

- যদিও

- সর্বদা

- an

- এবং

- মনে হচ্ছে,

- পন্থা

- রয়েছি

- এলাকায়

- AS

- দৃষ্টিভঙ্গি

- At

- পিছনে

- ভিত্তি

- BE

- কারণ

- পরিণত

- হয়ে

- হয়েছে

- আগে

- মধ্যে

- তার পরেও

- সাহসী

- উভয়

- পাদ

- by

- কল

- নামক

- CAN

- কারবন

- কোষ

- সেল

- চ্যালেঞ্জ

- চ্যালেঞ্জিং

- সুযোগ

- তুলনা

- পরিপূরক

- সংযোগ

- সংযোগ

- সীমাবদ্ধতার

- যোগাযোগ

- যোগাযোগ

- চলতে

- একটানা

- নিয়ন্ত্রিত

- বিলি

- আমানত

- জমা

- বর্ণিত

- উন্নয়ন

- যন্ত্র

- ডিভাইস

- বিভিন্ন

- সরাসরি

- আলোচনা

- do

- সম্পন্ন

- দ্বিত্ব

- ড্রপ

- প্রতি

- সহজ

- প্রান্ত

- প্রভাব

- সক্ষম করা

- সম্ভব

- ভোগ

- যথেষ্ট

- অবশেষে

- চমত্কার

- প্রত্যাশিত

- ব্যয়বহুল

- ব্যাখ্যা

- স্পষ্টভাবে

- FET

- ব্যক্তিত্ব

- ডানা

- চূড়ান্ত

- সূক্ষ্ম

- প্রথম

- প্রবাহ

- দৃষ্টি নিবদ্ধ করা

- অনুসরণ করা

- জন্য

- গঠন

- থেকে

- সদর

- ক্রিয়া

- মৌলিকভাবে

- গেট

- প্রজন্ম

- দান

- Go

- উন্নতি

- ছিল

- কঠিন

- আছে

- he

- উচ্চতা

- উচ্চ

- ঊর্ধ্বতন

- হাইলাইট

- তার

- অনুভূমিক

- HTTPS দ্বারা

- হুয়াওয়ে

- i

- প্রকাশ

- প্রভাব

- হানিকারক

- বাস্তবায়িত

- গুরুত্বপূর্ণ

- উন্নত

- উন্নত

- in

- বর্ধিত

- শিল্প

- তথ্য

- ভিতরের

- পরিবর্তে

- একীভূত

- ইন্টিগ্রেশন

- ইন্টেল

- মজাদার

- মধ্যে

- প্রবর্তন করা

- ভিন্ন

- বিচ্ছিন্নতা

- সমস্যা

- IT

- JPG

- স্তর

- স্তর

- বিন্যাস

- নেতাদের

- বিশালাকার

- বাম

- লাইন

- যুক্তিবিদ্যা

- ক্ষতি

- কম

- করা

- মানচিত্র

- সঙ্গী

- উপাদান

- সর্বোচ্চ প্রস্থ

- মে..

- উল্লিখিত

- মধ্যম

- হতে পারে

- কমান

- মূর্তিনির্মাণ

- Mol

- একশিলা

- অধিক

- চলন্ত

- বহু

- অবশ্যই

- প্রয়োজনীয়

- প্রয়োজন

- প্রয়োজন

- নেটওয়ার্ক

- নতুন

- পরবর্তী

- না।

- বিঃদ্রঃ

- এখন

- সংখ্যা

- of

- on

- একদা

- ONE

- অপ্টিমাইজেশান

- পছন্দ

- অপশন সমূহ

- or

- ক্রম

- অন্যান্য

- আমাদের

- বাইরে

- পরাস্ত

- পৃষ্ঠা

- অংশ

- বিশেষত

- কর্মক্ষমতা

- পিচ

- স্থাননির্ণয়

- Plato

- প্লেটো ডেটা ইন্টেলিজেন্স

- প্লেটোডাটা

- যোগ

- বিন্দু

- সম্ভবত

- পোস্ট

- ক্ষমতা

- বর্তমান

- উপহার

- উপস্থাপন

- উপস্থাপন

- আগে

- পূর্বে

- জন্য

- প্রক্রিয়া

- প্রসেস

- প্রক্রিয়াজাতকরণ

- উন্নতি

- আশাপ্রদ

- প্রমাণ

- প্রদান

- প্রকাশিত

- বিশুদ্ধরূপে

- অনুপাত

- পড়া

- হ্রাস করা

- হ্রাসপ্রাপ্ত

- হ্রাস

- হ্রাস

- অপেক্ষাকৃতভাবে

- পুনরাবৃত্তি

- প্রয়োজন

- প্রয়োজন

- প্রতিক্রিয়াশীল

- অধিকার

- প্রমাথী

- বলেছেন

- স্যামসাং

- SC

- আরোহী

- দ্বিতীয়

- দেখ

- দেখা

- প্রদর্শনী

- দেখাচ্ছে

- পাশ

- সংকেত

- So

- কথা বলা

- গাদা

- স্তুপীকৃত

- স্ট্যাক

- স্ট্যাক

- মান

- প্রারম্ভিক ব্যবহারের নির্দেশাবলী

- গঠন

- পরবর্তী

- সমর্থক

- গ্রহণ করা

- কথা বলা

- প্রযুক্তিঃ

- প্রযুক্তি উন্নয়ন

- চেয়ে

- যে

- সার্জারির

- তারপর

- তপ্ত

- এই

- এই বছর

- চিন্তা

- সময়

- থেকে

- শীর্ষ

- পথ

- স্থানান্তর

- tsmc

- দুই

- আপডেট

- বনাম

- উল্লম্ব

- উল্লম্বভাবে

- মাধ্যমে

- vs

- ছিল

- উপায়..

- we

- আমরা একটি

- পশ্চিম

- কি

- কখন

- ব্যাপকতর

- ইচ্ছা

- সঙ্গে

- ছাড়া

- হয়া যাই ?

- কাজ

- would

- লেখা

- লিখিত

- বছর

- আপনি

- zephyrnet