আপনি যখন "FPGA" মনে করেন, তখন মনে কী আসে? বিশাল, ব্যয়বহুল অংশগুলি প্রচুর যুক্তি ধারণ করতে সক্ষম তবে প্রচুর শক্তিও খরচ করে। রি-কনফিগারযোগ্য প্ল্যাটফর্ম যা প্রাক-সিলিকন পরীক্ষায় একটি SoC ডিজাইনের জন্য RTL গ্রাস করতে পারে। বড় স্প্ল্যাশী কর্পোরেট অধিগ্রহণ যেখানে বিনিয়োগকারীরা প্রচুর অর্থ উপার্জন করেছে৷ বহিরাগত 3D প্যাকেজিং এবং উন্নত আন্তঃসংযোগ। তবে সম্ভবত সস্তা নয়, ছোট প্যাকেজ, কম পিনের সংখ্যা, কম স্ট্যান্ডবাই পাওয়ার পার্টস, তাই না? ফ্লেক্স লজিক্সের ইএফপিজিএ কম-পাওয়ার প্রোগ্রামেবল লজিকের জন্য বেসিকগুলিতে ফিরে যায় যা কম খরচ, উচ্চ ভলিউম এবং আকার-সীমাবদ্ধ ডিভাইসগুলি গ্রহণ করতে পারে।

দুটি প্রোগ্রামযোগ্য রাস্তা একটি পছন্দ উপস্থাপন করেছে

নিজের সাথে ডেটিং করার ঝুঁকিতে, তখনকার FPGA প্রযুক্তির সাথে আমার প্রথম এক্সপোজার ফিরে আসে যখন Altera তাদের EPROM-ভিত্তিক EP1200 পরিবারকে 40 MHz ঘড়ি, 16 mW সক্রিয় শক্তি এবং 400 mW স্ট্যান্ডবাই সহ একটি 15-পিন ডিআইপি প্যাকেজে নিয়ে আসে। ক্ষমতা এটি একটি পরিকল্পিত সম্পাদক এবং গেট ম্যাক্রোগুলির একটি লাইব্রেরির সাথে এসেছিল। ডিজাইনাররা তাদের যুক্তি আঁকবে, তাদের অংশ "পুড়িয়ে ফেলবে", এটি পরীক্ষা করবে, এটি একটি UV বাতির নীচে নিক্ষেপ করবে এবং এটি কাজ না করলে এটি মুছে ফেলবে এবং আবার চেষ্টা করবে।

শীঘ্রই, প্রথম কিছু Xilinx FPGA সহ আমাদের অন্য ল্যাবে একটি বোর্ড দেখা গেল। এগুলি EPROM-ভিত্তিক-এর পরিবর্তে RAM-ভিত্তিক ছিল - UV বাতি অপেক্ষা না করে বা বোর্ড থেকে অংশটি সরানো ছাড়াই বড়, দ্রুত এবং পুনরায় প্রোগ্রামিং। দ্রুত গুণকগুলির প্রবর্তনের সাথে ভিতরের যুক্তিটি আরও জটিল ছিল। এই অংশগুলি কেবল যুক্তিকে ঝাড়ু দিতে পারে না তবে দ্রুত পুনরায় ডিজাইন চক্রের সাথে কাস্টম ডিজিটাল সিগন্যাল প্রক্রিয়াকরণ ক্ষমতা অন্বেষণ করতেও ব্যবহার করা যেতে পারে।

এটি প্রোগ্রামেবল সিলিকন অস্ত্র প্রতিযোগিতা শুরু করে এবং পিএলডি - প্রোগ্রামেবল লজিক ডিভাইস - এবং এফপিজিএ-র মধ্যে একটি দ্বিখণ্ডন তৈরি হয়। উৎপাদনকারীরা পছন্দ করেছেন, Altera এবং Xilinx FPGA স্কেলেবিলিটির উচ্চ রাস্তা এবং Actel, Lattice এবং অন্যরা "গ্লু লজিক" এর জন্য বিল-অফ-ম্যাটেরিয়াল খরচ কমাতে PLD নমনীয়তার নিম্ন রাস্তা গ্রহণ করেছে।

eFPGA কম-পাওয়ার প্রোগ্রামেবল লজিক সমীকরণ পরিবর্তন করে

যা একটি পরিপক্ক বাজারের মতো শোনাচ্ছে, এক প্রান্তে প্রবেশের জন্য একটি উচ্চ বাধা এবং অন্য দিকে আরও পণ্যযুক্ত অফার। কিন্তু যদি প্রোগ্রামেবল লজিক একটি আইপি ব্লক হয় যা এই অলীক যুগে যেকোনো চিপে ডিজাইন করা যেতে পারে - একটি ছোট, কম-পাওয়ার FPGA সহ? এটি বাধাকে অতিক্রম করবে (অন্তত নিম্ন এবং মধ্য-পরিসরের অফারে) এবং পণ্যীকরণ।

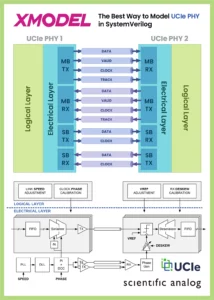

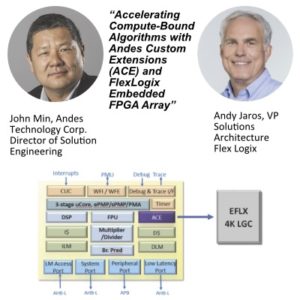

ফ্লেক্স লজিক্স EFLX 1K eFPGA টাইলের সাথে সেই চ্যালেঞ্জটি গ্রহণ করেছে। প্রতিটি লজিক টাইলে RAM, ক্লকিং এবং ইন্টারকানেক্ট সহ 560টি ছয়-ইনপুট লুক-আপ টেবিল (LUTs) রয়েছে। EFLX টাইলস সাজানো বিভিন্ন যুক্তি এবং DSP ভূমিকা পরিচালনা করার ক্ষমতা দেয়। তবে এর সবচেয়ে বিশিষ্ট বৈশিষ্ট্যগুলি এর আকার এবং শক্তি ব্যবস্থাপনা হতে পারে।

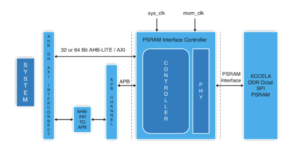

TSMC 40ULP তে তৈরি, EFLX 1K টাইল 1.5 মিমিতে ফিট করে2 এবং স্টেট রিটেনশন সহ ডিপ স্লিপ মোডের জন্য পাওয়ার-গেটিং অফার করে - প্রথাগত PLDs থেকে অনেক বেশি আক্রমনাত্মক। EFLX 1K-এ FPGAs থেকে ধার করা উৎপাদন-প্রস্তুত বৈশিষ্ট্যও রয়েছে। এটি বিটস্ট্রিম কনফিগারেশনের জন্য AXI বা JTAG ইন্টারফেস উপস্থাপন করে, রিডব্যাক সার্কিটরি সফ্ট এরর চেকিং সক্ষম করে এবং স্ট্রিমলাইনড ভেক্টর সহ একটি টেস্ট মোড কভারেজ উন্নত করে এবং পরীক্ষার সময় কমিয়ে দেয়।

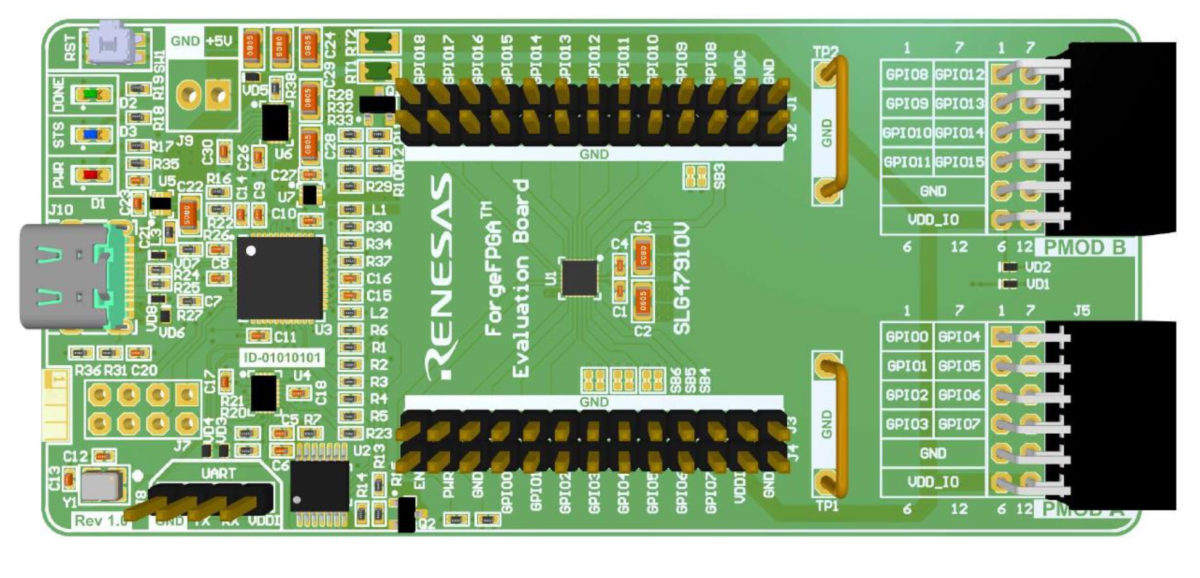

এই পরবর্তী ছবির কেন্দ্রে চিপ দেখুন? এটি একটি QFN-24 প্যাকেজে রেনেসাসের একটি ForgeFPGA, EFLX 1K IP-এর উপর ভিত্তি করে, যা রেনেসাস ভলিউমে সাব-$1 মূল্য পয়েন্টে অফার করে। এর স্ট্যান্ডবাই টার্গেট কারেন্ট চেক ইন 20uA এর কম। ছোট আকার, কম খরচ, এবং কম শক্তি খোলা দরজা পূর্বে FPGAs বন্ধ. ForgeFPGA-এর বংশধারা সিলেগো টেকনোলজিতে ফিরে আসে, তারপর ডায়ালগ সেমিকন্ডাক্টর, যা 2021 সালে রেনেসাস দ্বারা অর্জিত হয়েছিল।

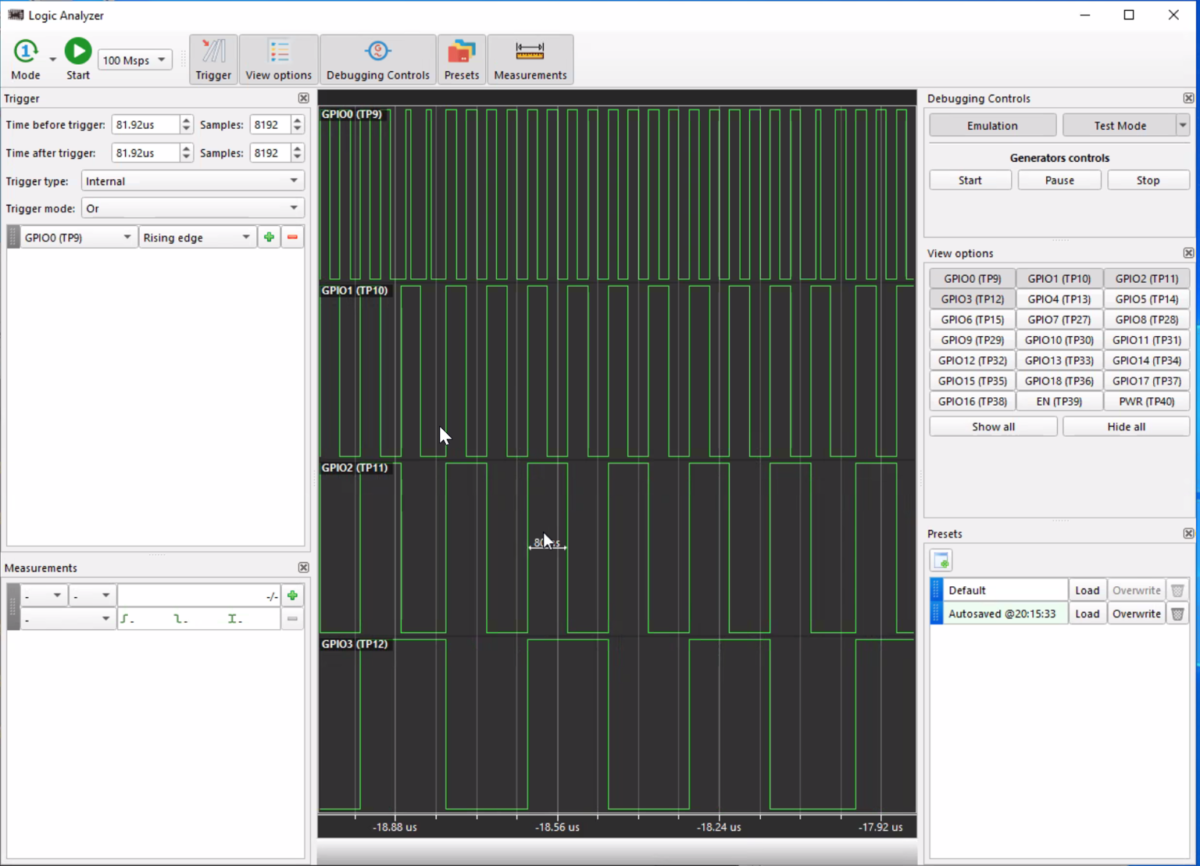

রেনেসাস গো কনফিগার আইডিই পরিবেশ নিয়ে আসে, ফ্লেক্স লজিক্স ইএফএলএক্স কম্পাইলারের উপরে একটি গ্রাফিকাল ইউজার ইন্টারফেস রাখে। এটি ForgeFPGA পিন ম্যাপিং সমর্থন করে, ভেরিলগ কম্পাইল করে, একটি বিটস্ট্রিম তৈরি করে এবং একটি হালকা লজিক বিশ্লেষক রয়েছে।

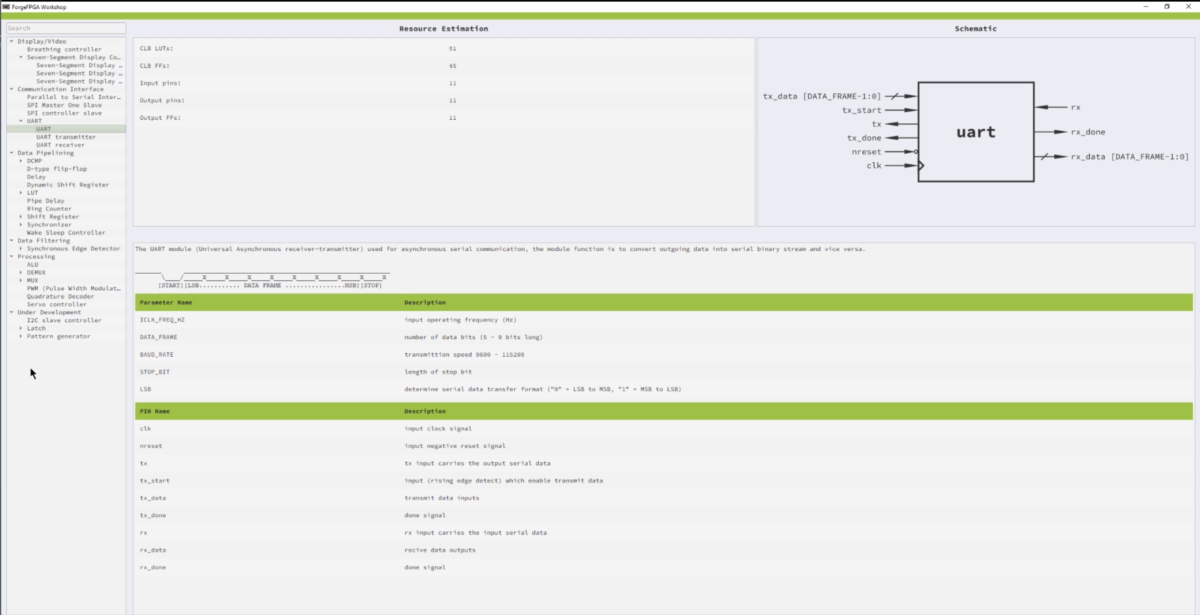

ForgeFPGA-এর জন্য পূর্ব-নির্মিত অ্যাপ্লিকেশন ব্লকগুলির একটি আকর্ষণীয় একটি রয়েছে যা ফ্লেক্স লজিক্সের জিওফ টেট উল্লেখ করেছেন: একটি UART। যুক্তিবিদ্যায় একটি UART তৈরি করা এতটা কঠিন নয়, তবে দেখা যাচ্ছে যে প্রত্যেকে এটিকে ভিন্নভাবে নিয়ে গেছে, এবং এটি কয়েকটি বিচ্ছিন্ন চিপগুলির চেয়ে বেশি হওয়ার জন্য যথেষ্ট যুক্তি। একটি ForgeFPGA হল পুনঃকনফিগারযোগ্য যুক্তির একটি অংশ যা সেই সমস্যার সমাধান করতে পারে, একটি হার্ডওয়্যার বাস্তবায়নকে বিভিন্ন কনফিগারেশনের জন্য দ্রুত মানিয়ে নিতে দেয়।

Flex Logix EFLX 1K eFPGA টাইল দিয়ে কী করা যেতে পারে তার একটি উদাহরণ ForgeFPGA। ফ্লেক্স লজিক্স বিভিন্ন প্রসেস নোডের জন্য আইপিকে মানিয়ে নিতে পারে এবং মিক্স-এন্ড-ম্যাচ টাইলিং ক্ষমতা স্কেলেবিলিটি অফার করে। এটি কম-পাওয়ার প্রোগ্রামেবল লজিকের জন্য নতুন লো অর্জন করে এবং চিপ নির্মাতাদের উল্লেখযোগ্য উপায়ে সমাধানগুলিকে আলাদা করতে দেয়। আরও তথ্যের জন্য, অনুগ্রহ করে দেখুন:

এছাড়াও পড়ুন:

eFPGAs PQC এর সাথে SoCs-এর জন্য ক্রিপ্টো-চপলতা পরিচালনা করছে

ফ্লেক্স লজিক্স: শিল্পের প্রথম এআই ইন্টিগ্রেটেড মিনি-আইটিএক্স ভিত্তিক সিস্টেম

ইএফপিজিএ প্ল্যাটফর্ম সুরক্ষিত করতে অভ্যন্তরীণ আইডি সহ ফ্লেক্স লজিক্স অংশীদার

এর মাধ্যমে এই পোস্টটি ভাগ করুন:

- এসইও চালিত বিষয়বস্তু এবং পিআর বিতরণ। আজই পরিবর্ধিত পান।

- প্লেটোব্লকচেন। Web3 মেটাভার্স ইন্টেলিজেন্স। জ্ঞান প্রসারিত. এখানে প্রবেশ করুন.

- উত্স: https://semiwiki.com/efpga/flex-logix/325926-efpga-goes-back-to-basics-for-low-power-programmable-logic/

- : হয়

- $ ইউপি

- 1

- 2021

- 3d

- a

- ক্ষমতা

- সম্পর্কে

- আইটি সম্পর্কে

- জাতিসংঘের

- অর্জিত

- অধিগ্রহণ

- সক্রিয়

- খাপ খাওয়ানো

- অগ্রসর

- পর

- আক্রমনাত্মক

- AI

- সব

- অনুমতি

- অনুমতি

- এবং

- অন্য

- আবেদন

- At

- পিছনে

- বাধা

- ভিত্তি

- মূলতত্ব

- BE

- মধ্যে

- বিশাল

- বড়

- বাধা

- ব্লক

- তক্তা

- ধার করা

- আনে

- আনীত

- by

- নামক

- CAN

- সক্ষম

- কেন্দ্র

- চ্যালেঞ্জ

- পরীক্ষণ

- চেক

- চিপ

- চিপস

- পছন্দ

- ঘড়ি

- বন্ধ

- জটিল

- কনফিগারেশন

- কর্পোরেট

- মূল্য

- খরচ

- পারা

- দম্পতি

- কভারেজ

- তৈরি করা হচ্ছে

- বর্তমান

- প্রথা

- চক্র

- ডেটিং

- গভীর

- নকশা

- পরিকল্পিত

- ডিজাইনার

- উন্নত

- যন্ত্র

- ডিভাইস

- কথোপকথন

- ভেদ করা

- কঠিন

- ডিজিটাল

- চোবান

- দরজা

- প্রতি

- সম্পাদক

- সক্রিয়

- যথেষ্ট

- প্রবেশ

- পরিবেশ

- যুগ

- ভুল

- মূল্যায়ন

- সবাই

- উদাহরণ

- বহিরাগত

- ব্যয়বহুল

- অন্বেষণ করুণ

- প্রকাশ

- পরিবার

- দ্রুত

- দ্রুত

- বৈশিষ্ট্য

- প্রথম

- নমনীয়তা

- জন্য

- fpga

- থেকে

- উৎপাদিত

- দেয়

- Go

- Goes

- হাতল

- হ্যান্ডলিং

- হার্ডওয়্যারের

- আছে

- উচ্চ

- ঊর্ধ্বতন

- অধিষ্ঠিত

- HTTPS দ্বারা

- ID

- ভাবমূর্তি

- বাস্তবায়ন

- উন্নতি

- in

- সুদ্ধ

- শিল্পের

- সস্তা

- তথ্য

- পরিবর্তে

- সংহত

- মজাদার

- ইন্টারফেস

- ইন্টারফেসগুলি

- স্বকীয়

- ভূমিকা

- বিনিয়োগকারীদের

- IP

- IT

- এর

- JPG

- শুধু একটি

- ল্যাবস

- লাইব্রেরি

- লাইটওয়েট

- মত

- অনেক

- কম

- কমিয়ে

- lows

- ম্যাক্রো

- ম্যাক্রো

- প্রণীত

- প্রস্তুতকর্তা

- ব্যবস্থাপনা

- নির্মাতারা

- ম্যাপিং

- বাজার

- বৃহদায়তন

- পরিণত

- সর্বোচ্চ প্রস্থ

- মন

- মোড

- মোড

- টাকা

- অধিক

- সেতু

- নতুন

- পরবর্তী

- নোড

- of

- নৈবেদ্য

- অর্ঘ

- অফার

- on

- ONE

- খোলা

- অন্যান্য

- অন্যরা

- প্যাকেজ

- প্যাকেজিং

- অংশ

- অংশীদারদের

- যন্ত্রাংশ

- পিনের

- প্ল্যাটফর্ম

- Plato

- প্লেটো ডেটা ইন্টেলিজেন্স

- প্লেটোডাটা

- দয়া করে

- পয়েন্ট

- পোস্ট

- ক্ষমতা

- উপস্থাপন

- উপস্থাপন

- পূর্বে

- মূল্য

- সম্ভবত

- সমস্যা

- প্রক্রিয়া

- প্রক্রিয়াজাতকরণ

- বিশিষ্ট

- স্থাপন

- দ্রুত

- জাতি

- র্যাম

- দ্রুত

- পড়া

- রূপের

- হ্রাস করা

- অসাধারণ

- সরানোর

- স্মৃতিশক্তি

- ঝুঁকি

- রাস্তা

- সড়ক

- ভূমিকা

- স্কেলেবিলিটি

- নিরাপদ

- অর্ধপরিবাহী

- সেট

- শিফট

- সংকেত

- সিলিকোন

- আয়তন

- ঘুম

- ছোট

- ক্ষুদ্রতর

- কোমল

- সলিউশন

- সমাধান

- কিছু

- রাষ্ট্র

- স্ট্রিমলাইনড

- সমর্থন

- কুড়ান

- গ্রহণ করা

- গ্রহণ

- লক্ষ্য

- প্রযুক্তিঃ

- পরীক্ষা

- পরীক্ষামূলক

- যে

- সার্জারির

- তাদের

- এইগুলো

- বার

- থেকে

- টন

- শীর্ষ

- ঐতিহ্যগত

- tsmc

- অধীনে

- ব্যবহারকারী

- ব্যবহারকারী ইন্টারফেস

- বিভিন্ন

- মাধ্যমে

- দেখুন

- আয়তন

- অপেক্ষা করুন

- উপায়

- কি

- যে

- সঙ্গে

- ছাড়া

- হয়া যাই ?

- would

- zephyrnet