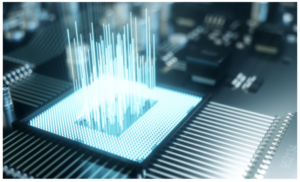

চিপলেটগুলি ডিজাইনের একটি ক্ষেত্রকে সরল করেছে কিন্তু অন্য ফ্রন্টে প্যানডোরার বাক্স খুলেছে। প্রতিটির সিমুলেশন জটিলতা চিপলেট কম কিন্তু এখন চিপলেট থেকে চিপলেট আন্তঃসংযোগ জটিল হয়ে উঠেছে। লোকেরা বিভিন্ন ইন্টারকানেক্ট প্রোটোকল, UCIe এর বিভিন্নতা, UCIe সেটিংস পরিবর্তন, ইন্টারফেসের গতি, শারীরিক স্তরের সংখ্যা এবং আরও একটি নিয়ে পরীক্ষা করছে। এখন AXI এর মত লিগ্যাসি স্ট্যান্ডার্ড, PICe6.0 এর মত নতুন প্রোটোকল এবং মিক্সে ক্যাশে কোহেরেন্সি যোগ করুন।

সর্বোপরি, এটি পরীক্ষার একটি সম্পূর্ণ নতুন সেট তৈরি করে। যার জন্য ঐতিহ্যগত অনুকরণ এবং RTL মডেলিং কাজ করবে না। আপনাকে প্রথমে আর্কিটেকচার ট্রেড-অফের জন্য একটি প্রচেষ্টা ব্যয় করতে হবে, শুধুমাত্র উপাদান নির্বাচন করার জন্য নয়। এর অর্থ হল আপনাকে ট্রাফিক বিশ্লেষণ, অ্যাপ্লিকেশন পার্টিশন, সিস্টেমের আকার এবং বিভিন্ন ধরণের শারীরিক স্তরের প্রভাব পরিচালনা করতে হবে। এছাড়াও, আবেদনের উপর নির্ভর করে বেঞ্চমার্ক খুব আলাদা হবে।

UCIe স্পেসিফিকেশন নতুন এবং কোন স্পষ্ট বেঞ্চমার্ক নেই। এছাড়াও, UCIe স্পেসিফিকেশন শুধুমাত্র লেটেন্সি এবং পাওয়ার বিষয়ে নির্দেশিকা প্রদান করে। উভয়ই কঠোর প্রয়োজনীয়তা। এর মানে হল একটি পাওয়ার-পারফরমেন্স-এরিয়া অধ্যয়ন অনিবার্য। যেহেতু আপনার কাছে প্রোটোকল-প্রটোকল-প্রটোকল রূপান্তর যেমন PCIe 6.0 থেকে UCIe থেকে AXI, মডেলিং সেটআপ জটিল।

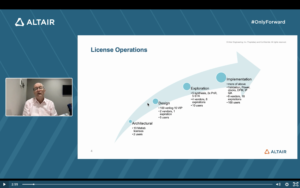

একটি সমাধান হল সিস্টেম-মডেলিং ব্যবহার করে তাকান ভিজ্যুয়ালসিম থেকে মিরাবিলিস ডিজাইন। তারা সম্প্রতি একটি UCIe সিস্টেম-স্তরের আইপি মডেল চালু করেছে এবং আন্তঃসংযোগের বেশ কয়েকটি ব্যবহারের ক্ষেত্রে প্রদর্শন করবে চিপলেট সামিট. ডিজাইনারদের গাইড করার জন্য, তারা প্রচুর ব্যবহারের ক্ষেত্রে, প্রত্যাশিত পাওয়ার-পারফরম্যান্স ফলাফল এবং অপ্টিমাইজেশনের বিকল্পগুলির সাথে একটি গাইড প্রকাশ করেছে। তারা সামিট এ একটি কাগজ উপস্থাপনা এবং একটি বুথ উভয় আছে. আমি তোমাকে সেখানে দেখার আশা করছি!

এছাড়াও, এখানে একটি কাগজের লিঙ্ক রয়েছে যা লোকেরা পেতে পারে: UCIe ইন্টারকানেক্ট আর্কিটেকচারের উপর ভিত্তি করে একটি ভিন্নধর্মী কম্পিউটিং সিস্টেমের পারফরম্যান্স মডেলিং

সারাংশ:

লিড-এজ নোডের আজকের জটিল চিপ ডিজাইনে সাধারণত একাধিক ডাই (বা চিপলেট) থাকে। পদ্ধতিটি বিভিন্ন প্রস্তুতকারক বা প্রসেস, সেইসাথে পুনঃব্যবহারযোগ্য আইপি থেকে মৃত্যুর জন্য অনুমতি দেয়। এই ধরনের জটিল পরিস্থিতিতে বিভিন্ন বাস্তবায়নের মূল্যায়ন করার জন্য ডিজাইনারদের একটি সিস্টেম স্তরের মডেল প্রয়োজন।

একটি উদাহরণ সিস্টেমের মধ্যে রয়েছে একটি I/O চিপলেট, লো পাওয়ার কোর চিপলেট, হাই-পারফরম্যান্স কোর চিপলেট, অডিও-ভিডিও চিপলেট এবং এনালগ চিপলেট, ইউনিভার্সাল চিপলেট ইন্টারকানেক্ট এক্সপ্রেস (UCIe) স্ট্যান্ডার্ড ব্যবহার করে আন্তঃসংযুক্ত।

আমাদের দল উন্নত এবং মানক প্যাকেজ, বিভিন্ন ট্র্যাফিক প্রোফাইল এবং সংস্থান সহ বেশ কয়েকটি পরিস্থিতি এবং কনফিগারেশন বিবেচনা করেছে এবং সময়সীমার সময়ে ইভেন্টগুলির পৌঁছানোর এবং মূল্যায়ন করার জন্য একটি রিটাইমার। মিশন অ্যাপ্লিকেশনগুলির জন্য UCIe আন্তঃসংযোগের শক্তি এবং দুর্বলতাগুলি সনাক্ত করা আমাদের কার্যক্ষমতা, শক্তি এবং কার্যকরী প্রয়োজনীয়তাগুলি পূরণ করার জন্য প্রতিটি সাবসিস্টেমের জন্য সর্বোত্তম কনফিগারেশন পেতে সহায়তা করেছে।

মিরাবিলিস ডিজাইন ইনকর্পোরেটেড সম্পর্কে

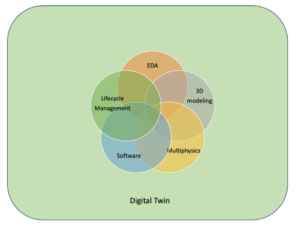

মিরাবিলিস ডিজাইন হল একটি সিলিকন ভ্যালি সফ্টওয়্যার কোম্পানি, পণ্যের স্পেসিফিকেশনে ঝুঁকি শনাক্ত করতে এবং দূর করার জন্য সফ্টওয়্যার এবং প্রশিক্ষণের সমাধান প্রদান করে, পণ্যটি বিকাশের জন্য প্রয়োজনীয় মানব ও সময় সম্পদের সঠিক ভবিষ্যদ্বাণী করে এবং বিভিন্ন প্রকৌশলের মধ্যে যোগাযোগ উন্নত করে।

দল.

VisualSim আর্কিটেক্ট মডেল নির্মাণ, সিমুলেশন, বিশ্লেষণ এবং RTL যাচাইকরণকে উল্লেখযোগ্যভাবে উন্নত করতে বুদ্ধিবৃত্তিক সম্পত্তি, সিস্টেম-স্তরের মডেলিং, সিমুলেশন, পরিবেশ বিশ্লেষণ এবং অ্যাপ্লিকেশন টেমপ্লেটগুলিকে একত্রিত করে। পরিবেশ ডিজাইনারদের দ্রুত একটি ডিজাইনে একত্রিত হতে সক্ষম করে যা পরস্পর নির্ভরশীল সময় এবং শক্তির প্রয়োজনীয়তার বিভিন্ন সেট পূরণ করে। এটি ডিজাইন প্রক্রিয়ার খুব প্রথম দিকে লিখিত স্পেসিফিকেশনের সাথে সমান্তরালভাবে (এবং একটি সহায়তা হিসাবে) ব্যবহার করা হয় এবং পণ্যটির বাস্তবায়নের আগে (উদাহরণস্বরূপ, RTL, সফ্টওয়্যার কোড, বা পরিকল্পিত)।

এছাড়াও পড়ুন:

ওয়েবিনার: আর্কিটেকচার অন্বেষণের সময় কীভাবে 95%+ সঠিক শক্তি পরিমাপ অর্জন করা যায়

হার্ডওয়্যার আর্কিটেকচারে SysML ম্যাপিং

শিক্ষার্থীদের জন্য মডেল-ভিত্তিক ডিজাইন কোর্স

এর মাধ্যমে এই পোস্টটি ভাগ করুন:

- এসইও চালিত বিষয়বস্তু এবং পিআর বিতরণ। আজই পরিবর্ধিত পান।

- PlatoData.Network উল্লম্ব জেনারেটিভ Ai. নিজেকে ক্ষমতায়িত করুন। এখানে প্রবেশ করুন.

- প্লেটোএআইস্ট্রিম। Web3 ইন্টেলিজেন্স। জ্ঞান প্রসারিত. এখানে প্রবেশ করুন.

- প্লেটোইএসজি। কার্বন, ক্লিনটেক, শক্তি, পরিবেশ সৌর, বর্জ্য ব্যবস্থাপনা. এখানে প্রবেশ করুন.

- প্লেটো হেলথ। বায়োটেক এবং ক্লিনিক্যাল ট্রায়াল ইন্টেলিজেন্স। এখানে প্রবেশ করুন.

- উত্স: https://semiwiki.com/ip/mirabilis-design-ip/341339-chiplets-open-pandoras-box/

- : আছে

- : হয়

- :না

- a

- সঠিক

- সঠিক

- অর্জন করা

- যোগ

- অগ্রসর

- চিকিত্সা

- অনুমতি

- বরাবর

- এছাড়াও

- an

- বিশ্লেষণ

- এবং

- অন্য

- আবেদন

- অ্যাপ্লিকেশন

- অভিগমন

- স্থাপত্য

- রয়েছি

- এলাকায়

- AS

- At

- ভিত্তি

- BE

- পরিণত

- আগে

- উচ্চতার চিহ্ন

- benchmarks

- মধ্যে

- উভয়

- বক্স

- কিন্তু

- ক্যাশে

- CAN

- পেতে পারি

- মামলা

- চিপ

- পরিষ্কার

- কোড

- সম্মিলন

- যোগাযোগ

- কোম্পানি

- সম্পূর্ণরূপে

- জটিল

- জটিলতা

- উপাদান

- কম্পিউটিং

- আচার

- কনফিগারেশন

- বিবেচিত

- গঠিত

- নির্মাণ

- একত্রিত করা

- পরিবর্তন

- মূল

- গতিপথ

- সৃষ্টি

- প্রদর্শক

- নির্ভর করে

- নকশা

- নকশা প্রক্রিয়া

- ডিজাইনার

- ডিজাইন

- বিকাশ

- বিভিন্ন

- বিচিত্র

- সময়

- প্রতি

- গোড়ার দিকে

- প্রচেষ্টা

- বাছা

- অনুকরণ

- সম্ভব

- পরিবেশ

- মূল্যায়ন

- ঘটনাবলী

- উদাহরণ

- প্রত্যাশিত

- পরীক্ষা নিরীক্ষা

- পরীক্ষা-নিরীক্ষা

- প্রকাশ করা

- প্রসারিত করা

- প্রথম

- জন্য

- থেকে

- সদর

- কার্মিক

- সাধারণত

- পাওয়া

- গুগল

- পথপ্রদর্শন

- কৌশল

- হার্ডওয়্যারের

- আছে

- সাহায্য

- এখানে

- উচ্চ পারদর্শিতা

- আশা

- কিভাবে

- কিভাবে

- HTTPS দ্বারা

- মানবীয়

- i

- সনাক্ত করা

- চিহ্নিতকরণের

- প্রভাব

- বাস্তবায়ন

- বাস্তবায়নের

- উন্নত করা

- in

- সুদ্ধ

- বুদ্ধিজীবী

- বুদ্ধিজীবী সম্পত্তি

- আন্তঃসংযুক্ত

- ইন্টারফেস

- IP

- IT

- JPG

- মাত্র

- অদৃশ্যতা

- চালু

- স্তর

- স্তর

- উত্তরাধিকার

- উচ্চতা

- মত

- LINK

- দেখুন

- প্রচুর

- কম

- নিম্ন

- নির্মাতারা

- সর্বোচ্চ প্রস্থ

- গড়

- মানে

- মাপা

- সম্মেলন

- পূরণ

- মিশন

- মিশ্রিত করা

- মডেল

- মূর্তিনির্মাণ

- মূর্তিনির্মাণ

- বহু

- প্রয়োজন

- নতুন

- না।

- নোড

- এখন

- সংখ্যা

- প্রাপ্ত

- of

- on

- ONE

- কেবল

- খোলা

- খোলা

- অনুকূল

- অপ্টিমাইজেশান

- অপশন সমূহ

- or

- প্যাকেজ

- কাগজ

- সমান্তরাল

- কর্মক্ষমতা

- শারীরিক

- Plato

- প্লেটো ডেটা ইন্টেলিজেন্স

- প্লেটোডাটা

- পোস্ট

- ক্ষমতা

- পূর্বাভাসের

- উপহার

- প্রক্রিয়া

- প্রসেস

- পণ্য

- প্রোফাইল

- সম্পত্তি

- প্রোটোকল

- উপলব্ধ

- প্রদানের

- প্রকাশিত

- দ্রুত

- নাগাল

- পড়া

- সম্প্রতি

- প্রয়োজনীয়

- আবশ্যকতা

- Resources

- ফলাফল

- পুনর্ব্যবহারযোগ্য

- ঝুঁকি

- পরিস্থিতিতে

- দেখ

- নির্বাচন

- সেট

- সেটিংস

- সেটআপ

- বিভিন্ন

- উল্লেখযোগ্যভাবে

- সিলিকোন

- সিলিকন ভ্যালি

- সরলীকৃত

- ব্যাজ

- পরিস্থিতিতে

- So

- সফটওয়্যার

- সমাধান

- সলিউশন

- সবিস্তার বিবরণী

- গতি

- ব্যয় করা

- মান

- মান

- শক্তি

- কঠোর

- অধ্যয়ন

- এমন

- শিখর

- পদ্ধতি

- টীম

- টেমপ্লেট

- যে

- সার্জারির

- সেখানে।

- তারা

- এই

- সময়

- থেকে

- ঐতিহ্যগত

- ট্রাফিক

- প্রশিক্ষণ

- ধরনের

- সার্বজনীন

- us

- ব্যবহার

- ব্যবহৃত

- ব্যবহার

- উপত্যকা

- বৈচিত্র

- প্রতিপাদন

- খুব

- মাধ্যমে

- দুর্বলতা

- আমরা একটি

- যে

- ইচ্ছা

- সঙ্গে

- হয়া যাই ?

- লিখিত

- আপনি

- zephyrnet