لقد عادت 1991 أعلنت شركة Cadence لأول مرة عن اسم منتج Virtuoso، وها نحن الآن بعد مرور 32 عامًا والمنتج على قيد الحياة ويعمل بشكل جيد. أعطاني ستيفن لويس من شركة Cadence تحديثًا بشأن شيء جديد يسمونه ستوديو الموهوب، والأمر كله يتعلق بتصميم IC مخصص للعالم الحقيقي. في تلك السنوات الـ 32، شهدنا مسيرة عملية أشباه الموصلات وفقًا لقانون مور من 600 نانومتر باستخدام CMOS المستوي، وتقليص حجمها إلى عصر FinFET أقل من 22 نانومتر، لتصل إلى GAA عند عقدة 3 نانومتر. من الواضح أن متطلبات أداة EDA قد تغيرت حيث جلبت العقد الأصغر تأثيرات فيزيائية جديدة كانت بحاجة إلى نمذجتها ومحاكاتها لضمان نجاح السيليكون الأول.

ينصب تركيز Cadence Virtuoso Studio على مساعدة مصممي IC على مواجهة تحديات الوقت الحاضر من خلال ستة مجالات:

- زيادة تعقيد العملية

- التعامل مع 10,000 ثانية من محاكاة الدوائر

- أتمتة التصميم وترحيل الدوائر

- التكامل غير المتجانس

- AI

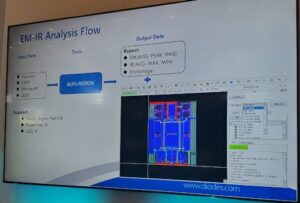

- تسجيل الخروج والتحقق من التصميم والتحليل

• الموهوب ADE (بيئة التصميم التناظري) تسمح لمهندسي الدوائر باستكشاف تصميماتهم التناظرية والإشارات المختلطة وRFIC من خلال الالتقاط التخطيطي ومحاكاة الدوائر. تم تجديد بنية Virtuoso ADE لتحسين التحكم في الوظائف، وتقليل استخدام ذاكرة الوصول العشوائي (RAM)، وتسريع عمليات المحاكاة باستخدام السحابة. على سبيل المثال، تم تقليل ذاكرة الوصول العشوائي المطلوبة لتشغيل Spectre على 10,000 ثانية من عمليات المحاكاة من 420 ميجابايت إلى 18 ميجابايت فقط لمراقبة المحاكاة، بينما انخفضت تقييمات التعبير من 420 ميجابايت من ذاكرة الوصول العشوائي إلى 280 ميجابايت فقط.

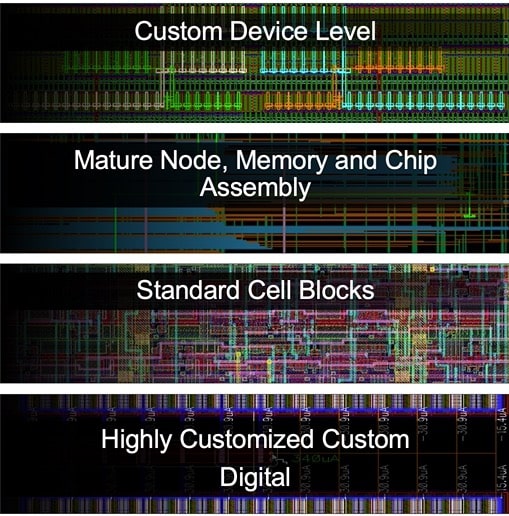

تحديثات لل جناح تخطيط الموهوب تتضمن أربعة اختيارات لتقنية المكان والطريق، كل منها يناسب المهمة الفريدة التي تقوم بها من خلال بيئة Virtuoso:

أربع تقنيات P&R

يعد تشغيل DRC وLVS جزءًا من التحقق المادي، ويؤدي تشغيلها في الوضع الدفعي، والإصلاح والتكرار، إلى جداول تطوير طويلة. يسمح التحقق داخل التصميم بالاستخدام التفاعلي لـ DRC وLVS أثناء العمل على تخطيط IC، لذلك يتم تسليط الضوء بسرعة على التعليقات حول ما يجب تغييره، مما يؤدي إلى تسريع الإنتاجية. يستفيد مصمم التخطيط الذي يستخدم Virtuoso Layout Suite من التحقق داخل التصميم باستخدام بيغاسوس تكنولوجيا جمهورية الكونغو الديمقراطية وLVS.

تمتد الشرائح الصغيرة والتعبئة 2.5D و3D إلى العوالم المنفصلة تقليديًا لمجالات تصميم ثنائي الفينيل متعدد الكلور والحزمة وIC. يتيح Virtuoso Studio إمكانية التصميم المشترك والتحقق من الحزم والوحدات والدوائر المرحلية من خلال:

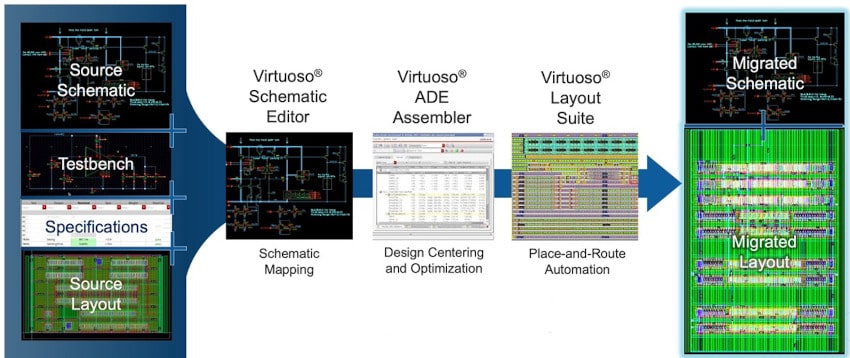

وبالنظر إلى المستقبل القريب، يمكنك أن تتوقع ظهور تفاصيل حول كيفية تطبيق الذكاء الاصطناعي للانتقال تلقائيًا من مخطط تناظري إلى تخطيط استنادًا إلى التعلم الآلي والمواصفات. ستعمل هذه التخطيطات التجريبية التي تم إنشاؤها تلقائيًا على تسريع العملية كثيفة العمالة. مجال التطوير الثاني لتطبيق الذكاء الاصطناعي هو مشكلة ترحيل IP التناظري المخصص إلى عقدة عملية جديدة. ابقوا متابعين.

يشمل العملاء الأوائل لـ Virtuoso Studio الأجهزة التناظرية للتصميم المشترك لـ IC والحزمة، والتصميمات الاستهلاكية الرائدة لـ IC في MediaTek، وترحيل العمليات القائمة على الذكاء الاصطناعي في Renesas.

نبذة عامة

لقد وضع Virtuoso Studio في الإصدار 23.1 بعض الميزات الجديدة الرائعة التي يمكن لفرق تصميم IC البدء في استخدامها لتكون أكثر إنتاجية. لقد تغيرت البنية التحتية لـ Virtuoso لمواجهة تحديات قانون مور، وأصبحت عمليات المحاكاة باستخدام محاكاة دوائر 10,000 ثانية عملية، ويتم دعم التصميم المشترك RFIC والوحدة النمطية 2.5D/3D، ويستغرق التحقق من DRC/LVS الداخلي وقتًا أقل بكثير، كما أن الذكاء الاصطناعي يتم تطبيقها لأتمتة المهام التناظرية.

مدونات ذات الصلة

شارك هذا المنشور عبر:- محتوى مدعوم من تحسين محركات البحث وتوزيع العلاقات العامة. تضخيم اليوم.

- بلاتوبلوكشين. Web3 Metaverse Intelligence. تضخيم المعرفة. الوصول هنا.

- سك المستقبل مع أدرين أشلي. الوصول هنا.

- المصدر https://semiwiki.com/eda/327556-whats-new-with-cadence-virtuoso/

- :لديها

- :يكون

- $ UP

- 1

- 10

- 3d

- a

- من نحن

- تسريع

- AI

- الكل

- يسمح

- على طول

- و

- أعلن

- تطبيقي

- هندسة معمارية

- هي

- المنطقة

- المناطق

- AS

- At

- أتمتة

- تلقائيا

- أتمتة

- الى الخلف

- على أساس

- BE

- كان

- يجري

- أقل من

- الفوائد

- أفضل

- جلبت

- by

- إيقاع

- دعوة

- CAN

- أسر

- التحديات

- تغيير

- الخيارات

- بوضوح

- سحابة

- مستهلك

- مراقبة

- على

- العملاء

- يوم

- مطالب

- تصميم

- مصمم

- المصممين

- تصاميم

- تفاصيل

- التطوير التجاري

- الأجهزة

- فعل

- المجالات

- إلى أسفل

- كل

- الآثار

- تمكن

- المهندسين

- ضمان

- البيئة

- عصر

- التقييمات

- مثال

- توقع

- اكتشف

- المميزات

- ردود الفعل

- الاسم الأول

- تركز

- في حالة

- أربعة

- تبدأ من

- إضافي

- مستقبل

- Go

- يد

- يملك

- مساعدة

- هنا

- سلط الضوء

- كيفية

- HTML

- HTTPS

- ICS

- مثير للإعجاب

- in

- تتضمن

- البنية التحتية

- التفاعلية

- IP

- وظيفة

- JPG

- عمل

- القانون

- تصميم

- يؤدي

- تعلم

- رافعة الحجارة

- طويل

- آلة

- آلة التعلم

- مارس

- ماكس العرض

- تعرف علي

- هجرة

- موضة

- وحدة

- الوحدات

- مراقبة

- الأكثر من ذلك

- الاسم

- قرب

- بحاجة

- جديد

- مزايا جديدة

- العقدة

- العقد

- of

- on

- ONE

- صفقة

- حزم

- التعبئة والتغليف

- جزء

- مادي

- المكان

- أفلاطون

- الذكاء افلاطون البيانات

- أفلاطون داتا

- منشور

- عملية

- يقدم

- المشكلة

- عملية المعالجة

- منتج

- مثمر

- إنتاجية

- وضع

- بسرعة

- رامات

- الوصول إلى

- حقيقي

- العالم الحقيقي

- عقار مخفض

- تقليص

- الافراج عن

- مطلوب

- طريق

- يجري

- تشغيل

- التحجيم

- الثاني

- انظر التفاصيل

- أشباه الموصلات

- مستقل

- السيليكون

- محاكاة

- SIX

- الأصغر

- So

- بعض

- شيء

- امتداد

- مواصفات

- طيف

- سرعة

- بداية

- إقامة

- ستوديو

- تحقيق النجاح

- جناح

- مدعومة

- أخذ

- يأخذ

- مهمة

- المهام

- فريق

- تكنولوجيا

- أن

- •

- من مشاركة

- تشبه

- عبر

- الوقت

- إلى

- أداة

- تقليديا

- محاكمة

- فريد من نوعه

- تحديث

- الأستعمال

- تستخدم

- التحقق

- بواسطة

- حسن

- ابحث عن

- في حين

- سوف

- مع

- عامل

- العالم

- سنوات

- زفيرنت