أصبحت نمذجة الإشارات المختلطة أكثر أهمية حيث أصبح التفاعل بين الدوائر الرقمية والتناظرية أكثر تشابكًا. يعتمد هذا المستوى من النمذجة بشكل حاسم على نماذج سلوكية دقيقة بما فيه الكفاية ولكنها سريعة للمكونات التناظرية. بول كننغهام (نائب الرئيس الأول/المدير العام، قسم التحقق في Cadence)، وراؤول كامبوسانو (Silicon Catalyst، رجل أعمال، مدير التكنولوجيا السابق في Synopsys والآن Silvaco CTO) وأنا أواصل سلسلتنا حول الأفكار البحثية. كما هو الحال دائما، ردود الفعل موضع ترحيب.

الابتكار

اختيار هذا الشهر هو التحقق السريع من صحة الإشارات المختلطة SoCs. تم تقديم الورقة في مجلة جمعية دوائر الحالة الصلبة لعام 2021. المؤلفون من جامعة ستانفورد، وجامعة سيول الوطنية والنظير العلمي.

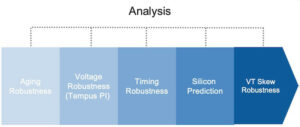

استحوذت مدونة SemiWiki الحديثة حول الإشارات المختلطة على اهتمام هائل، مما يشير إلى أن هذا مجال يستحق المزيد من الدراسة. تتمثل إحدى الخطوات الحاسمة لتحقيق التحقق الفعال من الإشارات المختلطة في تطوير نماذج سلوكية دقيقة متعددة المستويات للوظائف التناظرية التي تكون مناسبة للمحاكاة المستندة إلى الأحداث، وحتى النماذج القابلة للتوليف للنشر في محاكاة الأجهزة. تصف الورقة النهج القائم على القالب لتوليد النماذج وطريقتين لاستكمال السلوك التناظري للاتصالات القائمة على الحدث: الإفراط في أخذ العينات والنمذجة المستندة إلى الحدث باستخدام ناقلات الميزات (نماذج الأعداد الحقيقية).

يوضح المؤلفون التطبيق لمحاكاة الارتباط عالي السرعة ومضاهاته مع نتائج مبهرة. تُظهر المقارنة بين محاكاة Spice وVerilog على ADC تطابقًا وثيقًا في النتائج، وتشغيل أوامر الحجم بشكل أسرع. تضيف النمذجة القائمة على المحاكاة المزيد من الطلبات من حيث الحجم إلى تلك السرعة.

رأي بول

تبادل كبير للسياق هذا الشهر في عالم التحقق التناظري وتقاطع "الإشارات المختلطة" مع التحقق الرقمي. هذه الورقة بحثية مدعوة إلى مجلة مرموقة تلخص بشكل جميل أحدث ما توصلت إليه التكنولوجيا لبناء نماذج مجردة من الدوائر التناظرية التي يمكنها مواكبة المحاكاة الرقمية، حتى على المحاكي، وتفعل ذلك بدقة مذهلة.

في العالم التناظري، يكون كل شيء سلسًا ومتأرجحًا عادةً، مع وصف السلوك المقصود للمدخلات والمخرجات من خلال تحويل أشكال موجية المدخلات والمخرجات أولاً إلى مجال التردد. المعيار الذهبي للمحاكاة التناظرية هو سبايس، الذي يقوم بشكل متكرر بحل المعادلات التفاضلية على مستوى الجهاز للجهود في جميع النقاط في الدائرة ضمن تفاوتات الخطأ المضمونة. بالمقارنة مع المحاكاة الرقمية، فإن Spice أبطأ بآلاف المرات.

الطريقة النموذجية لإنشاء نماذج تناظرية مجردة سريعة هي القيام بأخذ عينات زمنية منفصلة لشكل موجة الإدخال ثم إنشاء شكل موجة إخراج عينات زمنية منفصلة مناسبة باستخدام بعض المنطق المشابه لـ DSP (مثل مرشحات الوقت المنفصلة). يمكن إنشاء قيم الإشارة بين هذه النقاط الزمنية المنفصلة إذا لزم الأمر باستخدام الاستيفاء الخطي أو المستند إلى الشريحة.

يقدم المؤلفون إطارًا كاملاً مفتوح المصدر مع لغة إنشاء نماذج أنيقة ومترجم لإنشاء نماذج قابلة للمحاكاة وقابلة للمحاكاة من هذه اللغة. إنهم يستخدمون طريقة أخذ العينات ذات الخطوات الزمنية التكيفية مع الاستيفاء القائم على الشريحة ويعملون من خلال دراسة حالة موثوقة باستخدام إطار العمل الخاص بهم على وصلة SERDES PHY عالية السرعة مقاس 16 نانومتر. يؤدي الانتقال من Spice إلى المحاكاة الرقمية المعتمدة على وحدة المعالجة المركزية (CPU) بنماذجها المجردة إلى تحقيق سرعة تصل إلى 13,000x. أدى وضع النماذج على FPGA إلى زيادة السرعة بمقدار 300 مرة أخرى. لطيف - جيد.

رأي راؤول

يمثل التحقق من صحة الإشارات المختلطة على SoCs تحديًا، من بين أمور أخرى، لأن تشغيل ناقلات اختبار كافية للتحقق من صحة الأجزاء الرقمية - عادةً باستخدام محاكي يحركه الحدث أو على محاكي - يؤدي إلى أوقات باهظة لمحاكاة الجزء التناظري باستخدام محاكي الدائرة. الحل هو إنشاء نماذج سلوكية تمثيلية. تستعرض ورقة هذا الشهر العديد من الأساليب لإنشاء هذه النماذج وتقدم ما يعتقد المؤلفون أنه أول إطار كامل مفتوح المصدر لمحاكاة AMS. هذه ورقة بحثية مدعوة إلى مجلة IEEE المفتوحة لجمعية دوائر الحالة الصلبة، وعلى هذا النحو تُقرأ المقاطع الكبيرة مثل برنامج تعليمي حول التصميم التناظري والتحقق من الصحة. إنه مختلف تمامًا عما فعلناه من قبل في هذه المدونة؛ يحتاج القارئ إلى بعض المعرفة التناظرية حتى يتمكن من الاستفادة الكاملة (على سبيل المثال، مجال لابلاس، تحويل z، PLL، مُحرف الطور، معدلات نيكويست، الارتعاش، وما إلى ذلك).

تتلقى النماذج الوظيفية للدوائر التناظرية المدخلات وتولد المخرجات في أوقات منفصلة. يمكن نمذجة الأشكال الموجية باستخدام دوال خطية متعددة التعريف أو ثابتة متعددة التعريف، باستخدام نقاط المفتاح (النهج المستخدم في هذه الورقة) أو مجموع الدوال الأسية المعقدة. يتم تصميم الوقت على أنه وقت منفصل (عينة أو زائدة عن الحاجة) أو كنموذج خطي متعدد التعريف (يستخدم هنا). يتم تجميع النماذج الفعلية للدوائر من مكتبة القوالب. قام المؤلفون بتجميع كل هذا معًا في نظام يتكون من: 1) أداة بايثون لإنشاء نماذج AMS قابلة للتوليف، مما يوفر مجموعة من الوظائف التي تسمح للمستخدمين بوصف كتل AMS كمعادلات تفاضلية، أو قوائم netlist، أو وظائف نقل، أو أنظمة مبدلة، ... في أي منهما نقطة ثابتة أو عائمة، و2) تجريد يشبه المحاكاة للوحات FPGA.. والذي يوفر بنية تحتية للمحاكاة تدير الخطوة الزمنية للمحاكاة وسرعة ساعة المحاكاة وواجهات الاختبار وتولد تدفق بت لمحاكاة FPGA بمساعدة أدوات EDA.

الحيلة لا تكمن في استخدام محاكاة الدوائر، بل في استبدال نماذج الدوائر بنماذج وظيفية. بالنسبة لمستقبل الارتباط عالي السرعة المسمى DragonPHY، تبلغ سرعة محاكاة Verilog مقابل محاكاة Spice 12,800x، مما يوفر دقة كافية. ولكن حتى هذا التسريع ليس كافيًا لمحاكاة استعادة الساعة وحلقات معادلة القناة، لاختبار معدلات خطأ البتات (BER)، مع حلقات ردود الفعل التي قد تستغرق 100,000 ثانية من الدورات حتى تستقر. يؤدي تعديل النماذج بحيث تكون قابلة للتوليف ويمكن دمجها في المحاكاة إلى توفير سرعة إضافية تصل إلى 5000x، وهو ما يكفي لحساب معدل الخطأ في البتات (BER) في حدود 7.5%. بديع!

اقرأ أيضا:

التوليف التأكيدي من خلال LLM. الابتكار في التحقق

يقوم Cadence Tensilica بتدوير الترقية التالية إلى بنية LX

كفاءة الاستدلال في الأداء والطاقة والمساحة وقابلية التوسع

شارك هذا المنشور عبر:

- محتوى مدعوم من تحسين محركات البحث وتوزيع العلاقات العامة. تضخيم اليوم.

- PlatoData.Network Vertical Generative Ai. تمكين نفسك. الوصول هنا.

- أفلاطونايستريم. ذكاء Web3. تضخيم المعرفة. الوصول هنا.

- أفلاطون كربون، كلينتك ، الطاقة، بيئة، شمسي، إدارة المخلفات. الوصول هنا.

- أفلاطون هيلث. التكنولوجيا الحيوية وذكاء التجارب السريرية. الوصول هنا.

- المصدر https://semiwiki.com/eda/336610-developing-effective-mixed-signal-models-innovation-in-verification/

- :يكون

- :ليس

- $ UP

- 1

- 100

- 12

- 13

- 2021

- 300

- 7

- a

- ماهرون

- الملخص

- التجريد

- دقة

- دقيق

- يحقق

- يقدم

- على التكيف

- يضيف

- الكل

- يسمح

- دائما

- من بين

- an

- و

- آخر

- تطبيق

- نهج

- اقتراب

- مناسب

- هي

- المنطقة

- AS

- تجميعها

- At

- الكتاب

- BE

- جميل

- لان

- أصبح

- أن تصبح

- قبل

- سلوك

- اعتقد

- تستفيد

- ما بين

- قطعة

- Blocks

- المدونة

- على حد سواء

- نساعدك في بناء

- لكن

- by

- إيقاع

- تسمى

- CAN

- القبض

- حقيبة

- دراسة حالة

- الحفاز

- تحدى

- قناة

- ساعة حائط

- اغلاق

- عن كثب

- مقارنة

- مقارنة

- إكمال

- مجمع

- مكونات

- إحصاء

- التواصل

- تتكون

- ثابت

- استمر

- خلق

- خلق

- خلق

- معقول

- حرج

- CTO

- دورات

- شرح

- يعتمد

- نشر

- وصف

- وصف

- تصميم

- تطوير

- تطوير

- مختلف

- رقمي

- do

- نطاق

- فعل

- مدفوع

- e

- الطُرق الفعّالة

- كفاءة

- إما

- ضخم

- كاف

- ريادي

- معادلات

- خطأ

- إلخ

- حتى

- الحدث/الفعالية

- كل شىء

- الأسي

- FAST

- أسرع

- الميزات

- ردود الفعل

- مرشحات

- الاسم الأول

- ثابت

- يطفو على السطح

- في حالة

- سابق

- FPGA

- الإطار

- تردد

- تبدأ من

- تماما

- وظيفي

- وظائف

- إضافي

- أعطى

- توليد

- ولدت

- يولد

- توليد

- جيل

- الذهاب

- ذهبي

- معيار الذهب

- خير

- مضمون

- أجهزة التبخير

- يملك

- مساعدة

- هنا

- مرتفع

- HTTPS

- i

- الأفكار

- IEEE

- if

- أهمية

- مثير للإعجاب

- in

- الاشتقاق

- البنية التحتية

- الابتكار

- إدخال

- المدخلات

- معد

- تفاعل

- مصلحة

- واجهات

- تقاطع طرق

- تتشابك

- إلى

- دعوة

- IT

- انها

- مجلة

- احتفظ

- لغة

- كبير

- مستوى

- المكتبة

- مثل

- LINK

- منطق

- يدير

- ماكس العرض

- مايو..

- طريقة

- طرق

- مختلط

- نموذج

- تصميم

- عارضات ازياء

- شهر

- الأكثر من ذلك

- محليات

- بحاجة

- إحتياجات

- جديد

- التالي

- رحلة جميلة

- الآن

- عدد

- of

- غالبا

- on

- جاكيت

- المصدر المفتوح

- or

- الطلبات

- أخرى

- لنا

- الناتج

- النتائج

- ورق

- جزء

- أجزاء

- بول

- أداء

- مرحلة جديدة

- اختيار

- أفلاطون

- الذكاء افلاطون البيانات

- أفلاطون داتا

- البوينت

- نقاط

- منشور

- قوة

- يقدم

- قدم

- الهدايا

- المرموقة

- ويوفر

- توفير

- وضع

- وضع

- بايثون

- تماما

- الأجور

- بدلا

- عرض

- قارئ

- حقيقي

- أدرك

- تسلم

- الأخيرة

- استرجاع

- بحث

- النتائج

- التعليقات

- تشغيل

- علمي

- كبير

- سيول

- مسلسلات

- طقم

- حل

- عدة

- يظهر

- سيجنل

- السيليكون

- محاكاة

- محاكاة

- كمنعم

- So

- جاليات

- حل

- حل

- بعض

- سرعة

- تابل

- يدور

- معيار

- ستانفورد

- دولة من بين الفن

- خطوة

- دراسة

- هذه

- كاف

- مناسب

- مسائل حسابية

- تحول

- تركيب

- نظام

- أنظمة

- أخذ

- النماذج

- تجربه بالعربي

- أن

- •

- العالم

- من مشاركة

- then

- تشبه

- هم

- الأشياء

- الآلاف

- عبر

- الوقت

- مرات

- إلى

- سويا

- أداة

- أدوات

- تحويل

- تحويل

- البرنامج التعليمي

- اثنان

- نموذجي

- عادة

- جامعة

- ترقية

- تستخدم

- مستعمل

- المستخدمين

- استخدام

- عادة

- التحقق من صحة

- التحقق من صحة

- القيم

- التحقق

- مقابل

- بواسطة

- وكان

- we

- ترحيب

- ابحث عن

- التي

- مع

- في غضون

- للعمل

- العالم

- قيمة

- حتى الآن

- زفيرنت