عندما تفكر في "FPGA" ، ما الذي يتبادر إلى الذهن؟ أجزاء ضخمة ومكلفة قادرة على تحمل الكثير من المنطق ولكنها تستهلك أيضًا قدرًا كبيرًا من الطاقة. منصات قابلة لإعادة التكوين يمكنها ابتلاع RTL لتصميم SoC في اختبار ما قبل السيليكون. عمليات استحواذ كبيرة على الشركات حيث جنى المستثمرون الكثير من المال. عبوات ثلاثية الأبعاد غريبة ووصلات متطورة. ولكن ربما ليست غير مكلفة ، حزمة صغيرة ، عدد دبوس منخفض ، أجزاء طاقة احتياطية منخفضة ، أليس كذلك؟ يعود eFPGA من Flex Logix إلى أساسيات المنطق القابل للبرمجة منخفض الطاقة والذي يمكن أن يتحمل تكلفة أقل وحجمًا أكبر وأجهزة محدودة الحجم.

قدم طريقان قابلان للبرمجة خيارًا

في خطر التعارف مع نفسي ، عاد تعرضي الأول لما كان يُطلق عليه آنذاك تقنية FPGA عندما أخرجت Altera عائلة EP1200 المستندة إلى EPROM في حزمة DIP ذات 40 سنًا بساعة 16 ميجاهرتز ، و 400 ميغاواط من الطاقة النشطة و 15 ميغاواط في وضع الاستعداد قوة. لقد جاء مع محرر تخطيطي ومكتبة من وحدات الماكرو للبوابة. كان المصممون يرسمون منطقهم ، "يحرقون" أجزاءهم ، ويختبرونها ، ويرمونها تحت مصباح الأشعة فوق البنفسجية ويمحوها إذا لم ينجح ، ثم يحاولون مرة أخرى.

بعد فترة وجيزة ، ظهرت لوحة في مختبراتنا الأخرى مع بعض من أول Xilinx FPGAs. كانت هذه تستند إلى ذاكرة الوصول العشوائي بدلاً من القائمة على EPROM - أكبر وأسرع وإعادة البرمجة دون انتظار مصباح الأشعة فوق البنفسجية أو إزالة الجزء من اللوحة. كان المنطق الداخلي أيضًا أكثر تعقيدًا ، مع إدخال المضاعفات السريعة. لا يمكن لهذه الأجزاء أن تكتسح المنطق فحسب ، بل يمكن أيضًا استخدامها لاستكشاف قدرة معالجة الإشارات الرقمية المخصصة مع دورات إعادة التصميم السريعة.

أدى ذلك إلى بدء سباق التسلح بالسيليكون القابل للبرمجة ، وتم تطوير تشعب بين PLD - جهاز منطقي قابل للبرمجة - و FPGA. اتخذ المصنعون خيارات ، مع اتخاذ Altera و Xilinx الطريق السريع لقابلية توسيع FPGA واتخذ Actel و Lattice وآخرون الطريق السفلي لمرونة PLD لـ "منطق الغراء" لتقليل تكاليف فاتورة المواد.

يغير eFPGA المعادلة المنطقية القابلة للبرمجة منخفضة الطاقة

كل هذا يبدو وكأنه سوق ناضجة ، مع وجود حاجز كبير للدخول من جهة وعرض أكثر سلعة من جهة أخرى. ولكن ماذا لو كان المنطق القابل للبرمجة عبارة عن كتلة IP يمكن تصميمها في أي شريحة في هذا العصر الخالي من fabless - بما في ذلك FPGA صغير منخفض الطاقة؟ من شأن ذلك الالتفاف على الحاجز (على الأقل في العروض المنخفضة والمتوسطة المدى) والتسليع.

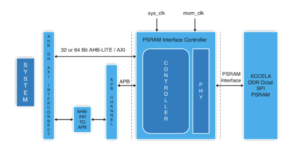

واجه Flex Logix هذا التحدي باستخدام بلاط EFLX 1K eFPGA. يحتوي كل مربع منطقي على 560 جدول بحث من ستة مدخلات (LUTs) مع ذاكرة الوصول العشوائي وتسجيل الوقت والتوصيل البيني. يعطي ترتيب مربعات EFLX القدرة على التعامل مع مختلف الأدوار المنطقية و DSP. لكن أبرز ميزاته قد يكون حجمه وإدارة طاقته.

بلاط EFLX 40K المعبأ في TSMC 1ULP يناسب 1.5 مم2 ويوفر بوابة الطاقة لأوضاع النوم العميق مع الاحتفاظ بالحالة - أكثر عدوانية بكثير من أجهزة PLD التقليدية. تحتوي EFLX 1K أيضًا على ميزات جاهزة للإنتاج مستعارة من FPGAs. يقدم واجهات AXI أو JTAG لتكوين تدفق البتات ، ودائرة إعادة التشغيل التي تتيح التحقق من الأخطاء بشكل بسيط ، ووضع اختبار مع متجهات مبسطة تعمل على تحسين التغطية وتقليل أوقات الاختبار.

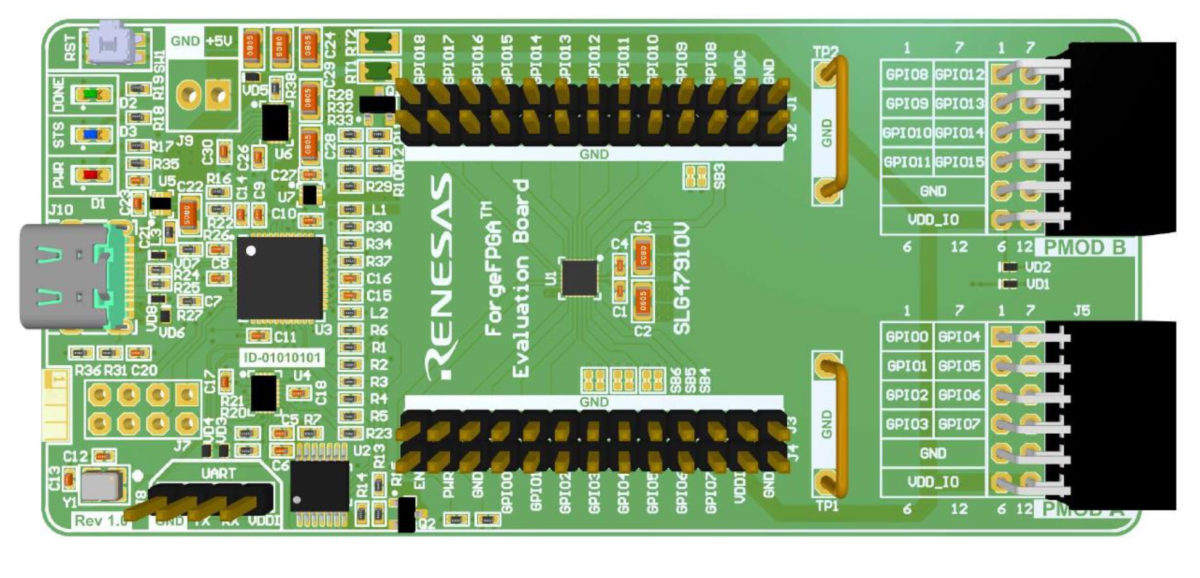

هل ترى الشريحة في وسط هذه الصورة التالية؟ إنها ForgeFPGA من Renesas في حزمة QFN-24 ، بناءً على EFLX 1K IP ، والتي تقدمها شركة Renesas بسعر أقل من 1 دولار في الحجم. هدفها الاستعداد الحالي الشيكات في أقل من 20uA. أصغر حجمًا ، وتكلفة أقل ، وأبواب مفتوحة طاقة أقل كانت مغلقة سابقًا في FPGAs. تعود نسب ForgeFPGA إلى تقنية Silego ، ثم إلى Dialog Semiconductor ، التي حصلت عليها شركة Renesas في عام 2021.

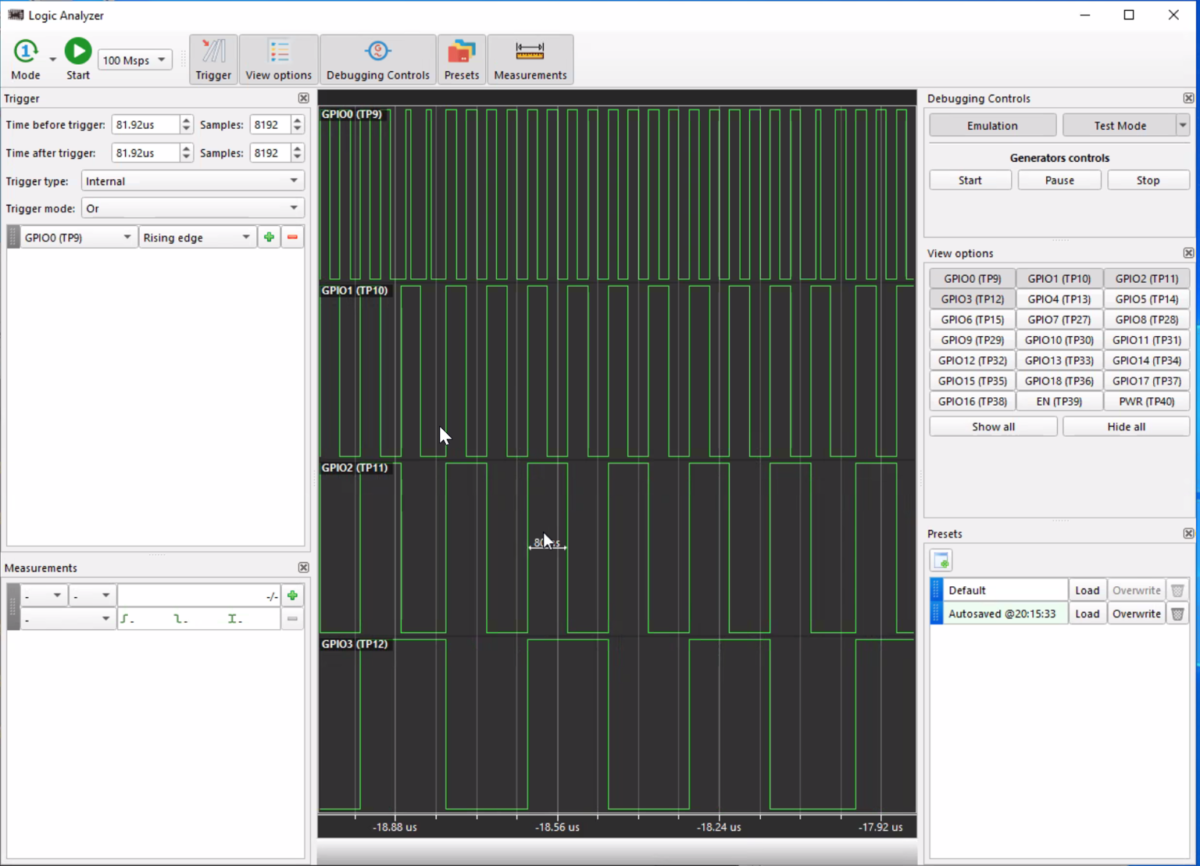

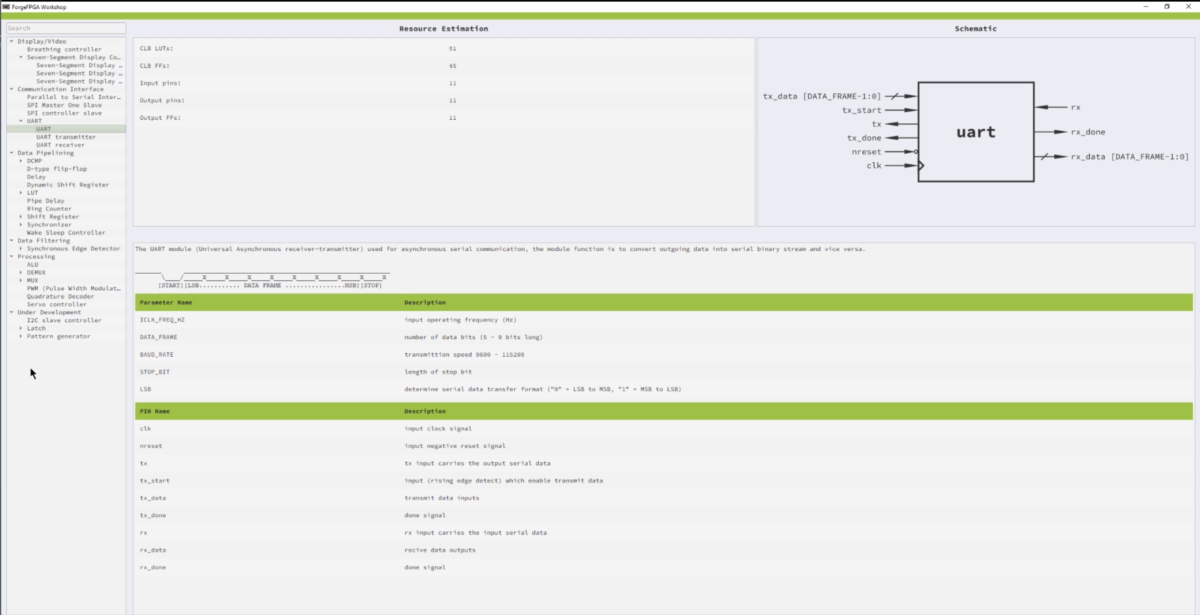

يجلب Renesas بيئة Go Configure IDE ، مما يضع واجهة مستخدم رسومية أعلى مترجم Flex Logix EFLX. وهو يدعم رسم خرائط دبابيس ForgeFPGA ، وتجميع Verilog ، وتوليد تيار بتات ، ويحتوي على محلل منطقي خفيف الوزن.

تحتوي كتل التطبيقات المبنية مسبقًا لـ ForgeFPGA على واحدة مثيرة للاهتمام يشير إليها Geoff Tate من Flex Logix: UART. إن إنشاء UART في المنطق ليس بهذه الصعوبة ، ولكن اتضح أن كل شخص قد تعامل معه بشكل مختلف ، ومن المنطقي أن يكون أكثر من بضع شرائح منفصلة. يعد ForgeFPGA جزءًا من المنطق القابل لإعادة التكوين يمكنه حل هذه المشكلة ، مما يسمح بتنفيذ أحد الأجهزة للتكيف بسرعة مع التكوينات المختلفة.

ForgeFPGA هو مجرد مثال واحد على ما يمكن عمله باستخدام بلاط Flex Logix EFLX 1K eFPGA. يمكن لـ Flex Logix أن يكيّف عنوان IP للعديد من عقد العملية ، وتوفر إمكانية التبليط المزيج والمطابقة قابلية التوسع. إنه يحقق مستويات منخفضة جديدة للمنطق القابل للبرمجة منخفض الطاقة ويسمح لصانعي الرقائق بالتمييز بين الحلول بطرق رائعة. لمزيد من المعلومات ، يرجى زيارة:

اقرأ أيضا:

تتعامل eFPGAs مع خفة الحركة المشفرة لـ SoCs مع PQC

فليكس لوجيكس: أول نظام مدمج يعتمد على الذكاء الاصطناعي في الصناعة يعتمد على تقنية Mini-ITX

شركاء Flex Logix بمعرف داخلي لتأمين منصة eFPGA

شارك هذا المنشور عبر:

- محتوى مدعوم من تحسين محركات البحث وتوزيع العلاقات العامة. تضخيم اليوم.

- بلاتوبلوكشين. Web3 Metaverse Intelligence. تضخيم المعرفة. الوصول هنا.

- المصدر https://semiwiki.com/efpga/flex-logix/325926-efpga-goes-back-to-basics-for-low-power-programmable-logic/

- :يكون

- $ UP

- 1

- 2021

- 3d

- a

- القدرة

- من نحن

- حوله

- يحقق

- المكتسبة

- الاستحواذ

- نشط

- تكيف

- متقدم

- بعد

- العدواني

- AI

- الكل

- السماح

- يسمح

- و

- آخر

- تطبيق

- At

- الى الخلف

- حاجز

- على أساس

- الأساسيات

- BE

- ما بين

- كبير

- أكبر

- حظر

- Blocks

- مجلس

- اقترضت

- يجلب

- جلبت

- by

- تسمى

- CAN

- قادر على

- مركز

- تحدى

- تدقيق

- الشيكات

- رقاقة

- شيبس

- الخيارات

- ساعة حائط

- صندوق توظيف برأس مال محدود

- مجمع

- الاعداد

- منظمة

- التكلفة

- التكاليف

- استطاع

- زوجان

- تغطية

- خلق

- حالياًّ

- على

- دورات

- التعارف

- عميق

- تصميم

- تصميم

- المصممين

- المتقدمة

- جهاز

- الأجهزة

- حوار

- تميز

- صعبة

- رقمي

- الصلصة

- الأبواب

- كل

- رئيس التحرير

- تمكين

- كاف

- دخول

- البيئة

- عصر

- خطأ

- تقييم

- كل شخص

- مثال

- غريب

- ذو تكلفة باهظة

- اكتشف

- تعرض

- للعائلات

- FAST

- أسرع

- المميزات

- الأول

- مرونة

- في حالة

- FPGA

- تبدأ من

- توليد

- يعطي

- Go

- يذهب

- مقبض

- معالجة

- أجهزة التبخير

- يملك

- مرتفع

- أعلى

- عقد

- HTTPS

- ID

- صورة

- التنفيذ

- تحسين

- in

- بما فيه

- الصناعة

- غير مكلف

- info

- بدلًا من ذلك

- المتكاملة

- وكتابة مواضيع مثيرة للاهتمام

- السطح البيني

- واجهات

- جوهري

- المُقدّمة

- المستثمرين

- IP

- IT

- انها

- JPG

- واحد فقط

- مختبرات

- المكتبة

- خفيفة الوزن

- مثل

- الكثير

- منخفض

- تخفيض

- أدنى مستوى

- الماكرو

- وحدات الماكرو

- صنع

- صناع

- إدارة

- الشركات المصنعة

- رسم الخرائط

- تجارة

- هائل

- ناضج

- ماكس العرض

- مانع

- موضة

- وسائط

- مال

- الأكثر من ذلك

- أكثر

- جديد

- التالي

- العقد

- of

- الوهب

- عروض

- عروض

- on

- ONE

- جاكيت

- أخرى

- أخرى

- صفقة

- التعبئة والتغليف

- جزء

- شركاء

- أجزاء

- دبابيس

- بلاتفورم

- أفلاطون

- الذكاء افلاطون البيانات

- أفلاطون داتا

- من فضلك

- نقاط

- منشور

- قوة

- قدم

- الهدايا

- سابقا

- السعر

- المحتمل

- المشكلة

- عملية المعالجة

- معالجة

- بارز

- وضع

- بسرعة

- سباق

- رامات

- سريع

- عرض

- إعادة تصميم

- تخفيض

- لافت للنظر

- إزالة

- استبقاء

- المخاطرة

- طريق

- الطرق

- الأدوار

- التدرجية

- تأمين

- أشباه الموصلات

- طقم

- التحولات

- سيجنل

- السيليكون

- المقاس

- النوم

- صغير

- الأصغر

- ناعم

- الحلول

- حل

- بعض

- الولايه او المحافظه

- تبسيط

- الدعم

- اكتساح

- أخذ

- مع الأخذ

- الهدف

- تكنولوجيا

- تجربه بالعربي

- الاختبار

- أن

- •

- من مشاركة

- تشبه

- مرات

- إلى

- نغمة

- تيشرت

- تقليدي

- TSMC

- مع

- مستخدم

- واجهة المستخدم

- مختلف

- بواسطة

- قم بزيارتنا

- حجم

- انتظر

- طرق

- ابحث عن

- التي

- مع

- بدون

- للعمل

- سوف

- زفيرنت