لقد قامت Chiplets بتبسيط منطقة واحدة من التصميم ولكنها فتحت صندوق باندورا على جبهة أخرى. تعقيد المحاكاة لكل منها شريحة أقل ولكن الآن أصبح الاتصال البيني من شريحة إلى شريحة معقدة. يقوم الأشخاص بتجربة بروتوكولات ربط مختلفة، وأشكال مختلفة من UCIe، وتعديل إعدادات UCIe، وسرعات الواجهة، وعدد الطبقات المادية، وما إلى ذلك. أضف الآن المعايير القديمة مثل AXI والبروتوكولات الجديدة مثل PICe6.0 وتماسك ذاكرة التخزين المؤقت إلى هذا المزيج.

وبشكل عام، يؤدي هذا إلى إنشاء مجموعة جديدة تمامًا من التجارب. واحد لن تعمل معه المحاكاة التقليدية ونمذجة RTL. تحتاج أولاً إلى بذل جهد في المفاضلة بين التصميم المعماري، وليس فقط في اختيار المكونات. وهذا يعني أنه سيتعين عليك إجراء تحليل حركة المرور وتقسيم التطبيقات وحجم النظام وتأثير الأنواع المختلفة من الطبقة المادية. أيضًا، اعتمادًا على التطبيق، سيكون المعيار مختلفًا جدًا.

مواصفات UCIe جديدة ولا توجد معايير واضحة. كما توفر مواصفات UCIe إرشادات حول زمن الوصول والطاقة فقط. كلاهما متطلبات صارمة. وهذا يعني أن دراسة منطقة أداء الطاقة أمر لا مفر منه. نظرًا لأن لديك تحويل بروتوكول-بروتوكول-بروتوكول مثل PCIe 6.0 إلى UCIe إلى AXI، فإن إعداد النمذجة معقد.

أحد الحلول هو النظر إلى نمذجة النظام باستخدام VisualSim تبدأ من بإحراز تصميم. لقد أطلقوا مؤخرًا نموذج IP على مستوى نظام UCIe وسيعرضون عددًا من حالات الاستخدام للتوصيل البيني في قمة تشيبليت. لتوجيه المصممين، قاموا بنشر دليل يحتوي على الكثير من حالات الاستخدام، ونتائج أداء الطاقة المتوقعة وخيارات التحسين. لديهم عرض تقديمي ورقي ومقصورة في القمة. آمل أن نراكم هناك!

وهذا أيضًا رابط الورقة التي يمكن للناس الحصول عليها: نمذجة أداء نظام حوسبة غير متجانس يعتمد على بنية UCIe Interconnect Architecture

المستخلص:

تتكون تصميمات الرقائق المعقدة اليوم في العقد المتقدمة عمومًا من قوالب متعددة (أو شرائح صغيرة). يسمح هذا النهج باستخدام قوالب من شركات مصنعة أو عمليات مختلفة، بالإضافة إلى IP القابل لإعادة الاستخدام. يحتاج المصممون إلى نموذج على مستوى النظام لتقييم التطبيقات المختلفة لمثل هذه المواقف المعقدة.

يتكون النظام النموذجي من شريحة إدخال/إخراج، وشريحة أساسية منخفضة الطاقة، وشريحة أساسية عالية الأداء، وشريحة صوت وفيديو، وشريحة تمثيلية، مترابطة باستخدام معيار Universal Chiplet Interconnect Express (UCIe).

نظر فريقنا في العديد من السيناريوهات والتكوينات بما في ذلك الحزم المتقدمة والقياسية، وملفات تعريف حركة المرور المتنوعة والموارد، ومؤقت لتوسيع نطاق الوصول وتقييم الأحداث عند انتهاء المهلة. ساعدنا تحديد نقاط القوة والضعف في التوصيل البيني UCIe لتطبيقات المهام في الحصول على التكوين الأمثل لكل نظام فرعي لتلبية متطلبات الأداء والطاقة والمتطلبات الوظيفية.

نبذة عن شركة ميرابيليس ديزاين إنك.

ميرابيليس ديزاين هي شركة برمجيات في وادي السيليكون، تقدم حلولاً برمجية وتدريبية لتحديد المخاطر في مواصفات المنتج والقضاء عليها، والتنبؤ بدقة بالموارد البشرية والوقت اللازمة لتطوير المنتج، وتحسين التواصل بين الهندسة المتنوعة.

فرق.

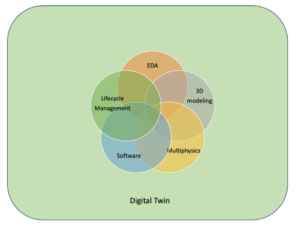

يجمع VisualSim Architect بين الملكية الفكرية والنمذجة على مستوى النظام والمحاكاة وتحليل البيئة وقوالب التطبيقات لتحسين بناء النماذج والمحاكاة والتحليل والتحقق من RTL بشكل كبير. تتيح البيئة للمصممين إمكانية الالتقاء بسرعة لتصميم يلبي مجموعة متنوعة من متطلبات الوقت والطاقة المترابطة. يتم استخدامه في وقت مبكر جدًا من عملية التصميم بالتوازي مع (وكمساعدة) للمواصفات المكتوبة وقبل التنفيذ (على سبيل المثال، RTL أو رمز البرنامج أو التخطيطي) للمنتج.

اقرأ أيضا:

ندوة عبر الإنترنت: كيفية تحقيق قياس دقيق للطاقة بنسبة 95%+ أثناء استكشاف الهندسة المعمارية

دورات التصميم المبني على النماذج للطلاب

شارك هذا المنشور عبر:

- محتوى مدعوم من تحسين محركات البحث وتوزيع العلاقات العامة. تضخيم اليوم.

- PlatoData.Network Vertical Generative Ai. تمكين نفسك. الوصول هنا.

- أفلاطونايستريم. ذكاء Web3. تضخيم المعرفة. الوصول هنا.

- أفلاطون كربون، كلينتك ، الطاقة، بيئة، شمسي، إدارة المخلفات. الوصول هنا.

- أفلاطون هيلث. التكنولوجيا الحيوية وذكاء التجارب السريرية. الوصول هنا.

- المصدر https://semiwiki.com/ip/mirabilis-design-ip/341339-chiplets-open-pandoras-box/

- :لديها

- :يكون

- :ليس

- a

- دقيق

- بدقة

- التأهيل

- تضيف

- متقدم

- مساعدة

- يسمح

- على طول

- أيضا

- an

- تحليل

- و

- آخر

- تطبيق

- التطبيقات

- نهج

- هندسة معمارية

- هي

- المنطقة

- AS

- At

- على أساس

- BE

- أصبح

- قبل

- مؤشر

- المعايير

- ما بين

- على حد سواء

- صندوق

- لكن

- مخبأ

- CAN

- يستطيع الحصول على

- الحالات

- رقاقة

- واضح

- الكود

- يجمع بين

- Communication

- حول الشركة

- تماما

- مجمع

- تعقيد

- مكونات

- الحوسبة

- إدارة

- الاعداد

- نظرت

- يتكون

- إنشاء

- CONVERGES

- تحويل

- جوهر

- دورات

- يخلق

- التظاهر

- اعتمادا

- تصميم

- عملية التصميم

- المصممين

- تصاميم

- تطوير

- مختلف

- عدة

- أثناء

- كل

- في وقت مبكر

- جهد

- القضاء

- محاكاة

- تمكن

- البيئة

- تقييم

- أحداث

- مثال

- متوقع

- تجارب

- تجارب

- التعبير

- مد

- الاسم الأول

- في حالة

- تبدأ من

- جبهة

- وظيفي

- على العموم

- دولار فقط واحصل على خصم XNUMX% على جميع

- شراء مراجعات جوجل

- توجيه

- توجيه

- أجهزة التبخير

- يملك

- ساعد

- هنا

- أداء عالي

- أمل

- كيفية

- كيفية

- HTTPS

- الانسان

- i

- تحديد

- تحديد

- التأثير

- التنفيذ

- تطبيقات

- تحسن

- in

- بما فيه

- فكري

- الملكية الفكرية

- مترابطة

- السطح البيني

- IP

- IT

- JPG

- م

- كمون

- أطلقت

- طبقة

- طبقات

- إرث

- مستوى

- مثل

- LINK

- بحث

- الكثير

- منخفض

- خفض

- الشركات المصنعة

- ماكس العرض

- تعني

- يعني

- قياس

- تعرف علي

- يجتمع

- الرسالة

- مزيج

- نموذج

- تصميم

- تصميم

- متعدد

- حاجة

- جديد

- لا

- العقد

- الآن

- عدد

- تحصل

- of

- on

- ONE

- فقط

- جاكيت

- افتتح

- الأمثل

- التحسين

- مزيد من الخيارات

- or

- حزم

- ورق

- موازية

- أداء

- مادي

- أفلاطون

- الذكاء افلاطون البيانات

- أفلاطون داتا

- منشور

- قوة

- توقع

- <font style="vertical-align: inherit;"> كمادة تطعيم في تجديد عيوب محيط بالذورة (الحنك) الكبيرة:</font>

- عملية المعالجة

- العمليات

- المنتج

- ملامح

- الملكية

- البروتوكولات

- ويوفر

- توفير

- نشرت

- بسرعة

- الوصول

- عرض

- مؤخرا

- مطلوب

- المتطلبات الأساسية

- الموارد

- النتائج

- قابلة لإعادة الاستخدام

- المخاطرة

- سيناريوهات

- انظر تعريف

- اختيار

- طقم

- إعدادات

- الإعداد

- عدة

- بشكل ملحوظ

- السيليكون

- وادي السيليكون

- مبسط

- محاكاة

- حالات

- So

- تطبيقات الكمبيوتر

- حل

- الحلول

- مواصفة

- بسرعة

- أنفق

- معيار

- المعايير

- نقاط القوة

- صارم

- دراسة

- هذه

- قمة

- نظام

- فريق

- النماذج

- أن

- •

- هناك.

- هم

- الوقت

- إلى

- تقليدي

- حركة المرور

- قادة الإيمان

- أنواع

- عالمي

- us

- تستخدم

- مستعمل

- استخدام

- Valley

- الاختلافات

- التحقق

- جدا

- بواسطة

- نقاط الضعف

- حسن

- التي

- سوف

- مع

- للعمل

- مكتوب

- لصحتك!

- زفيرنت